Устройство для записи информации в магнитные оперативные блоки памяти

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

< 1781972

Союз Советск их

Социалистических

Респубиии (6l ) Дополнительное к авт. саид-ву (22) Заявлено 02.01.79 (21) 2704948/18-24 с присоединением заявки М (23) Приоритет (5! )М. Кд. 11 С 7/00 тооударотаоииый коиитат

СССР по делан изобретений и открытий (З) УДК681,327..66(088.8)

Онубликовано23.11.80. Бюллетень М43

Дата опубликования описания 23,11.80

I (72) Авторы изобретен кя

М. И. Фомин и Э. П. Твепенев

Ъ у

1 т, с

1. г . „,t (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ЗАПИСИ ИНФОРМАЦИИ В МАГНИТНЫЕ

ОПЕРАТИВНЫЕ БЛСЖИ ПАМЯТИ

Изобретение относится к вычислительной технике и предназначено дпя использования в магнитных оперативных запоминающих устройствах (ОЗУ) ЭВМ.

Известно устройство дпя записи информации в магнитные оперативные блоки памяти, в котором нспопьзуется бапансная схема вкпючения формирователей тока запрета и усипнтепей считывания дпя уменьшения помех от тока запрета.

При таком построении обмоток счи!

О ,тывание-запрет" необходимо использовать на каждую секцию обмотки один формирователь тока запрета, рассчитанный as psбочий ток перемагничнвания ферритовых

s сердечников, и один усилитель считывания "форм "ин 13.

Выпускаемые в настоящее время интеграпьные формироватепн: тока рассчитаны на половину рабочего тока перемагни- „О .чнвания ферритовых сердечников. Таким образом, дпя создания секционированной обмотки "считывание-запрет необходимо применение четырех интегральных форми2 роватепей и двух усипитепей считывания информации.

Наиболее бпизкое техническое решение к предлагаемому — устройство дпя записи информации в магнитные оперативные бпоки памяти, которое содержит усилитель считывания, формирователь тока и две секции обмотки считывание-запрет (2 .

Однако в известном устройстве схема вкпючения секционированной обмотки "считывание-запрет является работоспособной только в том случае, когда вопновое сопротивление 2. секций имеет эначитепьную величину.

При увепичении напряжения питания формирователя тока запрета происходит увеличение потребляемой мощности от источника питания, дпя снижения которой необходимо уменьшить величину волнового сопротивления обмотки K но в этом спучае начинает сказываться шунтирующее воздействие одной секции на другую, что приводит к оспабпению амплитуды считываемого сигнала.

3 781 972, 4

lIemü изобретения — уменьшение потреб- Шунтирование входов усилителей устраляемой мощности и упрощение устройства - несется эа счет обратного включения в цепь для записи информации в магнитные orre- диодов 5, 6 для индуцирования сигнала, а ративные блоки памяти. общий путь тока осуществляется за счет

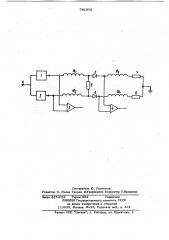

Поставленная цель достигается тем, g прямого включения в цепь разрядной обмот что в устройстве, содержащем секциони- ки указанных диодов. рованную разрядную обмбтку, формирова- В предлагаемом устройстве за счет истели разрядного тока, усилители считыва- ключения щунтирую цего влияния секций ния и разделительные елементыу вйпол- удается увеличить амплитуду считываемоненные на диодах, первый формирователь q© го сигнала с ферритовых сердечников, поразрядного тока соединен с выводом пер- является возможность работы с обмотками вой. секции разрядной обмотки, другой с небольшими значениями волновых сопровывод которой соединен с первым диодом, тивлений (g, ) и, как следствие, снижаетвторой формирователь разрядного тока ся потребляемая мощность от источника coerrrrrrerr с выводом второй секций разряд- у питания. Количество формирователей тока ной обмотки, другой вывод которой сое- запрета сокращается в два раза. динен со вторым диодом, одноимейные электродй первого и второго дйодов соединены с выводами третьей и четвертой Ф о р м у л а и э о б р е т е н и я секций разрядной обмотки, другие выводы .® которых подключены к шине нулевого по Устройство для записи информации в тенциала, первые дифференциальные rrxorrbr магнитные оперативные блоки памяти,соусилителей считывания соединены с выво- держащее секционированную разрядную обдами первой и третьей секций Разрядной мотку, формирователи разрядного тока, обмотки, а вторые диФференциальные в""" д усилители считывания и разделительные

1 дь: усилителей считывания - с выводами . элементы, выполненные на диодах, о твторой и четвертой секций Ранкой обмотки л и ч а ю щ е е с я тем, что, с целью

На чертеже изображена принципиальная уменьшения потребляемой мощности и упсхема предлагаемого устройства. Рощения устройства, первый формироваустройство для записи информации в тель разрядного тока соединен с выводом магнитные оперативные блоки паМяти,со- первой секции разрядной обмотки, другой держит формирователи 1 и 2 Разрядного . вывод которой соединен с первым диодом, тока, усилители 3 и 4 считывания,"диоды юй формирователь Разрядного тока

5, 6, токоэадающие резисторы 7, 8 Pe- соединен с выводом второй секции разрядзистор . 9 и секционированную РаэР днУю ной обмотки, другой вывод которой соедиобмотку состоящую иэ четырех секций;. нен со вторым диодом, одноименные елек10 -104 Выход усилителей.3 и 4 считы- труды первого и второго диодов соединевания и является выходом устройства „c выводами третьей и четвертой секУстрой во Раб тает слеуим обра- ции paepQHoN обмотки. дру ие выводы зом. Ток запрета от формирователей 1 и 4д.- - Рых йодключены к шине нулевого потен2 проходит через секции разрядной обмот и л первые дифференциальные входы ки 10 и 10, диоды 5, 6 и секции Раз» terreó считывания соединены с выворядной обмотки 10 и 104 . Величина то-: дами первой и третьей секцйй разрядной ка задается резисторами 7 и 8. Tm ea- „бмо и,. а В рые дифференциальные вхонрета создает синфазную помеху На вхо- gg rr усилителей с.:читывания - с выводами дах дифференпиальных усилителей 3, 4 и e ó и четвертой секций данной обмотки. компенсируется ими.

Индуцнрованный сигнал tJ может возникнуть в одной из четырех секций разряд- -,Источники информации, йой обмотки. При ййдупировайий сйгйала " принятЫе" во внимание при экспертизе в секциях 10 или 102 сигнал поступает

М

1. Шигин А. Г., Дерюгин A.. A. Бифро2 ю У на вход усилителей 3 через резистор 9. вые вычислительные машины, Энергия, При индуцировании сигнала в секциях 10р 1976, с. 122. или 10, сигнал поступает на вход усиля- 2. Патент США l4 3550445, теля 4 через резисторы 7 и 8. кл. 340-174, 1970 (прототип)., 781972

Составитель Ю. Розенталь

Редактор О. Малец Техред E.Ãàâðèïåøêî Корректор Г.Назарова.

Заказ 8154/63 Тираж 662 Подписное . ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4