Ждущий мультивибратор

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

Союз Советских

Соцнапнстнческнх

Республик н>782134

К АВТОРСКОМУ СВИ ЕТЕЛЬСТВУ (б1) Дополнительное к авт. свид-ву (22) Заявлено 26.12.78 (21) 2702713/26-21 с присоединением заявки ¹ (23) Приоритет

Опубликовано 23,11,80, Бюллетень ¹ 43

Дата опубликования описания 251180 (51)М К 3

Н ОЗ.К 3/281

Государственный комитет

СССР по делам изобретений и открытий (53) УДК 621. 373. .141(088 ° 8) (72) Авторы изобретения

В. Н. Семенов, H. П. Булаткин и Е. А. Жмуров (71) Заявитель (54) ждУщий мультивиВРАтор

f ,Изобретение относится к импулЬсной технике и может быть использова. но в радиотехнических устройствах и системах автоматики.

В настоящее время известно большое количество различных ждущих уст;ройств формирования импульсов, выполненных на транзисторной элементной базе, к которым относятся ждущие мультивибракоры, одновибраторы, жду.. не блокинг-генераторы и т.д.

В то же время различных ждущих устройств формирования импульсов, по» строенных на интегральных микросхемах (ИМС), для решения многообразных технических задач имеется сравнительно небольшое количество, что характерно для начального периода освоения новой элементной базы. Каждое новое поколение элементной базы, по сравнению с предыдущим, имеет более высокие технические характеристики и обладает только им присущими новыми специфическими свойствами.

Поэтому для построения ждущих релаксаторов на ИМС требуются новые технические решения.

Известен ждущий мультивибратор, выполненный на двух логических элементах HE-И, который имеет большую стабильность длительности выходного сигнала по сравнению с классической схемой мультнвибратора 1) . В отличие от классической схемы в предложенном мультивибраторе времязадающая ячейка состоит из конденсатора, включенного между выходом мультивибратора и вторым входом входйого логи10 ческого элемента, а также из последовательно соединенных полупроводникового диода и резистора, которые включены между выходом и вторым входом этого элемента (анод полупровод15 никового диода подключен ко входу).

Укаэанное включение времязадающей ячейки дает возможность производить возврат мультивнбратора в исходное состояние на линейной части экспо20 нента, в то время как в классической схеме возврат происходит на пологом участке экспойенциально изменяющегося напряжения, снимаемого с времязадающей ячейки. Этот ждущий муль25 тнвибратор имеет высокую стабильность длительности выходного сигнала в случае, когда период запускающих импульсов значительно больше длитель- ности формируемого выходного импуль30 са

782134

40 ряжен через выход логического элемен, та 2 и резистор 5.

Поступающий на вход ждущего мультивибратора запускающий импульс отрицательной полярности (логический

45 ."0") воздействует одновременно на логический элемент 1 и на триггер 3.

На выходе логического элемента 1 на время длительности запускающего импульса устанавливается логическая

50 "1". Триггер 3 переключается в единичное состояние, в результате на обоих входах логических элементов, 2 присутствует разрешающий потенциал (логическая "1") и начинается быстрый процесс заряда конденсатора 7 интегрирующей цепи через закрытое плечо триггера 3 и сопротивление резистора. Так как конденсатор 7 не может зарядиться мгновенно, а время заряда его пропорционально величи60 не емкости конденсатора 7 и сопротивлению резистора 6, то установление логической "1" на входах логического элемента 2 происходит с некоторой задержкой, равной по величине постоян1

65 ной Времени заряда интегрирующей пепи

Однако, если на вход ждущего мультивибратора поступают запускающие импульсы, период которых меньше длительности формируемого сигнала, то часть из них будет совпадать по времени с процессом восстановления устройства, поэтому конденсатор времязадающей цепи не успевает разряжаться до нуля, В этом случае на выходе устройства формируется укороченный по длительности импульс или вообще его не будет, так как схема генератора может не сработать.

Известен ждущий мультивибратор, содержащий .два логических элемента

И-НЕ, RS-триггер и времязадающую

RC-цепь 21

Данный мультивибратор имеет недостаточную стабильность длительности выходных импульсов. Когда на вход устройства поступают запускающие импульсы с периодом повторения меньше длительности его выходного сигнала, то часть импульсов будет по времени совпадать с процессом его восстановления, в течение которого отсутствует защита устройства.

Цель изобретения — стабилизация длительности выходных импульсов и расширение функциональных возможностей мультивибратора.

Указанная. цель достигается тем, что в ждущий мультивибратор, содер-. жащий два логических элемента И-НЕ, RS-триггер и времязадающую RC-цепь, включенную между входом первого логического элемента И-НЕ, второй вход которого подключен к входной шине и выходом второго логического элемента

НЕ-ИЛИ, 5-вход RS-триггера соединен с входной шиной, à R-вход соединен с выходом первого логического элемента И-НЕ, введены интегрирующая КСцепь и диод, причем выход RS-триггера подключен к одной общей точке параллельно включенных диода и резистора интегрирующей RC-цепи, вторая общая точка которых подключена ко входу второго логического элемента И-НЕ и к одной обкладке конденсатора интегрирующей RC-цепи, вторая обкладка которого соединена с общей шиной.

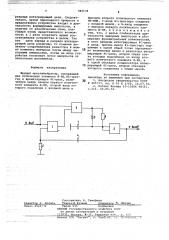

На чертеже представлена принципиальная электрическая схема устройства.

Устройство содержит два логических элемента И-HE 1 и 2, триггер 3, времязадающую RC-цепь, состоящую из конденсатора 4 и резистора 5. Кроме того, устройство включает в себя интегрирующую цепь, в которую входит резистор б и конденсатор 7 и диодный элемент 8 разряда.

Входом устройства является один из входов логического элемента 1, соединенный с входом установки триггера

3 в единичное состояние, вход ycTaHDBки триггера 3 в нулевое состояние подключен к выходу логического элемента

1. Другой вход логического элемента

1 соединен через конденсатор 4 времязадающей цепи с выходом второго логического элемента 2, являющегося выходом устройства, который также связан с одним из выводов резистора 5 времязадающей цепи, а второй вывод его соединен с общей шиной устройства.

Выход триггера 3 подключен к одному выводу резистора б интегрирующей цепи, второй вывод которого связан с входом логического элемента 2 и с одним из выводов конденсатора 7 интегрирующей цепи, второй вывод конденсатора 7 соединен с общей шиной устройства. Диодный элемент 8 разряда подключен параллельно резистору б.

Ждущий мультивибратор работает следующим образом.

В исходном состоянии на входах логического элемента 1 поддерживаются потенциалы, соответствующие уровню логической единицы. На выходе логического элемента 1 устанавливается "0". Триггер З.устанавливается в нулевое состояние, соответственно на входе логического элемента И-НЕ 2 присутствует запрещающий потенциал

"0", что исключает срабатывание ждущего мультивибратора от высокочастотных помех, амплитуда которых не достигает порогового уровня логических элементов. Так как триггер 3 переключается в нулевое состояние, то конденсатор 7 разряжен через прямое сопротивление диодного элемента 8 и открытое плечо триггера 3 потенциал т которого равен нулю.

На выходе логического элемента 2 будет высокий потенциал, соответствующий уровню логической "1". Кон-; денсатор 4 времязадающей RC-цепи за782134 логического элемента 2, этим исключается .запуск ждущего мультивибратора от высокочастотных помех, амплитуда которых не достигает порогового уровня логических элементов.

Помехоустойчивость ждущего мультивибратора определяется помехоустойчивостью триггера 3, поэтому замена " триггера, выполненного на логических элементах И-НЕ, на триггер RCтипа, имеющего более высокие уровни срабатывания, позволяет увеличить помехоустойчивость устройства в целом.

В течение времени разряда времязадающей RC-цепи формируется длиS тельность выходного импульса, на это время на вход логического элемента

1 подается отрицательный потенциал.

Поэтому приходящие запускающие импульсы отрицательной полярности, когда их период меньше длительности выходного сигнала, то определенное число из которых совпадает по времени с процессом формирования выходного импульса, не могут нарушить работу ждущего мультивибратора.

Формирование паузы между импульсами и переднего фронта выходного сит .нала производится с задержкой, равной постоянной времени заряда интегрирующей цепи, что необходимо для полного установления переходных процессов, связанных с зарядом времязадающей цепи. Формирование заднего фронта выходного сигнала и начала паузы производится с задержкой, равной пос; тоянной времени разряда интегрирующей цепи для того, чтобы закончился переходный процесс в схеме устройства связанный с разрядом времязадающей цепи ° При поступлении на вход ждущего мультивибратора запускающих импуль- сов с периодом следования меньшим, чем длительность выходного сигнала, часть из этих импульсов совпадает по времени с процессом формирования переднего и заднего фронтов выходного импульса. Так как заряд и разряд времязадающего конденсатора производится по времени больше на величину постоян« ных времени заряда и разряда интегрирующей цепи до полного окончания переходного процесса в схеме устройства, поэтому исключается подзаряд хронирующего конденсатора 4 запускающими импульсами, потому что области зон переходных процессов при формировании выходного импульса защищены. Таким образом, на выходе ждущего мультивибратора формируются стабильные по длительности импульсы, длительность которых не зависит от потока запускающих импульсов. Длительность выходных импульсов >хдущего мультивибратора определяется не только параметрами постоянной времени времязадающей цепи, а также и ве личиной постоянных времени заряда н

Таким образом, после заряда конденсатора 4 времязадающей цепи, дается еще дополнительное время на окончание переходных процессов в схеме устройства, которое определяется величиной постоянной времени заряда интегрирующей цепи. Когда положительный потенциал на входе логического элемента 2 достигает порогового значения, тогда элемент открывается и на его выходе устанавливается нулевой потенциал.

Заряженный в исходном состоянии конденсатор 4 времязадающей цепи начинает разряжаться через резистор 5 и открытый элемент 2. За время разряда конденсатора 4 производится формирование длительности выходного импульса ждущего мультивибратора и на это время на входе логического элемента 1, связанного с времязадающей ячейкой, поддерживается отрицательный потенциал. По мере разряда конденса- щ тора 4 разрядный ток, протекающий через резистор 5, начинает уменьшаться, а потенциал резистора 5 повышается за счет вытекающего тока из элемента 1. По мере возрастания положительного потенциала на резисторе 5, т.е. на входе логического элемента 1, и когда он достигает порогового значения, ждущий мультивибратор скачком возвращается в исходное состояние. На выходе логического элемента1 устанавливается "0", триггер 3 перебрасывается в нулевое состояние., Однако нулевое состояние с выхода триггера 3 передается на вход логического элемента 2 с небольшой задержкой порядка 3-5 десятых микросекунды, равной величине разряда постоянной времени интегрирующей цепи, так как конденсатор 7 был заряжен ранее положительным потенциалом от. 40 источника питания микросхем. Разряд конденсатора 7 производится через прямое сЬпротивление диодного элемента 8 и открытое плечо триггера 3, так как величина сопротивления ре- 4> эистора б на много больше, чем прямое сопротивление диодного элемента

8. Следовательно, после разряда конденсатора 4 времязадающей цепи, дается еще дополнительное время на окончание переходных процессов в схеме устройства, которое определяется величиной постоянной времени разряда интегрирующей цепи. По мере разряда конденсатора 7 потенциал резистора

6 на входе логического элемента 2 понижается, когда он достигает порогового значения, тогда логический элемент 2 изменяет свое состояние на выходе скачком с "0" на "1". Снова начинается процесс заряда конденса- ц) тора 4 через логический элемент 2 и резистор 5. Так осуществляется генерация прямоугольных импульсов жду- щим мультивибратором. При установке запрещающего потенциала "0" на входе д

782134

Формула изобретения

Составитель В. Тимофеев

Тех е М. К зыка Ко екто М. немчик

Редакто A. Мотыль

Заказ 8 66/72

Тираж 995 Подписное

ЭНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035 москва х-35 Раув3ская наа, д, 4 5

Филиал ППП Патент, г. Ужгб. oh," .,-., П, 3а.ктн;351, 4 афм3акаР сао31 ь*:. -" вк Р н:. н -« * . 35 ., 3 а1- 3 3: разряда интегрирующей цепи. Следовательно, время переходного процесса в предлагаемом устройстве входит в длительность формируемых импульсов, в отличие от классических схем, благодаря этому представляется возможность в 2 раза сократить время восстановления устройства в целом. Так как цепи заряда и разряда интегрирующей цепи различны, то изменяя величину сопротивления резистора 6 можно изменять интервал паузы между выходными импульсами, когда на вход устройства поступает поток импульсов от нескольких источников.

Ждущий мультивибратор, содержащий два логических элемента Й-НЕ, AS-триггер и времязадающую RC-цепь, включенную между входом первого логического элемента И-НЕ, второй вход которого подключен к входной шине и выходом второго логического элемента

НЕ-ИЛИ, 5-вход RS-триггера соединен с входной шиной, а R-вход соединен с выходом первого логического элемента И-НЕ, отличающийся тем, что, с целью стабилизации длительности выходных импульсов и расширения функциональных возможностей, в него введены интегрирующая RC-цепь и диод, причем выход RS-триггера подключен к одной общей точке параллель10 но включенных диода и резистора интегрирующей RC-цепи, вторая общая точка которых подключена ко входу вто рого логического элемента И-НЕ, и к одной обкладке конденсатора интег15 рирующей RC-цепи, вторая обкладка которого соединена с общей шиной.

Источники информации, принятые во внимание при экспертизе

2О 1. Авторское свидетельство СССР

9 446655771177, кл. Н 03 К 1/00, 14.07.72.

2, Патент Японии 51-15606 98(5), с.111. 10.05.72.