Импульсно-фазовый детектор

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советскнх

Сюцналнстическнх

Реслублнк (1)782142

У .У i. é .У. с.У W

У„ .",.;.,(,::."..1.. „( » " »..:.; . .,— (61) Дополнительное к авт. свид-ву

/ (22) Заявлено 19. 01. 79 (21) 2715982/26-21 (я)М. Кл.3

Н 03 К 9/04 с присоедммеммем заявки № (23) Приоритет

Государственный комитет

СССР по делам изобретений н открытий

Опубликовано 231180. юллетемь ¹ 43 (53) УДК 621. 376..55(088.8) Дата опубликоваммя описания 25.1180 (72) Авторы мзобретеммя

Е. П. Ветлугин, A. И. Лаврушев и T. П. Ярцун

Житомирский филиал Киевского ордена Ленина политехнического института (71) Заявитель УЮ »Е у» (54) ИМПУЛЬСНО-ФАЗОВЫЙ ДЕТЕКТОР

i первый и второй входы блока разности фаз соединены соответственно с первой и второй входной шиной, а первый и второй выход блока разности фаэ соединены соответственно с первым и вторым входом первого триггера, первый выход которого соединен с управляющим входом транзистора блока развертки, а второй выход — с йервым входом блока ИЛИ-НЕ, второй вход которого соединен с первым входом первого триггера, выход блока. ИЛИ-НЕ соединен с первым входом второго триггера, выход которого соединен через первый блок задержки с входом второго блока задержки и с первым входом ключа блока запоминания, второй вход ключа блока запоминания соединен с выходом второго блока задержки и входом третьего блока задержки, выход которого соединен со вторым входом второго триггера и с базой транзистора, коллектор которого соединен с общей шиной, а эмиттер †. через первый резистор к общему выходу коллектора транзистора блока развертки и первой обкладкой интегрирующего конденсатора, вторая обкладка которого соединена с общей шиной, эмиттер транзистора блока развертки соединен! .Изобретение относится к радиотех-, нике и может быть использовано в ин формационно-иэмерительн6й технике и системах импульсно-фазовой автоподстройки частоты. 5

Известен импульсно-фазовый детектор, содержащий параллельно включенные интегрирующий конденсатор и разрядный ключ $1)

Недостатком этого устройства яв- тО ляются импульсные помехи на частоте сравнения.

Известен импульсно-фазовый детектор, содержащий интегрирующий конденсатор, ключ блока развертки, блок за- )5 поминания, ключ и первый триггер, ключ блока запоминания g2)

Недостатком этого устройства является низкая помехозащищенность, цель изобретения — повышение по- 2О мехозащищенности °

Поставленная цель достигается тем, что в импульсно-фазовый детектор, содержащий интегрирующий конденсатор, транзистор блока развертки, блок 25 запоминания, транзистор, первый триггер, ключ блока запоминания, введены блок разности фаэ, блок или-не, второй триггер, три блока задержки, два буферных блока, резисторы, причем Зр " 4УУМВЙ(ФЙИЙЙЫУУДЯ@ЬЯаф Уф У е У-"УУ @ПУУЬ

782142 через второй резистор с питающей шиной, выход интегрирующего конденсатора соединен через первый буферный блок, ключ блока запоминания, блок запоминания, второй буферный блок с выходом детектора.

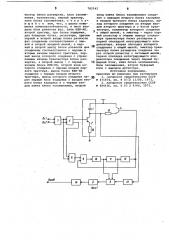

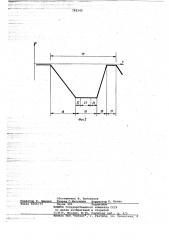

На фиг. I изображена структурная электрическая схема импульсно-фаэово го детектора; на фиг. 2 - диаграмма напряжений.

Импульсно-фазовый детектор содержит интегрирующий конденсатор 1, тран-lt) эистор 2, блок Развертки, блок 3 запоминания, транзистор 4, первый триггер 5, ключ 6 блока запоминания, блок

7 разности фаз, блок 8 ИЛИ-НЕ, второй триггер 9, три блока 10-12 задерж-1 ки, два буферных блока 13 и 14, резисторы 15 и 16.Импульсно-фазовый детектор работает следующим образом.

За исходное состояние принимают момент времени, когда на йервых выходах блока 7 разности фаз и триггерах 5 и 9 присутствуют уровни "лог.0" (фиг.2), а на вторых выходах — уровни "лог. "1" (фиг. 2) и транзисторы

2 и 4 закрыты, на выходе блока 8 уровень "лог. 0" (фиг. 2).

Входные сигналы подаются на блок

7 разности фаз, с выхода которого парофаэный сигнал, длительностью про- () порциональный разности фаз, поступает на входы первого. триггера 5. При изменении сигнала на первом входе триггера 5 с уровня "лог. 0" (фиг.2)

° в уровень "лог. 1" (фиг.2), а на вто- З5 ром входе - c уровня "лог. 1"(фиг.2) в уровень "лог. 0"(фиг.2,), первый триггер 5 перейдет в состояние, когда на первом его выходе будет уровень

"лог. 1" (фиг. 2), а-на втором = уровень "лог. 0"(фиг. 2), при этом тран- 4О эистор 2 блока развертки откроется и начнется заряд интегрирующего конденсатора 1 ° На выходе блока 8 сохранится уровень "лог. 0" (фиг.2). По окончанию, сигнала уровни на входах 45 первого триггера 5 принимают исходное состояние (первый вход — уровень

"лог. 0", второй - уровень "лог.1").

Поскольку на втором выходе первого триггера 5 в этот момент времени еще gp присутствует уровень "лог. 0", то нозникшийГ на втором входе блока 8 уровень "лог. 0" приведет к изменению на его выходе уроння "лог. 0" на уровень "лог. 1", что принедет к сра- >5 батыванию второго триггера 9. Несколько .Раньше первый триггер 5 вернется в исходное состояние и закроет транзистор 2, остановин заряд интегрирующего конденсатора 1. Таким образом, время заряда интегрирующего конденса- 60 тора 1 соответствует длительности приходящего импульса с блока 7 разности фаэ. После окончания заряда.интегрирующего конденсатора 1 начинается время хранения его заряда. i5

Переключение второго триггера 9 вызывает появление на его выходе уровня "лог. 1", который через первый блок 10 задержки поступает на первый вход ключа б блока запрминания и открывает его, осуществляя перезапись с интегрирующего койденсатора 1,выполняющего функцию промежуточного хранения, через входной буферный блок 13 на блок 3 запоминания и через выходной буферный блок 14 на выход устройства. Через время, равное задержке второго блока 11 задержки уровень "лог. 1" поступает на второй управляющий вход ключа запоминающего устройства и закрывает его.

Через время, равное задержке третьего блока 12 задержки уровень "лог.1" поступит на базу транзистОра 4 и откроет его. Начинается сравнительно медленный разряд интегрирующего конденсатора 1 через токоограничинающий резистор 15. Время хранения заряда на интегрирующем конденсаторе заканчивается. Одновременно с выхода третьего блока 12 задержки сигнал с .уровнем "лог. "." поступает.на второй вход второго триггера 9 и возвращает его н исходное состояние. Через время, равное сумме задержек блоков 1012 задержки сигнал с выхода второго триггера 9 с уровнем "лог. 0" закрывает транзистор 4. Затем цикл работы повторится.

Таким образом, н импульсно-фазовом детекторе формируется несимметрично-трапециедальная форма развертывающего напряжения, приведенная на фиг. 2; где показано, что за время периода 17 происходит развертка 18, хранение 19, разряд 20, пауза 21 между окончанием разряда и началом развертки,при этом время хранения 19 определяется суммарной задержкой трех блоков 10-12.

Время 22 задержки первого блока

10 задержки должно быть больше времени переходных процессон в блоке развертки при переходе из режима развертки в режим хранения. Время

23 задержки второго блока 11 задержки определяется временем перЪзаписи, которое дОлжно быть больше времени переходных процессов в ключе 6 блока

3 запоминания.Время 24 задержки блока

12 задержки должно быть больше време« ни переходного процесса запирания ключа.

Использование несимметрично-трапецеидальной формы развертывающего напряжения позволяет значительно уменьшить амплитуду выбросов напряжения и время установления переходных процессов развертывающего устройства, особенно при смене режима развертки на разряд.

ФоРмУла изобретения

Импульсно-фазовый детектор, содержащий интегрирующий конденсатор, тран782142 зистор блока развертки, блок запоми- нания, транзистор, первый триггер, ключ блока запоминания, о т л и ч а« ю шийся тем, что, с.целью повышения помехоустойчивости, в него введены блок разности фаз, блок ИДИ-НЕ, второй триггер, три блока задержки, два буферных блока, резисторы, причем первый и второй входы блока разности фаз соединены соответственно с первой и второй входной шиной, а первый и второй выход блока разности фаз 1© соединены соответственно с первым и вторым входом первого триггера, первый выход которого соединен с управляющим входом транзистора блока развертки, а второй выход — c п еeр в ы м, 15 входом блока ИЛИ-НЕ, второй вход которого соединен с первым входом первого триггера, выход блока ИЛИ-НЕ соединен с первым входом второго триггера, выход которого соединен че- ;1О рез первый блок задержки с входом второго блока задержки и с первым входом ключа блока запоминания, второй

1 вход ключа блока запоминания соединен с выходом второго блока задержки и входом третьего блока задержки, выход которого соединен со вторым входом второго триггера и с базой транзистора, коллектор которого соединен с общей шиной, а эмиттер — через первый резистор к общему выводу коллектора транзистора блока развертки и первой обкладкой интегрирующего конденсатора, вторая обкладка которого соединена с общей шиной, эмиттер транзистора блока развертки соединен через второй резистор с питающей шиной, первая обкладка интегрирующего конденсатора соединена через первый буферный блок, ключ блока запоминания, блок запоминания, второй буферный блок с выходом детектора.

Источники информации, принятые .во внимание при экспертизе

1. Авторское свидетельство СССР

В 471654, кл. Н 03 5 13/00, 1973.

2. Авторское свидетельство СССР

9 484б36, кл. Н 03 К 9/04, 1973..782142

Фиаl

Составитель В. Коновалов .Ре акто Е. Шишкин Тех е С.Мигунова Ко екто О. Билак

Заказ 8 66 7

Тираж 99 Подписйое

ВНИИПИ Гооударственного комитета СССР по.делам изобретений и открытий

113035 Москва Ж-35 Ра шская наб. д, 4 5

Филиал ППП, Патент,. r. Ужтород, ул. Проектная, 4