Аналого-цифровой преобразователь

Иллюстрации

Показать всеРеферат

ОПИСА

ИЗОБРЕТЕНИЯ

Союэ Советских

Социалистических

Республик

МБА (ii>782153

К АВТОРСКОМУ СВИДЕТЕЯЬСТВУ (61) Дополнительное к ввт. саид-ву(22) Заявлено 30. 01. 79 (21) 2722167/26-21 (51) Ah.

3 с присоединением заявки йо (23) Приоритет

Н 03 К 13/20

Государственный комитет

СССР

А0 делам изобретений и открытий

Опубликовано 2 311,80, Бюллетень Мо 4 3

Дата опубликования описания 251180. (53) УДК 681. 325 (088.8) (72) Автор изобретения

В. С. Степанов

Калининградское производственно-конструкторское объединение

"Стрела" (71) Заявитель (54) АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ

Изобретение относится к технике преобразования информации и измерительной технике.

Известен аналого-цифровой преобразователь, содержащий генератор, аналоговые ключи для подключения измеряемого и эталонного напряжения, детектор полярности, компаратор нуля, генератор тактовых импульсов, счетчик импуЛьсов, блок памяти, блок индикации и триггер для управления входными аналоговыми ключами $1) .

Недостатком известного устройства является ограниченное быстродействие. Минимальное время преобразования определяется длительностью первого такта интегрирования и при фиксированной частоте генератора импульсов пропорционально количеству разрядов используемого счетчика импульсов.

Цель изобретения — увеличение быстродействия аналого-цифрового преобразователя.

Поставленная цель достигается тем, что в аналого-цифровой преобразователь, содержащий интегратор, ко входу которого через первый аналоговый ключ подключена шина входно-, го сигнала, а выход соединен через ! детектор полярности с управляющим входом второго аналогового ключа и через компаратор нуля с суммирующим входом первого счетчика и с управляющими входами блока памяти и индикатора и выходом генератора тактовых импульсов, при этом выходы разрядов первого счетчика соединены с первыми входами блока .памяти, выходы которого соединены со входами индикатора, а выход управляемого источника эталонного напряжения соединен с первым входом второго аналогового

15 ключа и через инвертор со вторым входом этого ключа, выход которого соединен со вторым входом первого аналогового ключа, введены второй счетчик, элемент И и j-К триггер, входы

20 j и К которого соединены с его инверсным выходом, счетный вход - с выходом старшего разряда первого счетчика и первым входом элемента И, а прямой выход - с управляемым входом

25 первого аналогового ключа и вторым входом элемента И, выход которого соединен с суммирующим входом второго счетчика, выходы разрядов которого соединены со вторыми входами блока

30 памяти.

782153

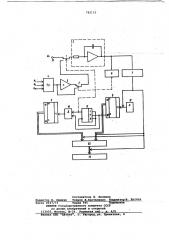

На чертеже представлена структурная схема аналого-цифрового преобразователя.

Аналого-цифровой преобразователь содержит первый и второй .аналоговые ключи 1 и 2, интегратор 3, управля1 емый источник 4 эталонного напряжения, инвертор 5, детектор 6 полярности, компаратор 7 нуля, первый и второй счетчики 8 и 9, элемент ИЛИ 10, j-К триггер 11, генератор 12 тактовых импульсов, блок 13 памяти, инди- lO катор 14, шину входного сигнала 15.

Устройство работает следующим образом.

В исходном состоянии счетчики 8 и 9 импульсов и триггер 11 обнулены, напряжение на выходе интегратора равно нулю. При этом низкий потенциал с прямого выхода триггера запрещает прохождение импульсов через элемент

И 10 на суммирующий вход второго счетчика 9.Измеряемое напряжение по-.

"дается через аналогЬвый ключ 1 на интегратор 3, одновременно начинается заполнение первого счетчика 8 импульсами от генератора 12 тактовых импуль- сов. Задний фронт импульса переполнения первого счетчика 8 опрокинет триг:гер 11 в состояние "1", при этом первый счетчик перейдет в нулевое состояние. Так как входы j и К тригге- 30 ра 11 подключены к его инверсному выходу, который после изменения состояния получил нулевой потенциал, то триггер после опрокидывания не будет реагировать на импульсы, поступаю-З5 щие на его счетный вход, а останется в состоянии,,разрешающем прохождение импульсов со старшего разряда первого счетчика 8 через элемент И на вторую часть счетчика

С момента опрокидывания триггера

11 начинается второй такт интегрирования. Изменение состояния триггера приводит к переключению ключа 1 и подключению ко входу интегратора 3 через ключ 2 эталонного напряжения. Для пре-45 образбванйя входного напряжения произвольной полярности выход управляемого источника 4 эталонного напряжения связан со входом инвертора 5. В зависимости от знака напряжения на 50 выходе интегратора 3 в конце первого такта интегрирования, ключ 2, управляемый детектором 6 полярности, подключает ко входу интегратора 3 либо выход источника 4 напряжения, либо у выход инвертора 5, так, чтобы полярность напряжения на входе интегратора 3 во втором такте интегрирования была противоположной полярности измеряемого напряжения. Окончание второго такта интегрирования определяет- ® ся по прохождению напряжения с вы хода интегратора через нуль. В этот момент сигнал с компаратора 7 нули запрещает прохождение импульсов с генератора 12 тактовых импульсов на . вход первого счетчика 8.

Число, зафиксированное в счетчиkax 8 и 9, пропорционально измеряе мому напряжению, запоминается в блоке 13 памяти и поступает на индикатор 14 для визуального отображения.

В аналого-цифровом преобразователе применен дискретно-управляемый источник 4 эталонного напряжения. В зависимости от управляющего сигнала, поступающего на один из m его входов

К,... К„, можно получить m значений эталонного напряжения Uz,, . . . U T и, еоответственно, значений цифрового кода для каждой измеряемой величины.

Применение дискретно-управляемого источника эталонного напряжения позволяет расширить диапазон цифрового представления измеряемых аналоговых величин и построить, например, измерительную систему для измерения коэффициентов усиления ряда электронных трактов, получая выходные цифровые данные непосредственно в десятичных значениях коэффициентов.

Формула изобретения

Аналого-цифровой преобразователь, содержащий интегратор, ко входу которого через первый аналоговый ключ подключена шина входного сигнала, а выход соединен через детектор полярности с управляющйм входом второго аналогового ключа и через компаратор нуля с суммирующим входом первого счетчика и с управляющими входами блока памяти и индикатора и выходом генератора тактовых импульсов, при этом выходы разрядов первого счетчика соединены с первыми входами блока памяти, выйоды которого соединены со входами индикатора, а выход управляемого источника эталонного напряжения соединен с первым входом второго аналогового ключа и через инвертор со вторым входом этого ключа, выход которого .соединен со вторым входом первого аналогового ключа, о т л и ч аю шийся тем, что, с целью повьыения быстродействия, введены второй .счетчик, элемент И и j-К триггер, входы j и К которого соединены c его инверсным выходом, счетный вход с выходом старшего разряда первого счетчика и первым входом элемента И, а прямой выход с управляемым входом первого аналогового ключа и вторым входом элемента И, выход которого соединен с суммирующим входом второго счетчика, выходы разрядов которого соединены со вторыми входами блока памяти.

Источники информации, принятые во внимание при экспертизе

1. Патент CliIA N 3896431, кл. 340"347, 22.07.75.

782153

Составитель Л. Беляева

Редактов е. шишкин тек вд е.еаотвдевич ео кто В. кутята

Заказ 8167 73 Тиран 995,, Поднисное

ВНИИПИ Государственного комитета СССР по делам изобретениЯ и открытий

113035 Москва Ж-35, Ра кая наб. 4 5 ент, r. Уагород, ул.