Устройство преобразования последовательного двоичного кода в код десятичный

Иллюстрации

Показать всеРеферат

ОП ИСАНКЕ

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистических

Республик

«ii782155

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. сеид-ву 1в 403058 (22) Заявлено 12. 12. 78 (21) 2698126/26-21 (51)М. Кл. с присоединением заявки М (23) Приоритет

Н 03 К 13/24

Государственный комитет

СССР но делам изобретений и открытий

Опубликовано 231180 бюллетень Йо 43

Дата опубликования описания 251180 (53) УДК 681. 325 (088.8) В. A. Максимов, Е. В. Андреев, В. П. Быстров, Ю. A. Душкин, A. В. Кремнев, Б. Н. Кот и Ю. Е. Снетков (72) Авторы изобретения (71) Заявитель (54) УСТРОЙСТВО ПРЕОБРАЗОВАНИЯ ПОСЛЕДОВАТЕЛЬНОГО

ДВОИЧНОГО КОДА В КОД ДЕСЯТИЧНЬ1Й

Изобретение относится к автоматике и электронно-вычислительной технике, технике регистрации и может быть использовано прн построении преобразователей кодов в аппаратуре 3 обработки телеметрической информации.

Известно устройство преобразования последовательного двоичного кода в код десятичный по авт. св.у .10

М 403058, содержащее переключатель, элементы И, элементы ИЛИ, декадный счетчик импульса, генератор фиксированного числа импульсов, при этом первые входы элементов И подключены 1Я к переключателю, вторые через элементы ИЛИ .- к генератору фиксированного числа импульсов, а выходы элементов И соединены с декадньве счетчиicoM импульсов 1 . 20

Недостатком описанного устройства является замедленное время преобразования, обусловленное количеством разрядов в слове и его длительностью, временем счета импульсов декаднык 25 счетчиком импульсов, формируемых по каждому разряду входного последовательного кода..

Цель изобретения — повьыение быст.родействия устройства. ЗО указанная цель достигается тем, что в устройство преобразования последовательного двоичного кода в код десятичный, содержащее переключатель, элементы И, элементы ИЛИ, декадный счетчик импульсов, генератор фиксированного числа импульсов, при этом первые входы элементов И подключены к переключателю, вторые через элементы ИЛИ вЂ” к генератору фиксированного числа импульсов, причем выходы элементов И соединены с декадным счетчиком импульсов, введены регистр, формирователь последовательного кода, последовательно соединенные формирователи импульсов, вход первого из которых соединен с первым выходом переключателя, а выход — со счетным входом декадного счетчика импульсов, выход второго формирователя импульсов — с управляющим входом регистра, третьего с управляющим входом формирователя последовательного кода и входом установки в нуль декадного счетчика импульсов, выходы которого соединены со входами регистра, выходы которого являются выходами параллельного кода и соединены со входами формирователя последовательного кода,,выход которого является выходом по782155

I f ° следовательного кода, и элемент задержки, вход которого соединен с ин формационной шиной, а выход — co входом линии задержки.

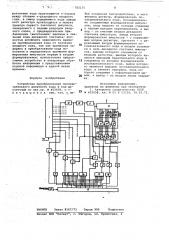

На чертеже изображена структурная электрическая схема устройства.

Устройство содержит переключатель

l„ элементы 2-10 И, элементы 11-16

ИЛИ, линию 17 задержки, счетчик 18 декадных импульсов, формирователи

19-21 импульсов, регистр 22, формирователь 23 последовательного кода, элемент 24 задержки.

Устройство работает следующим образом.

В исходном состоянии содержимое счетчика 18 и регистра 22 соответствует предыдущему значению входного кода (предыдущему значению п разрядного слова двоичного входного кода, преобразованного в десятичный код), находится в нулевом положении и выдает на все элементы 2-10 за« прет. На вход линии 17 задержки через элемент 24 поступают импульсы последовательного двоичного входного кода.

На вход переключателя 1 поступают тактовые входные импульсы (ТИ), синхронно следующие с разрядами по следовательного входнбго кода и переводящие переключатель 1 последовательно в положения 1, 2 ... и, где

n — число двоичных разрядов в преобразуемом входном слове.

После прихода первого тактового импульса, синхронного с первым разрядом входного кода, переключатель 1 перебрасывается с нулевого в первое положение.

С первого выхода переключателя 1 подается напряжение разрешения (первый стробирующий импульс) на элемент 2. На элементы 3-10 выдается запрет. По переднему фронту первого стробирующего импульса на входе формирователя 19 с выходов последовательно соединенной цепочки формирователей 19-21 выдаются сдвинутые относительно друг друга импульсы управления.

С выхода формирователя 19 сформирован.ный импульс поступает на счетный вход счетчика 18, хранящего в се6е предыдущее значение преобразованного входного кода, и изменяет его значение на единицу (увеличивает при работе с монотонно возрастающим, или умейьшает при работе с монотонно убывающим входным кодом).

При этом значение счетчика 18 принимает значение эквивалентное значению "входного кода.

Выходной импульс с формирователя

20 поступает на управляемый вход регистра 22, осуществляя запись в регистр 22 значения кода счетчика 18.

Выходной импульс с формирователя

21 поступает одновременно на сбросовый вход счетчика 18, устанавливая его в нулевое состояние, и на вход формирователя 23 в качестве сигнала на разрешение формирования выходной ,структуры последовательного десятич ного кода.

Одновременно с первым тактовым импульсом через элемент 24 на вход линии 17 задержки, представляющей собой генератор фиксированного числа импульсов, поступает первый разряд последовательного двоичного кода.

С первого отвода линии 17 задержки при значении первого разряда входного кода 1 через. элемент 2 на счетный вход счетчика 18 поступает один им15 пульс для заполнения первой декады счетчика 18.

При этом суммарнсе время задержки ф формирова .-еля 19%р1,формирователя

2Мф и формирователя 21 iy» должно щ быть меньше или равно времени задержки элемента 24. еф Эь

Второй тактовый импульс перебрасывает переключатель 1 с первого полоЯ жения во второе. Со втброго отвода переключателя 1 подается напряжение разрешения (второй стробирующий импульс) на элемент 3. На элементы И выдается запрет. рц Одновременно со сторым тактовым импульсом на вхоце переключателя 1 импульс второго разряда последова.тельного двоичного кода через элемент 24 поступает на вход линии 17 задержки, с первых двух отводов которой снимаются два параллельно-последовательных импульса и поступают на элемент 11, с выхода которого два последовательных импульса через элемента 3 поступают на счетный вход

40 счетчика 18 для заполнения первой декады счетчика 18.

Третий тактовый импульс перебрасывает переключатель 1 со второго положения на третье. С третьего вывода переключателя 1 снимается напряжение с разрешения на.элемент 4. На остальные элементы И выдается запрет. Одно.временно с третьим тактовым импульсов на входе переключателя 1 им$0 пульс третьего разряд последовательного двоичного кода через элемент 24 поступает на вход линии 17 задержки, с первых четырех отводов которой сни.маются четыре параллельно-последовательных импульса и поступают на элемент 12, с выхода которого четыре ! последовательных импульса через элемент 4 поступают на счетный вход счетчика 18 для заполнения первой декады счетчика 18.

60 Четвертый тактовый импульс перебрасывает переключатель 1 с третьего положения в четвертое. С четвертого выхода переключателя 1 снимается напряжение разрешения на элемент 5. На 5 остальные элеМенты И выдается за782155 прет. Одновременно с четвертым тактовым импульсом импульс четвертого разряда последовательного двоичного кода ерез элемент 24 поступает на вход инии 17 задержки, с первых восьми отводов которой подаются восемь па-. раллельно-последовательных импуль5 сов на входы элемента 13. С выхода элемента 13 восемь последовательных импульсов через элемент 5 поступают на счетный вход первой декады счетчика 18 для ее заполнения.

Пятый тактовый импульс перебрасывает переключатель 1 с четвертого положения на пятое. С пятого вывода переключателя 1 снимается напряжение разрешения на элементы б и 7. На »5 остальные элементы выдается запрет.

Одновременно с пятым тактовый импульсов импульсы пятого разряда последовательного двоичного кода через элемент 24 поступают на вход линии 17 20 з адержк и,.

Сначала с первых шести отводов линии 17 задержки шесть параллельиопоследовательных импульсов через элемент б подаются на счетный вход первой декады счетчика 18 для ее заполнения, затем с седьмого отвода линии

17 задержки через элемент 7 один импульс поступает на счетный вход второй декады счетчика 18 для его заполнения.

Преобразование шестого и седьмого разрядов последовательного двоичного кода в код десятичный аналогично преобразованию пятого разряда кода.

Восьмой тактовый импульс перебра- 35 сывает переключатель 1 с седьмого положения на восьмое. С восьмого выхода переключателя 1 снимается напряжение разрешения на элементы 8, 9 и 10. На остальные элементы И вы- @» дается запрет.

Одновременно с восьмым тактовым импульсом импульс восьмого разряда через элемент 24 поступает на вход линии 17 задержки.

С первых восьми отводов линии 17 задержки восемь параллельно-последовательных импульсов подаются на входы, элемента 15, с выхода которого у» восемь последовательных импульсов че-. рез элемент 8 подаются на счетный вход первой декады счетчика 18 для ее заполнения, затем с девятого и десятого отводов линии 17 задержки два параллельно-последовательных им» пульса поступают на входы элемента 16, с. выхода которого два"последовательных импульса через элемент 9 подаются на счетный вход второй декады счетчика 18 для ее заполнения. В по- 40 следнюю очередь с одиннадцатого отвода линии 17 задержки через элемент . 10 один импульс поступает на счетный вход третьей декады счетчика 18 для ее заполнения. 65 б

Девятый десятый и т д разряды последовательного двоичного кода пре> образуются в код десятичный аналогично преобразованию восьмого разряда кода.

После преобразования последнего разряда (n-разрядного входного слова) последовательного двоичного кода в код десятичный, переключатель 1 переходит в нулевое (исходное) положение, на все Элементы И выдается запрет и содержимое счетчика 18 принимает значение в десятичном виде, соответствующее значению преобразованного входнаго двоичного кода (значение п-разрядного входного слова).

При приходе первого тактового импульса, синхронного с первым разрядом монотонно изменяющегося последовательного входного двоичного кода (последующего и-разрядного слова), описанный выше процесс повторяется.

Ограничением для линии задержки при формировании фиксированного числа параллельно-последовательных импульсов является то, что время формирования указанных импульсов с учетом задержки вспомогательного элемента задержки должно быть меньше или равно периоду следования тактовых импульсов. Т „, ьK «(Т НТаким образом, преобразование монотонно изменяющегося последовательного двоичного кода в код десятичный осуществляется в период между и-разрядными словами входного двоичного кода, а добавление единицы при монотонно возрастающем коде (или уменьшение на единицу при монотонно убывающем коде) к значению счетчика 18 и запись в регистр 22 эквивалентного кода осуществляется в момент прихода первого тактового импульса, синхронного с первым разрядом последующего

h-ðàýðÿäíîãî входного слова.

Таким образом исключается временная задержки в преобразовании монотонно изменяющегося последовательного двоичного кода в код десятичный,воэникающая за счет времени преобразования всей последовательности кодовых импульсов и-разрядного слова. управление декадным счетчиком для работы с монотонно возрастающим или монотонно убывающим входным кодом осуществляется внешним сигналом "управление", поступающим на вход счетчика 18.

Использование предлагаемого устройства преобразования последовательного двоичного кода в код десятичный позволяет полностью исключить временную задержку в преобразовании монотонно изменяющегося последовательного двоичного кода в код десятичный, определяемую количеством разрядов в слове и тактовой частотой следования кодовых импульсов; так как реоб7

782155

Формула изобретения

ВНИИПИ Заказ 8167/73 Тираж 995 Подписное

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4 разование кода производится в период между словами и-разрядного входного кода, а смена содержимого кода выход( ного регистра производится в момент прихода первого тактового импульса, синхронного с первым разрядом входного слова, с предварительным при.бавлением (вычитанием) единицы к значению кода декадного счетчика; полностью исключить зависимость времени преобразования кода от значения . входного кода, так как временная задержка в преобразований кода постоянна и определяется временем формирования импульсов первым и вторым формирователем; испольэовать предлагаемое устройство в аппаратуре обработки информации с представлением кодовой информации в единой шкале времени.

Устройство преобразования последозательного двоичного кода в код десятичный по авт.св. Р 403058, о тл и ч а ю щ е е с-я тем, что, с целью повышения быстродействия, в него введены регистр, формирователь последовательного кода, последовательно соединенные формирователи импульсов, вход первого иэ которых соединен с первым выходом переключателя, а выход — со счетным входом декадного счетчика импульсов, выход второго формирователя .импульсов — с управляющим входом регистра, третьего — с управляющим входом формирователя последовательного кода и входом установки в нуль декадного счетчика импульсов, выходы которого соединены со входами регистра, выходы которого являются выходами параллельного кода и соединены со входами формирователя последовательного кода, выход которого является выходом последовательного кода, и элемент задержки, вход которого соединен с информационной шиной, а выход — co входом линии задержки.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Р 403058, кл. Н 03 К 13/24, 18.03.71.