Преобразователь фазового сдвига во временной интервал

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОПИСЛНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

<п783704 (61) Дополнительное к авт, саид-ву М 678666 (22) Заявлено 09.0278 (21) 2578071/18-21 с присоединением заявки № (S1)M. Кл.

G 01 R 25/00

Н 03 К 13/20

Государственный комнтет

СССР по делам нзобретеннй н отк рытнй (23) Приоритет

Опубликовано 301180, Бюллетень ¹ 44

Дата опубликования описания 301180 (S3) УДК 621. 317. .77(088.8) (72) Авторы изобретения

С.И. Гусев и С.Л. Селезнев (71) Заявитель (54) ПРЕОБРАЗОВАТЕЛЬ ФАЗОВОГО СДВИГА

ВО ВРЕМЕННОЙ ИНТЕРВАЛ

Настоящее изобретение относится к электроизмерительной технике и может быть использовано при измерении фазовых сдвигов.

Известен преобразователь фазового сдвига во временной интервал по основному авт.св. Р 678666, содержащий источник опорного напряжения, три триггера, два интегратора, три ключа, инвертор, детектор нуля и два формирователя коротких импульсов. Выход одного из формирователей подключен к первому входу первого триггера, второй вход которого соединен с выходом второго формирователя и счетным вХодом второго триггера. Выход источника опорного напряжения подключен к пфтенциальным входам первого и второго ключей, управляющие входы которых соединены соответственно с выходом первого триггера и прямым выходом второго триггера. Инверсный выход второго триггера подключен к управляющему входу третьего ключа и первому входу третьего триггера. Выход первого ключа через первый интегратор и детектор нуля соединен с ,вторым входом третьего триггера. Выход второго ключа через второй интегратор и инвертор подключен к потенциальному входу третьего ключа, выход которого соединен с входом первого интегратора. Данное устройство позволяет производить преобразование фа5 зового сдвига в течение периода входных напряжений во временной интервал.

Однако данное устройство имеет невысокую точность преобразования, так как величина постоянной времени

10 интеграторов находится в зависимости от температуры окружающей среды.

Цель изобретения — повышение точности преобразования в широком диапазоне температур., 15 Эта цель достигается тем, что в преобразователь фазового сдвига во временной интервал, содержащий источник опорного напряжения, три триггера, два интегратора, три ключа, ин2О вертор, детектор нуля и два формирователя коротких импульсов, причем выход одного из формирователей подключен к первому входу первого триггера, второй вход которого соединен

25 с выходом второго формирователя и счетным входом второго триггера, выход источника опорного напряжения подключен к потенциальным входам первого и второго ключей, управляющие

Зп входы которых соединены соответствен783704

И откуда р т т.к.

2й

;но с выходом и первого и ьторого триггеров, инверсный выход второго триггера подключен к управляющему входу третьего ключа и первому входу третьего триггера, выход второго ключа через второй интегратор и ин вертор подключен к потенциальному входу третьего ключа, выход которога соединен с входом первого интегратора, введены задатчик времени, ключ и интегратор, вход которого соединен с выходами третьего и четвертого клю- © чей, а выход — c входам детектора нуля, при этом инверсный выход второго триггера подключен через эадатчик времени к управляющим входам третьего и четвертого ключей ко вта- 33 раму входу третьего триггера, а потенциальный вход четвертого ключа подсоединен к выходу первого интегратора.

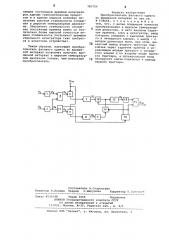

Изобретение поясняется электрической функциональной схемой преобразователя фазового сдвига ва временной интервал, изображенной на чертеже.

Преобразователь содержит формирователи 1 и 2 коротких импульсов, выходы которых соединены соответствен5 но с первым и вторым входами триггера 3, а выход формирователя 2, кроме того, подключен к счетному входу триг4. Выход триггера 3 H прямой выход триггера 4 соединены соответственно с управляющими входами ключей

5 и б,.- на потенциальные входы которых подана опорное напряжение U „ от источника опорнога напряжения. Выходы ключей 5 и б соединены соатветствен- 35 на с входами интеграторов 7 и 8. Выход интегратора 8 подключен к входу инвертара 9, а выход интегратора I к потенциальному входу ключа 10. Выход инвертора 9 соединен = потенци- 4О альным входом ключа 11, у катарога выход соединo í с выходом ключа 10 и входом третьега интегра-ора 12. Выход интегратора 12 .;ереэ детектор нуля «3 подключен к зтарсму входу григгера 14. Инверсный выход триггера 4 соединен с входом эадатчика времени 15, у которого адин иэ выходов подключен к управляющему входу ключа 11 и первому входу триггера 14, Устройство работает следующим образом., В исходном состоянии на вход формирааателя 1 поступает напряжение U, а на вход формирователя 2 — напряжение U, относительно которого измеряется фазовый сдвиг напряжения 01.

В момент перехода напряжений Uq и U2 через нулевой уровень, от отрицательнага значения к положительному, на выходах формирователей 1 и 2 образуются короткие импульсы, которые поступая на входы триггера 3, формируют на ега выходе временной интервал, ц пропорциональный фаэоваму сдвигу причем Д = 2lll где T — период колебаний напряжений

02

Импульс длительностью с открывает ключ 5 и интегратор 7 заряжается ат источника апорнога напряжения UD„ äà напряжения

U = - Пап

Ь „ где 1 — постоянная времени интегратора 7.

Одновременно на прямом выходе триггера 4 формируется импульс дли-1åëüíGñTüKl Т, который открывает ключ б, и интегратор 8:=.,àðÿæàåòñÿ от того же источника апоряага напряжения Uдо напряжения

T )Э оп л х

U Ьg где Ь2 — постоянная времени интегратора 8.

По прохождении очередного импульса от формирователя 2 триггер 4 перебрасывается, закрывая ключ б и через задатчик воемени 1.:. откры-вая ключ 10.

Напряжение с выхода интегратора 7 через ключ 10 паступае= на вход интегратора 12 и начинает заряжать ега до напряжения

U = — U - П-, Г) ttl -)

Ъ где 5> — постоянная времени интегратора 12;

t>z — эталонное время, задаваемое з адатчиком време.-,и .

Через время tgn, от прихода входного импульса на в -.ором выходе =-адатчика времени вырабатывается сигнал перебрасывающий триггер 14, формируя начало временного интервала и открывая ключ 11.

Инвертированное напряжение Ulna c выхода интегратора 8 начинает разря>хать интегратор 17, -аряженный до напряжения Un, . Ин-.;егратор 12 разряжается да нуля за время tw . При этом Ъ

tx = „ -г- tan

Р Со то

При достижении нулевого уровня на выходе интегратора 12 детектор нуля 13 перебрасывает триггер 14, формируя на ега выходе временной интервал

Отличительной особенностью вь1раже ния выходного временнагo интервала в предложенном устройстве является то, чта в него входит отношение

„ постоянных времени интеграларав и при изготовлении э IeMBBTGB, опреде783704

Составитель A. Старостина

Редактор Н.Коляда Техред С.Мигунова Корректор Н.Григорук

Заказ 8539/48 Тираж 1019 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и,открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4 ляющих постоянную времени интеграторов,единым технологическим процессом и в едином корпусе возможно получение высокой стабильности отношения в широком температурном диапазоне. Обеспечить стабильность отноше.ния постоянных времени можно со значительно более высокой точностью нежели стабильность постоянной времеии отдельного интегратора (как требуется в известном устройстве).

Таким образом, настоящий преобразователь фазового сдвига во временной интервал позволяет получать временной интервал в широком. температурном диапазоне точнее, чем известный преобразователь.

Формула изобретения

Преобразователь фазового сдвига во временной интервал по авт.св.

9 678666, отличающийся тем, что, с. целью повышения точности преобразования в широком температурном диапазоне, в него введены эадатчик времени, ключ и интегратор, вход которого соединен с выходами третьего и четвертого ключей, а выход †с входом детектора нуля, при этом, ин1Ц версный выход второго триггера подключен через задатчик времени к управляющим входам третьего и четвертого ключей и ко второму входу третьего триггера, а потенциальный вход четвертого ключа подключен к выходу ,первого триггера.