Преобразователь двоичного кода в двоично-десятичный

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (6i ) Дополнительное к авт. свид-ву (22) Заявлено 150179 (2f) 2714577/18-24 {51)М. Кл. с присоединением заявки Мо (23) Приоритет

G 06 F 5/02

Государственный комитет

СССР по делам изобретений и открытий

Опубликовано 30.1180, Бюллетень Но 44

Дата опубликования описания 301180

{53) УДК 681. 325 (088. 8) (72) Авуоры изобретения

Л.А. Волкова, В.А. Канашкевич и В.Г. Ковган (71) Заявитель (54) ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОГО КОДА В

ДВОИЧНО-ДЕСЯТИЧНЫЙ изобретение относится к области автоматики и вычислительной техники и может быть использовано при построении преобразующих устройств в автоматизированных системах управления и информационных системах.

Известен преобразователь двоичного кода в двоично-десятичный)1, содержащий регистр множимого, регистр множителя, блок порядков и корректирующих коэффициентов, последовательный сумматор, регистр прбизведения и управляющие логические элементы.

Недостаток этого преобразователя состоит в том, что корректирующий коэффициент должен быть рассчитан заранее для заданного диапазона преобразующих чисел. Кроме того, в нем применен последовательный принцип работы, что ограничивает быстродействие.

Наиболее близким к изобретению по технической сущности и схемному решению является преобразователь двоичного кода в двоично-десятичный 2),, содержащий двоичный счетчик, первый и второй последовательно соединенные двоично-десятичные счетчики, информационные выходы которых являются выходами преобразователя, генератор импульсов, элемент И-НЕ, первый вход которого соединен с выходом генератора импульсов, а второй вход — с выходом двоичного счетчика.

5 Недостаток этого преобразователя в том, что он обрабатывает только числа с фиксированной запятой и не может преобразовывать числа с плавающей запятой. Другой его недостаток

10 состоит в недостаточно высоком быстродействии.

Цель изобретения — расширение класса решаемых задач за счет возможности преобразования чисел в форме с плавающей запятой и увеличение быстродействия.

Поставленная цель достигается тем, что в преобразователь двоичного кода в двоично-десятичный, содержащий

20 двоичный счетчик первый и второй

I последовательно соединенные дв оичнодесятичные счетчики, информационные выходы которых являются выходами преобразователя, генератор импульсов, 25 элемент И-НЕ, первый вход которого соединен с выходом генератора импульсов, а второй вход — с выходом двоичного счетчика, дополнительно введены двоичный делитель частоты, деся30 тичный делитель частоты, первый и

783788 второй коммутаторы, регистр порядка, регистр мантиссы, управляемый делитель частоты и дешифратор порядка.

Прк этом вход дешифратора порядка соединен с выходом регистра порядка и управляющими входами первого коммутатора к управляемого делителя час5 готЫ, а выход дешкфратора порядка подключен к установочному входу второго двоична-десятичного счетчика, счетный хвод которого соединен с входом записи двоичного счетчика, а выход — с управляющим входом второго коМмутатора. Выходы первого и второго коммутаторов соединены соответственно со счетными входами двоичного счетчика к первого двоична-десятичного 15 счетчика, а информационные входы гервого к второго коммутаторов связаны с выходами двоичного и десятичного делителей частоты соответственно, счетные входы которых соединены с выходами элемента И-НЕ к управляемого делителя частоты соответственно.

Выход элемента И-НЕ, кроме того, соединен с тактовым входом управляемого делителя частоты, выход регистра мантиссы — с информационным вхацом,цвоичного счетчика. Входы регистра мантиСсы и регистра порядка являются входами преобразователя.

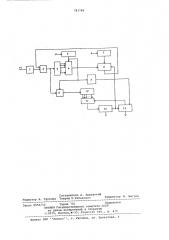

На чертеже представлена блок-схема предлагаемого преобразователя, В его состав входят генератор 1 имцульсав, элемент И-НЕ 2, двоичный делитель 3 частоты, первый коммутатор 4, регистр 5 порядка, управляемый делитель б частоты, регистр 7 35 мантиссы, двоичный счетчик 8, дешифратор 9 порядка, десятичный делитель

10 частоты, второй коммутатор 11, двоична-десятичные счетчики 12, 13, вход Пуск 14.

Математическое обоснование рабаты устройства следующее.

Любое число в нормальной форме записывается следующим образом:

Y =!Д.X -в двоичной системе счисления;

Y,= М„I.Π— в десятичной систеМе ,ц — С счисления, где p,,re -соответственно значения мантиссы к порядка чисел в двоичной системе счкс- 5О ления;

>р -соответственно значения мантиссы и порядка чисел в десятичной системе с-1исления„ 55

TcLI< как gq=Qqy „то „,- 4.0 " - 2 откуда

2 JIG JQ 10

Иэ формулы следует, что для того, чтобы осуществить пересчет мантиссы двоичного числа„ подавая на счетный вход двоичного счетчика импульсы с частотой f в мантиссу двоична-деХ сяткчного числа, на счетный вход двоична-,цесяткчнога счетчика мантиссы долл<ны поступать импульсы с частотой

Преобразователь работает следующим образом.

В исходном состоянии в регистр 5 порядка заносится порядок двоичного числа, в регистр 7 мантиссы — мантисса двоичного числа. На выходе двоичнога счетчика 8 появляется разрешающий потенциал, который поступает на первый вход элемента И-НЕ 2; По команде Пуск импульсы с выхода генератора 1 поступают на второй вход элемента И-НЕ 2 и далее через двоичный делитель 3 частоты на первый коммутатор 4. В зависимости от порядка двоичного числа в регистре

5 к счетному входу двоичного счетчика 8 подключается тот или иной ,выход коммутатора 4, т.е. на него поступают импульсы с частотой,f/2, где f - частота импульсов генератора

1.

Одновременно импульсы с выхода генератора 1 через элемент И-НЕ 2 к десятичный делктель 10 подаются на вход второго коммутатора 11.

Управление зткм коммутаторам осуществляется при помощи второго двоична-десятичного счетчика 13. B зависимости от порядка десятичного числа на разрядных выходах второго двоична-десятичного счетчика, тот или иной выход поцключается к счетному входу первого двоична-десятичного счетчика 12. В результате на счетный вход двоична-де<"ятичнаго счетчика

12 поступают импульсы с частотой

f j 1 Р т

Частоты импульсов, поступающих на счетные входы счетчика 8 и двоична-десятичного счетчика 12, связаны между cîáàé как .2"

<О 1,<

При переполненик двоична-десятичного счетчика 12 сигнал переноСа поступает на вход двоична-десятичного счетчика 13 и на вход записи двоичного счетчика 8 и процесс счета повторяется до обнуления двоичного счет чика 8. При абнуленкк двоичного сче гчика 8 на его выходе переноса появляется запрещающий потенциал„- кото; рый закрывает элемент И-НЕ 2 к процесс преобразования на этом заканчивается, Быстродействие преобразователя можно оценить, исходя иэ независк мости рабаты двоична-десятичного и двоичного счетчиков.

Время, через которое обнуляется двоичный счетчик мантиссы, опредепяется количеством разрядов преоб»

783788 раэуемого двоичного числа и частотой импульсов генератора ь пр где n — количество разрядов мантиссы двоичного, числа.

Время преобразования растет с ростом порядка преобразуемого числа.

Однако по величине порядка двоичного кода всегда можно приблизительно оценить порядок десятичного числа. i0

Эту роль в устройстве выполняет дешифратор 9 порядка. Приближенное значение порядка десятичного числа заносится в двоично-десятичный счетчик 13.

Если истинная величина десятичного порядка преобразуемого числа выше приближенной, то происходит переполнение двоично-десятичного счетчика 12 и содержимое двоично-десятич- gp ного счетчика 13 увеличивается на единицу, после чего процесс преобразования повторяется.

Применение дешифратора порядка позволяет увеличить быстродействие, исключив операции подбора величины десятичного порядка.

Если, начиная с некоторого значе- ния двоичного порядка, произвести увеличение частоты в 2 раэ, то не- в обходимо во столько же раз увеличить 30 и частоту f генератора 1

Аналогичным образом увеличивая в

l0 раз частоту, подаваемую на двоично-десятичный счетчик 12, получим

1O" f, =ô. O",0

Оба счетчика должны работать син- 40 хронно и, следовательно, должно выполняться равенство,.

2Р f =g у.fo где g — корректирующий коэффициент. 45

Таким образом; появляется возможность повышения быстродействия преобразователя эа счет увеличения частоты генератора, которая ограничена быстродействием применяемых логичес- 50 ких схем, эа счет введения делителя частоты с коэзфициентом деления fO /ß, который подключается при порядках двоичного числа, равных С, и выше.

Управление делителем частоты осущест- нляется при этом декодером.

Значение величины двоичного порядка, начиная с которого производится увеличение частоты f< можно задать не одно, а несколько. Тогда в зависимости от порядка преобразуемого дно- . 40 ичного числа будет устанавливаться тот или иной коэффициент деления частоты.

Оченидно, что реализация делителя частоты с переменным коэффициентом 65 деления возможна лишь н том случае, когда число 10"/ целое.

Кроме того, получается выигрыш н оборудовании, поскольку отпадает необходимость н двоичных делителях

2 и выше.

Ь

Предполагаемое устройство оперирует с числами, представленными н форме с плавающей запятой, что существенно расширяет диапазон решаемых задач формула.изобретения

Преобразователь двоичного кода н дноично-десятичный, содержащий двоичный счетчик, первый и второй последовательно соединенные двоично-десятичные счетчики, информационные выходы которых являются выходами преобразователя, генератор импульсов, элемент И-НЕ, первый вход которого соединен с выходом генератора импульсов, а второй вход — с выходом двоичного счетчика, д т л и ч а ю— шийся тем,, что,,с. целью расширения класса решаемых задач за счет воэможности преобразования чисел и форме с плавающей запятой и увеличения быстродействия, в. него внедены двоичный делитель частоты, десятичный делитель частоты, первый и второй коммутаторы, регистр порядка, регистр мантиссы, управляемый делитель частоты и дешифратор порядка, вход которого соединен с выходом регистра порядка и управляющими входами перного коммутатора и управляемого делителя частоты, а выход дешифратора порядка соединен с установочным входом второго двоично-десятичного счетчика, счетный вход которого соединен с входом записи двоичного счетчика, а вь|ход — с управляющим нходом второго коммутатора, выходы первого и второго коммутато-, ров соединены соответственно со счет. ными нходами двоичного счетчика и перного двоично-десятичного счетчика, а информационные входы первого и второго коммутаторов соединены с выходами двоичного и десятичного делителей частоты соответственно, счетные входы которых соединены с ныходами элемента И-НЕ и управляемого делителя частоты соответственно, выход элемента И-НЕ, кроме того, соединен с тактовым входом управляемого делителя частоты, выход регистра мантиссы соединен с информационным входом двоичного счетчика, входы регистра мантиссы и регистра порядка являются входами преобразователя °

Источники информации, принятые во внимание при экспертизе

1. Анторское свидетельство СССР

Р 547763, кл. G 06 F 5/02, 1977.

2. Авторское свидетельство СССР

Р 468236, G 06 F 5/02, 1975 (прототип) .

783788

Сос тавитель А, Аршавск ий

Редактор И. Грузова Техред М,Табакович Корректор N, Вигула

Заказ 8550/52 Тираж 751 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва,Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, r. Ужгоюод, ул. Проектная, 4