Устройство для нормализации двоичных чисел

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ПИ -Е

ИЗОБРЕТЕНИЯ

<1и783 792 Ф

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 220179 (2 f ) 2716076/18-24 с присоединением заявим Йо (23) Приоритет

Опубликовано 30,1180. Бюллетень Мо 44

G 06 F 7/38

Государственный комитет

СССР ио делам изобретений и открытий (53) УДК 681.3 (088.8) Дата опубликования описания 30,11.80 (72) Авторы изобретения

В .Ф. Евдокимов, Н.П. Тимошенко, М.Е. Цыгановский, П.А. Тарчук и Б.К. Крыжный (73) Заявитель

Институт электродинамики AH Украинской ССР (54) УСТРОЙСТВО ДЛЯ НОРМАЛИЗАЦИИ ДВОИЧНЫХ

ЧИСЕЛ

Изобретение относится к автомати. ке и вычислительной технике и может быть использовано при создании высокопроизводительных вычислительных

1 систем.

Известна логическая схема сдвига (1), состоящая из нескольких схем логических уровней, каждый из которых содержит логические-элементы типа И, или (1).

Число t уровней, на которые разделена логическая схема сдвига, является целым числом и должно удовлетворять соотношению 2 СИ+1 Ь.2 о (N+1 — разрядность нормализуемого тэ числа) .

Каждый из уровней содержит логический блок сдвига влево, с помощью которого двоичное число сдвигается влево на определенное число разрядов. 2{)

Известно сдвигающее устройство, позволяющее выполнять сдвиг входной информации параллельно,на требуемое число разрядов за один такт и содержащее матрицу иэ элементов памяти 25 долговременного типа (триггеров) и логические схемы И, ИЛИ (2).

Наиболее близким к изобретению является устройство для нормализации чисел, содержащее несколько пос- 3О ледователько соединенных схем логических уровней, каждая из которых содержит анализатор содержимого групп ка куль, соединенный входами с выходами вентильной схемы предыдущего уровня, а выходами — c входами дешифратора величины сдвига, выходы которого подключены к входам шифратора и вентильной схемы данного уровня (3$, К-разрядное число N определяющее количество нулей перед старшим ненулевым разрядом нормализуемого числа, разбивается на группы, содержащие количество разрядов К(, К о, 4 П(1 и 3 4

Вентильная схема каждого логического уровня сдвигает число влево на величину, определяемую весовыми коэффициентами,и значениями разрядов соответствующей группы.

С увеличением разрядности нормалиэуемого числа растет число логических уровней, что приводит к увеличению(аппаратурных затрат и времени выполнения операции нормалиэаци и °

Недостатком этого устройства являются сравнительно большие аппаратные затраты и зависимость времени

783792 выполнения операции нормализации от разрядности нормализуемого числа.

Цель изобретенйя — упрощение устройства.

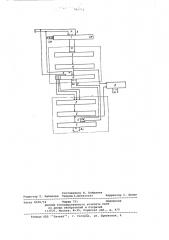

Достигается она тем, что устройство для нормализации двоичных чисел, вКлючающее коммутаторы и дешифраторы, причем информационные входы первого коммутатора соединены с первым входом устройства, информационные входы второго коммутатора соединены с вЫходами первого коммутатора, содержит регистр порядка, два шифратора, сумматор, первая группа вхоцов кото. рого подключена к первому и второму входам устройства, выход переноса каждой из -N тетрад сумматора (N=n/4, 35 где п - разрядность нормализуемых чисел) подсоединен к соответствующему входу первого дешифратора, выходы которого соединены с входами первого шифратора, связанного выходами щ с первой группой входов регистра порядка и с управляющими входами первого коммутатора, выходы трех старших разрядов которого соединены с входами второго дешифратора, связанного выходами с входами второго шифратора, выходы которого соединены с второй группой входов регистра порядка и с усправляющими входами второго коммутатора.

Блок-схема устройства приведена на чертеже. устройство содержит сумматор 1, первый и второй дешифраторы 2 и 3, первый и второй шифраторы 4 и 5, первый и второй коммутаторы б и 7, ре- 35 гистр 8 порядка.

Нормализуемое число A разрядностью и разбивается íà N тетрад,,начиная со старшего разряда. В случае наличия неполной крайней тетрады она дополняется нулями. Число A является первым слагаемым, поступающим на первую группу входов сумматора 1.

Старшие разряды нормалиэуемо"o числа поступают на младшие разряды (4 N) — разрядного сумматора, а младшие разряды нормализуемого числа— на старшие разряды сумматора.

Вторым слагаемым является двоичное число, состоящее из (4N ) единиц, поступающее на вторую группу входов сумматора 1 4N разрядов сумматора 1 также разбиты на N тетрад, начиная со старшего разряда.

Таким образом, возникающий при сложении перенос между тетрадами сумматора распространяется в направлении от младших тетрад сумматора к старшим, а по отношению к тетрадам нормализуемого числа — от старших к младшим. 4О

При поступлении на сумматор 1 и-разрядного нормализуемого числа

A и (4Ы) - единиц второго слагаемого на выходе сумматора формируется Nразрядное число, разрядами которого являются переносы между тетрацами сумматора.

Первый перенос формируется в тетраде сумматора, на которую поступает старший ненулевой разряд нормалиэуемого числа. При этом но всех последующих старших тетрадах сумматора формируются переносы неэавнсимо от нулей в соответствующих тетрадах нормалиэуемого числа.

Нули в N-разрядном числе на выходе сумматора 1 соответс — âóþò тетрадам нормализуемого числа, состоящим иэ одних нулей и находящимся перед первой значащей тетрадой нормализуемого числа.

Первый дешифратор 2 в соответствии с поступающим на его входы Иразрядным числом из сумматора 1 формирует сигнал выбсрки из первого шифратора,где записаны номера тетрад нормализуемогo числа, начиная с нулевого номера.

На выходе первого шифратора 4 в соответствии с кодом N-разрядного числа формируется номер первой значащей тетрады нормалиэуемогo числа, Выходы первого шифратора coåäèнены с первой группой входо, регистра 8 порядка и входами управления первого коммутатора б.

Номер первой значащей тетрады поступает на входы управления первого коммутатора б, обеспечивая сдвиг поступающего на информационные входы первого коммут"..òîðà б нормализуемого числа на 4 K разрядов влево, гдов. К - rro

Одноьременно К записывается в

m — 2 старших разряда m-разрядного регистра 8 порядка (m-разрядное число определяет ксличество нулей перед старшим ненулевым разрядом нор мализуемого числа A}

Запись номера . <; в m — 2 старших разряда регистра порядка 8 соответствует записи величины сдвига влево на 4 К, осуществленного в первом коммутаторе б.

Сдвинутое На 4 К разрядов влеэо нормалиэуемое число А поступает на входы второго коммутатора 7.

Иаксимальное число нулей перед старшим ненулевым разрядом сдвинутого нормализуемого числа Л равно трем, 4

Старшие три разряда первого коммутатора б выходами соединены с входами второго дешифратора 3, выходы которого соединены с входамн второго шифратора 5. Второй дешифратор

3 .формирует сигналы выборки иэ второго шифратора 5 номера старшего ненулевого разряда сдвинутого числа

A по формулам вида (1

А2 Д1 ла 2ь а 3 1

783792

Во втором шифраторе 5 записаны номера старших четырех разрядов числа A начиная с нулевого. С выходов второго шифратора 5 номер старшего ненулевого разряда К" (двухразрядное цвоичное число) поступает на входы управления второго коммутатора 7, обеспечивая сдвиг числа А» влево на

К" разрядов и, следовательно, окончательную нормализацию числа А, и на вторую группу входов регистра 8 порядка. Двухразрядный номер К" записывается в младшие два разряда rn-разрядного регистра 8 порядка, в котором после этого будет сформирован порядок нормализованного числа А н, При увеличении разрядности исходного нормализуемого числа А увеличивается на сОответствующее число разрядов, длина всех (за исключением второго дешифратора 3) узлов устройства для нормализации двоичных чисел.

Увеличение аппаратурных затрат, связанное с ростом разрядности исходного нормалиэуемого числа, в предлагаемом устройстве значительно меньше, чем в прототипе. Время выполнения операции нормализации постоянно, не зависит от разрядности нормалиэуемого числа и определяется по формуле вида.

Время нормализации t<-1++619, где t+- время суммирования в сумматоре.;

t>- среднее время задержки в уз лах устройства.

В качестве примера рассмотрим устройство для нормализации 40-разрядного двоичного числа, используем микросхемы серии 155.

Как показали расчеты, при реализации устройства экономия в аппаратурных затратах (в количестве используемых микросхем) по сравнению с устройством, выбранным в качестве прототипа, достигает ЗОВ {Р=ЗОЪ).

В случае нормализации и-разрядного числа с последующим использованием старших разрядов мантиссы нормализованного числа (E(n) экономия в аппаратурных затратах предлагаемого устройства по сравнению с прототипом стАновится более значительной (например, при n=40 и 3 =12, Р=45Ъ) .

Формула изобретения

Устройство для нормализации двоичных чисел, содержащее коммутаторы и дешифраторы, причем информационные входы первого коммутатора соединены с первым входом устройства, информационные входы второго коммутатора

»5 соединены с выходами первого коммутатора, о т л и ч а ю щ е е с я тем, что, с целью упрощения устройства, оно содержит регистр порядка, два шифратора, сумматор, первая группа входов () которого подключена к первому и второму входам устройства, выход переноса каждой из N тетрад сумматора (N=n/4, где и — разрядность нормализуемых чисел) подсоединен к соответствую щему входу первого дешифратора, выходы которого соединены с входами первого шифратора, связанного выходами с первой группой входов регистра порядка и с управлякщими входами первого коммутатора, выходы трех стар () ших разрядов которого соединены с входами второго дешифратора, связанного выходами с входами второго шифратора, выходы которого соединены с второй группой входов регистра по35 рядка и с управляющими входами второго коммутатора.

Источники информации, принятые во внимание при экспертизе

1. Патент Японии Р 48-23866, gp кл. G 06 F 7/54, 1973.

2. Патент Великобритании Р 1323825 кл, G 06 F 7/00, 1973.

3. Авторское свидетельство СССР

Р 397908, кл. G 06 F 7/38,,1972 (пРо тотип) .

783

Заказ 8550/52 Тираж 751 Подписное

ВНИИПИ Государственного ко митета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5 г. Ужгород, ул. Проектная, 4

Филиал ППП Патент, Составитель В. Кайданов

Редактор Т. Рыбалова Техред A,Ùåïàíñêàÿ Корректор С. Щомак