Процессор

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

<»783795

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. саид-ву Р 526900 (22) Заявлено 240179 {21) 2717714/18-24 с присоединением заявки № (23) Приоритет

Опубликовано 30118р Бюллетень ¹ 44

Дата опубликования описания 3Q1 18 р (51)М. Кл.з

G 06 F 15/00

Государственный комитет

СССР по делам изобретений и открытий (53) УДК 681.3 (088.8) (72) Авторы изобретения

С.В. Цакаев, Б.В. Зайцев, А.И. Журавлев, В.В. Чернов, К.П. Тиханович, В.В. Лаврешин и В.Н. Середкин (71) Заявитель (54) ПРОЦЕССОР

Устройство относится к области вычислительной техники, может быть использовано при проектировании электронных цифровых вычислительных машин и является усовершенствованием известного устройства по авт. св.

Р 526900.

В основном изобретении по. авт.св.

Р 526900 описан процессор (1) содержащий распределитель импульсов, регистр микрокоманды, блоки формирования приемов и выдач, клавишный регистр,клавишный регистр информации, регистр адреса запоминающего устройства, регистр сигналов обмена .15 с оперативным запоминающим устройством, регистр индикации и блок регистров общего назначения. При этом все регистры подключены к межрегистровой магистрали, 20 к которой подключены блоки формирования приемов и выдач, которые соединены с регистром микрокоманд.

Целью изобретения является повышение достоверности функционирова- 2> ния процессора.

Для достижения указанной цели в устройство по авт. св ° 9 526900 ввеЛены регистр ошибок, регистр контрольных кодов, формирователь сигна- 30 ла ошибки, элемент И, элемент ИЛИ и блок прерываний, выход которого соединен с входом блока микропрограммного управления. Входы регистра контрольных кодов подключены к выходам блока микропрограммного управления, а выходы регистра контрольных кодов — к межрегистровой магистрали, к которой подключен формирователь сигнала ошибки, выходом соединенный с первым входом элемента И, второй вход которого связан с выходом элемента ИЛИ, подключенного своими входами к выходам блока формирования приемов. При этом выход элемента И соединен с входом блока прерываний и с входом разрешения записи регистра ошибок, информационные входы которого подключены к выходам блока формирования выдач, а выходы регистра ошибок подсоединены к межрегистровой магистрали.

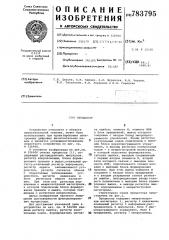

Структурная схема процессора представлена на фиг.1.

Процессор содержит межрегистровую магистраль 1, регистр 2 индикации, клавишный регистр 3 информации,распределитель 4 импульсов, блок 5 микропрограммного управления, блок 6 прерываний, регистр 7 микрокоманд,.

783795 элемент И 8, элемент ИЛИ 9, регистр

10 ошибок, регистр 11 контрольных кодов, формирователь 12 сигнала ошибки, блоки 13 и 14 формирования выцач и приемов соответственно, которые име!от одинаковую внутреннюю структуру и состоят, например, каждый из входной сборки, дешифратора, элементов памяти. В качестве формирователя 12 сигнала сшибки может быть применена схема свертки информации по некоторому модулю.

Контроль за отсутствием сбоев в работе блоков процессора осуществляет ся в момент передачи информации по межрегистровой магистрали 1. Пусть, например, необходимо переслать инфор- 35 мацию по межрегистровой магистрали из регистра i в регистр 3, Для этого на входы блоков формирования выдач и приемов из регистра 7 микрокоманд или из регистра 3 поступают кодь!, соответству!ощие номерам подключаемых регистров. С выхода блока 13 формирования выдач на. вход регистра. приходит сигнал, разрешающий считывание данного регистра B межрегистрову!о магистраль, одновременно код, соответствующий номеру регистра, пОступает на вход регистра 10 ошибок, По магистрали 1 информация поступает на вход регистра 3, а также в форми-, рователь 12 сигнала ошибки. 39

Сигнал записи (фиг.2,6), формируе-!

ый блоком 14 формирования приемов, запаздывает по отношению сигнала очи. тывания (фиг.2,а) »а время Pt, дос- 35 таточное для осуществления контроля информации формирователем 12 сигнала ошибки. С соответствующего выхода блока 14 си-нал записи поступает на вход записи регистра j и через элемент ИЛИ 9 на вход элемента И 8, где осуществляет опрос сбоя информации. Если сигнал сбоя на выходе формирователя 1-2 отсутствует, то э о свицетельствует о тои, что на вход регистра j поступила достоверная ин- 45 формация . Далее осуществляется запись в регистр j сигнал прерывания на выходе элемента И 8 не формируетrÿ и запись в регистр 10 ошибок не проис":îäèò. 59

Контроль отсутствия сбоев при прохо!! цении информации через входные и выходные пепи рег..!стра j, а также отсутствие искажения информации при ее хранении и обработке в регистре будет осуществлен при последующем считывании информации из этого регистра.

Если при пересылке информации по иежрегистровой магистрали формирова- бО телем 12 сигнала ошибки зафиксирован сбой, сигнал ошибки поступает на первый вход у емента И 8. C соответствующего выхода блока 14 сигнал подается на вход регистра j, где осуществляет- 5

=я запись инфориаци !. Одновременно этот сигнал поступает на вход элемента ИЛИ 9 и далее на второй вход элемента И 8. С выхода элемента H 8 сигнал сбоя проходит »а вход записи регистра 10 ошибок и осуществляет запись в этот регистр кода, соответствующего номеру регистра 3., передавшего сбившуюся информацию по межрегистровой магистралиа Одновременно сигнал сбоя с выхода элемента H B поступает в блок б прерываний, далее в блок

5 микропрограммного управления и процессор переключателя на микропрограмму обработки сбоя.

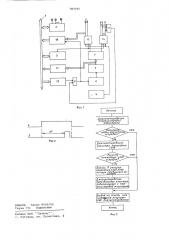

Иикропрограмма обработки сбоя начинается с диагностирования хара«тера ошибки (сбой или отказ), для это-!

"о ис поль зуетс я микропрограмма, организующая повторное выполнение команды (или группы команд) .

В случае сбоя при повторном выполнении команды (или группы «ома»д) процессор переключается на микропрограмму диагностирования H локализации неисправности, а!!горитм который представлен на фиг.З. Эта микропрограмма включает следующие действия." диагностирование межрегнстровой магистрали на отсутствие короткого заиьиания информационных разрядов на 0 или 1 „ диагностирование роботоспособности регистра командных слон; диагностирование произвольного регистра, подключенного к иежрегистровой магRcтрали, с целью локализации неисправности; вывод на индикапию или на печать результатов диагностирования.

Диагностирование межрегистровой магистрали на отсутствие короткого замыкания в одном из пнфориационных разрядов осуществл!!ется путем последовательного счиоывания в магистраль со специального поля микрокоманды через регистр )1 контрольных кодов, имеющих вид 111...1 и 000...0.

Для опроса формирователя 12 сигнала ошибки блок 14 формирует сигнал записи в регистр и»дикаи,"!и.

Если при считыва»ии первого кон= трольного кода, например, состоящего из всех единиц, будет обнаружен сбой, то контрольный код, состоящий из всех нулей, не считывается.

При считывании контрольного кода и магистраль сигнал записи D регистр индикации производит опрос сбоя по цепи". один из выхоцов блока 14, элемент HJiH 9, вход элемента И 8.

Предположим, что один из разрядов иежрегистровой магистрали 1 неиспраBBH и равен постоянно логическоиу 0, тогда при считывании н магистраль контрольного «опа 111... 1 формирователь 12 сигнала ошибки фиксирует сбой; По сигналу с выхода элемента И 8 в регистр 10 ошибок запи783795 сывается код, соответствующий номеру регистра 11 контрольных кодов, что и служит признаком неисправности межрегистровой магистрали. Кроме того, при считывании контрольного кода .111...1 иэ регистра 11 контрольных кодов в межрегистровую магистраль

1 в регистр индикации записывается контрольный код, имеющий, например, вид 1011...1. Наличие в контрольном коде нуля свидетельствует о неисправности второго информационного разряда межрегистровой магистрали. Микропрограмма диагностирования клавишного регистра 3 информации аналогична описанной микропрограмме диагностирования межрегистровой магистра- l5 ли 1 и включает запись диагностичных контрольных кодов из регистра 11 контрольных кодов в регистр 3, считывание контрольных кодов из клавишного регистра информации по межрегистро - ;щ вой магистрали в регистр 2 индикации.

При неисправности клавишного регистра 3 информации после завершения диагностирования в регистре 10 оши- бок будет храниться код, соответствующий номеру клавишного регистра инфор:мации.

Для того, чтобы использовать одну общую микропрограмму для диагностирования и локализации неисправности во всех остальных регистрах, подключен- 30 ных к межрегистровой магистрали, из регистра ошибок в клавишный регистр информации пересылается код, соответствующий номеру неисправного регистра.

Локализация неисправности, как и в 35 предыдущих случаях, производится с помощью кодов, состоящих иэ всех нулей и из всех единиц. Подключение регистра ll контрольных кодов к межрегистровой магистрали осуществляется микропрограммно, а неисправный контролируемый регистр подключается к межрегистровой магистрали с помощью кода, поступающего на входы блоков формирования приемов и выдач иэ клавишного регистра 3 информации.

Как и в предыдущих случаях, в контролируемый регистр записывается контрольный код. В момент считывания контрольного кода иэ проверяемого регистра в межрегистровую магистраль формирователь 12 сигнала ошибки проверяет считанный код на наличие сбоя и, если сбой обнаружен, в регистре

10 ошибок фиксируется код номера сбившегося регистра, в регистре 2 индикации фиксируется сбившийся раз" ряд.

Формула изобретения

Процессор по авторскому свидетельству Р 526900, о т л и ч а ю щ и йс я тем, что с целью повышения достоверности функционирования, в него дополнительно введены регистр ошибок, регистр контрольных кодов, формирователь сигнала ошибки, элемент

И, элемент ИЛИ и блок прерываний, выход которого соединен с входом блока микропрограммного управления,входй регистра контрольных кодов подключены к выходам блока микрЬпрограммного управления, а выходы регистра контрольных кодов — к межрегистровой магистрали, к которой подключен формирователь сигнала ошибки, выход которого соединен с первым входом элемента И, второй вход которого соединен с выходом элемента ИЛИ, подключенного своими входами к выходам блока формирователя приемов, при этом выход элемента И соединен с входом блока прерываний и с входом раз.решения записи регистра ошибок, информационные входы которого подключены к выходам блока формирования выдач, а выходы регистра ошибок подключены к межрегистровой магистрали, Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

9 526900, кл. G 06 F 15/00, 1974 (прототип).

783795

Havana

Конец

Фиг. 3

ВНИИПИ Эаказ 8550/52

Тираж 7 51 Подпис ное

Филиал ППП Патент, г. Ужт ород, ул. Проектная, 4

Д иагнастиробание м емр е г и стр ооой магистрали

Мекрегыся- нет робал магыслтраль

ucnpaÞía?

Д иагностирооание регистра кщчанднык слоо

Регистр команднык сло испрабен да.Запись б регистр командных слод када и о м еро со ибшег осл pezucm а

Д иа гн асспироба ние проигбольнога регистра, подключенного к иежрег истробой и а гистрал

Выбод но nevamb или индикодии резулыпатоо диа гностиробанил