Формирователь серии импульсов

Иллюстрации

Показать всеРеферат

Сеюз Советскими

Сецмеектичееиии

Оеевубаик

ОП-И САН

<„>783957

К АВТОРСКОМУ СВИ ВТВЛЬСТВУ (61) Дополнительное к авт. санд-ву М 663090 (22) Заявлено 090878 {213 2654437/18-21 с присоединением заявки ИЯ (23) Приоритет

Опубликовано 301180, Бюллетень М 44

Дата опубликования описания 3011ЯО (51)М. Кл.з

Н 03 К 3/64

Государственный комитет

СССР

Ilo дмам нзобретекнй я вткрытнй (53) УДК 621. 374 °.38(088.8) {72) Авторы изобретения

В.К. Буевич, В.П. Левин, A.Е. Лутченко, Р.И. Полонников и Е.М. Скороходов (73 3 Заявитель (54) ФОРМИРОВАТЕЛЬ СЕРИИ ИМПУЛЬСОВ

С ПРОГРАММНЫМ УПРАВЛЕНИЕМ

Изобретение относится к импульсной технике H может быть использовано в цифровой аппаратуре для формирования периодических последовательностей пачек импульсов, Известен формирователь серии импульсов с программным управлением по основному авт. св. 9 663090, содержащий опорный генератор, блок программ, . преобразователь код-временной интервал и делитель-фазосдвигатель (ij .

Недостатком известного устройства является низкое быстродействие, которое ограничивается временем формирования и передачи кодов из блока программ в преобразователь код-временной интервал.

Целью .изобретения является повышение быстродействия формирователя.

Укаэанная цель достигается тем, что s формирователь серии импульсов с программным управлением, содержа:щий опорный генератор, блок программ, преобразователь код-временной интервал и делитель-фаэосдвигатель, выход которого соединен с С-входом преобразователя код-временной интервал, управляющие входы которого поразрядно соединены с выходами старших разрядов блока программ, выходы младших разрядов которого подключены к управляющим входам делителя-фазосдвигателя,синхроннэирующий вход которого "соединен с выходом опорного генератора, а Чвход блока программ соединен с V-входом и выходом преобразователя кодвременной интервал, введен ждущий элемент задержки, управляющие входы которого поразрядно соединены с выхот6 дами средних разрядов блока программ, а V- и С-входы ждущего элемента задержки соединены соответственно с

Ч н С-входами преобразователя код-вре- менной интервал.

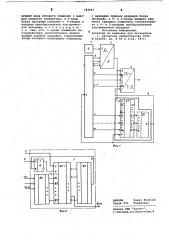

15 На фиг. 1 представлена функциональная схема устройства; на фиг.2 функциональная схема примера конкретного выполнения ждущего элемента задержки.

2О Формирователь серий импульсов с программным управлением содержит опорный генератор 1, делитель-фазосдвигатель 2,. блок программ 3, ждущий элемент задержки 4 и преобразователь

2Ç код-временной интервал 5.

Ждущий элемент задержки (фиг. 2) содержит триггер 6, сдвигающий регистр 7, дешифратор 8 нулевого состояния регистра и многовыходной дешнфЗО ратор 9.

783957

35

50

Формула изобретения

55 нен с С-входом преобразователя код<0. временной интервал, управляющие входы

Сущность нэобретения состоит в том. что функции формирования периодов, изменяющихся с дискретом, соответствующим коду младшего разряда из группы старших разрядов, выполняет преобразователь 5. Функцию формирования периодов, изменяющихся с минимальным -Дискретом, соответствующим младшему

Разряду группы кодов средних разрядов и Периоду частоты сигналов синхронизации регистра 7, выполняег ждущий элемент задержки 4.

Устройство работает следующим образом.

Преобразователь 5 формирует периоды, изменяющиеся со сравнительно грубыми дискретами. Их длительность выбирается бблЬшей, чем время, необхо"димое для выполнения команды формировайия нового кода числа в блоке 3.Для формировайия периодов с грубыми интервалами из блока 3 по группе старших разрядов подается код числа на соответствующие входы управления преобразователя 5. Входы его младших разрядов не задействованы. В результате ,часть схемы счетчика преобразователя

5, относящаяся к группе младших разрядов, работает в режиме с постоянным коэффициентом пересчета и служит в качестве генератора грубых дискретов для части схемы преобразователя

5, которая относится к группе старших разрядов и управляется сигналами с выходов старших разрядов преобразователя 5.

Счетчик преобразователя 5 работает в режиме вычитания и формирует на выходе своего дешифратора (ДС) сигналы в те моменты, когда все "его"трйггеры устанавливаются в состояние

"0". Сигнал с выхода дешифратора поступает на Ч-вход счетчика преобразователя 5 и разрешает перезапись кода с выходов старших разрядов блока 3 в этот счетчик. Одновременно этот сигнал поступает на вход блока 3, по которому в нем формируется новый код числа. Сигнал с выхода преобразователя 5 поступает также íà V-вход (стартвход) элемента задержки 4, по которому на его выходе формируется пачка импульсов с короткими интервалами, задержанными относительно пускового сигнала пропорционально коду числа средних разрядов блока 3 и периоду сигналов на С-входе регистра 7. Затем цикл работы устройства повторяется.

Принцип работы элемента задержки

4 состоит в следующем.

В режйме, когда в регистре 7 отсутствует информация (все его триггеры установлены в "0") на выходе дешифратора 8 имеется сигнал, которым триггер б по Р-входу удерживается в состоянии "0". При этом на входе регистра 7 имеется"уровень сйгнала ;запрещакщий прохождейие синхронизирую-, щих- импульсов с выхода делителя-фазо" сдвигателя 2 на его схему сдвига. В момент поступления кода числа по шинам средних разрядов с блока 3 на входы многовыходной схемы дешифратора 9 на одном из его выходов формируется импульс, которым соответствующий триггер регистра устанавливается в состояние "1". При этом на выходе дешифратора 8 снимается сигнал запрета и триггер 6 переходит в режим ожидания сигнала "старт". Этот сигнал

Ю формируется на выходе преобразователя 5 в момент обнуления его счетчиков. Сигналом "старт" триггер б устанавливается в состояние "1" и разрешает прохождение синхроимпульсов на регистр 7. В этом режиме регистр 7 выдвигает информацию до момента своего обнуления. Как только содержиМое регистра 7 станет равным нулю, на выходе дешифратора 8 вновь появляется сигнал, которым триггер б вновь устанавливается в состояние "0" и схема элемента задержки 4 переходит в режим ожидания.

Схема элемента задержки 4 может выдавать пачку импульсов с определенной временной расстановкой импульсов, если на ее управляющие входы подать последовательно коды различных чисел.

От .каждого кода один из триггеров регистра 7 устанавливается в состояние

"1". Таким образом, заранее можно сформировать пачку из Р импульсов, которая выдается из элемента задержкй 4 по команде, поступающей из преобразователя 5. Каждый импульс в пач- ке задержан относительно пускового импульса на величину, пропорциональйую коду числа шин средних разрядов блока 3, и частоте синхроимпульсов, формируемых делителем-фазосдвигателем 2.

Таким образом, быстродействие устройства определяется частотой синхроимпульсов, поступающих на элемент задержки 4. Преимуществом устройства является также то, что засылка кодов иэ блока программ 3 в ждущий элемент задержки 4 по "шинам средних разрядов может осуществляться, в любой последовательности.

Формирователь серии импульсов с программным управлением по авт.св.

9 663090, содержащий опорный генератор, блоК проГрамм, преобразователь код-временной интервал и делительфаэосдвигатель, выход которого соедикоторого поразрядно соединены с выходами старших разрядов блока программ, выходы младших разрядов которого подключены к управляющим входам делителя-фаэосдвигателя, синхронизи783957

Фиа f

Риа8 рующий вход которого соединен с выходом опорного генератора, а Ч-вход блока программ соединен с V-входом и выходом преобразователя код-временной интервал, о т л и ч а ю щ и й- . с я тем, что, с целью повышения быстродействия, дополнительно введен ждущий элемент задержки, управляющие входы которого поразрядно соединены

I с выходами средних разрядов блока програмМ, а Ч- и С-входы ждущего элемента задержки соединены соответственно с V- и С-входами преобразователя код-временной интервал.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Р 663090, кл. Н 03 К 3/64, 1977.

1 z.9НИИПИ Заказ 8568/60

Тираж 995 Подписное

Филиал ППП Патент", r Ужгород,ул.Проектная,4