Устройство декодирования импульсной последовательности

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик пн783975

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт, свид-ву (22) Заявлено 31. 01. 79 (21) 2719656/18-21 с присоединением заявки ¹ (23) Приоритет

Опубликовано Зц118ц Бюллетень ¹ 44 (5! ) м. кл 3

Н 03 К 13/00

Государственный комитет

СССР по делам изобретений н открытий (53) УДК 621. .374(088.8) Дата опубликования описания 301180 (72) Автор изобретения

A. С. Ибрагимов

Ленинградский ордена Ленина электротехнический институт им. В. И. Ульянова (Ленина) (71) Заявитель е

I ъ„:а(54) УСТРОЙСТВО ДЕКОДИРОВАНИЯ ИМПУЛЬСНОЙ

ПОСЛЕДОВАТЕЛЬНОСТИ

Изобретение относится к области импульсной техники и может быть использовано при обработке импульсных ° сигналов.

Известно устройство декодирования импульсной последовательности, содержащее генератор импульсов, подключенный к управляющему входу элемента задержки. Выход элемента задержки подключен ко входу устройства, а выходы подключены к. пороговому элементу f1).

Его недостатком является низкая помехоустойчивость.

Известно также устройство декоди- 1$ рования импульсной последовательности,которое содержит генератор импуль- сов, соединенный с управляющим входом элемента задержки, и элементов совпадения, дешифратор адресов ступе- 20 ней декодирования по числу интервалов в импульсной последовательности и блок адресации ступеней декоди, рования. Выходы блока адресации ступеней декодирования подключены к 25 ,адресным входам элемента задержки, выходы элемента задержки подключены на входы соответствующих дешифраторов ступеней декодирования, выходы каждого из которых подключены к пер- 30 вым входам соответствующих элементов совпадения. Вторые выходы и элементов совпадения подключены к сигнальному входу элемента задержки. Выходы и элементов совпадения подключены к соответствующим входам блока адресации ступеней декодирования 21.

Его недостатком является низкая помехоустойчивость.

Целью изобретения является увеличение помехоустойчивости устройства.

Поставленная цель достигается тем, что в устройство декодирования импульсной последовательности, содержащее генератор импульсов, выход которого соединен с первым управляющим входом элемента задержки, пороговый элемент, один вход которого соединен с входной шиной и с первым информационным входом элемента задержки, а выход подключен к выходной шине, введены дополнительные элементы задержки, счетчик, сумматоры, элементы числовых констант, элементы поразрядного сравнения чисел, расширители импульсов, причем вход счетчика подключен к выкоду генератора импульсов и к первым

783975 4

/ управляющим входам дополнительных элементов задержки, а выходы — к первым входам первого сумматора и к первым входам элементов поразряд- ного сравнения чисел, управляющий вход первого сумматора соединен с входной шиной, выходы каждого предыдущего сумматора через элементы задержки соединены с первыми ! входами последующих сумматоров и с вторыми входами соответствующих элементов поразрядного сравнения чисел, выходы которых подключены к вторым управлякщим входам всех элементов за« держки, к управляющим входам-остальных сумматоров и через расширители импульсов — к остальным входам порогового элемента, выходы элементов числовых констант соединены с вторыми входами сумматоров.

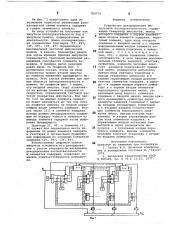

На фиг. 1 приведена схема устройства; на фиг. 2 — временные дйаграммы работы схемы при декодировании трехимпульсной серии; на фиг. 3 вариант функциональной схемы элемента задержки.

Устройство содержит генератор 1 импульсов, выход которого соединен с первым управляющим входом элемента 2-1 задержки, пороговый элемент

3, один вход которого соединен с входной шиной и с первым информационным входом элемента 2-1 задержки, а выход подключен к выходной шине, счетчик 4, вход которого подключен к выходу генератора 1 импульсов и к первым управляющим входам дополнительных элементов 2-2-2-п задержки, а выходы т к первым входам первого сумматора 5-1 и к первым входам элементов 6 поразрядного сравнения чисел, управлякнций вход первого сумматора 5-1 соединен с входной шиной, выходы каждого предыдущего сумматора 5-1-5-и через элементы 2-12-п задержки соединены с первыми входами последующих сумматоров и с вторыми входами соответствующих элементов б поразрядного сравнения чисел, выходы которых подключены к вторым управляющим входам каждого элемента 2-1-2-п задержки, к управляющим входам остальных сумматоров 5-2 — 5-п и через расширители

7:импульсов - к остальным входам порогового элемента 3, выходы элементов 8 числовых констант соединены с вторйми входами сумматоров 5-1

5-п.

3$

$0

И

Устройство работает следующим образом.

На управляющий вход сумматора

5-4 поступает импульсная последовательность подлежащая декодированию.

С йриходом импульса последовательности на управляющий вход сумматора

5-1 текущее число счетчика 4 суммируется с элементом числовой константы 6-1 последнего по порядку интервала декодируемой последователь ности, и полученная сумма числа с выхода сумматора 5-1 поступает на вторые информационные входы первого элемента задержки 2-1 и под действием импульса последователь ности и импульсов с выхода гене-, ратора импульсов 1 устанавливается на выходе элемента задержки 2-1.

К моменту прихода второго импульса последовательности произойдет сравtO нение двоичного числа на выходе эле мента задержки 2-1 и счетчика 4 посредством элемента поразрядного сравнения чисел 6-1. Импульс с выхода элемента поразрядного сравнения

f$ чисел 6-1, поступая на управляющий вход сумматора 5-2, дает разрешение на суммирование числа с выхода элемента задержки 2-1 и числа с элемента числовой константы 7 следующе 0 го интервала импульсной последовательности. Полученная сумма числа с выхода сумматора 5-2 поступает на следующий элемент задержки. Одновременно импульс с выхода поразрядного сравнения чисел 6-1,поступая на второй управляющий вход элемента задержки 2-1,осуществляет стирание числа на его выходе и разрешает перезапись импульса с первого информационного выхода элемента заЗО держки 2-1 на последующий.

Декодирование последующих интервалов последовательности осуществляется аналогично декодированию предыдущего интервала. При приеме последнего импульса последовательности на всех выходах элементов поразрядного сравнения чисел 6-1 — б-п бу1 дут присутствовать импульсы, которые поступят на вход порогового элемента 3 через расширители импульсов — 8-1 — 8-п. В результате на выходе порогового элемента 3 появится сигнал общего декодирования.

Работа предлагаемого устройства иллюстрируется графиками временного анализа, представленными на фиг. 2.

Для примера взята трехимпульсная последовательность с интервалами (2, 3) - (граф. "вх"). На граф. 1 показаны импульсы генератора импульсов 1. На граф. 4 показаны моменты смены числа счетчика 4. На граф. 5-"

5-2 отмечены моменты времени прихода импульса последовательности и соответствующие им числа в десятич- ном виде на счетчике 4-.(3, 11, 19, 27) на выходе сумматоров 5-1 (19, 27, 43) 5-2 — (19, 27). На граф.б-1, 6-2 показаны импульсы на выходах элементов поразрядного сравнения чисел, а на граф. 8-1, 8-2 — импульсы на выходах расширителей импульсов

8-1, 8-2. Момент декодирования импульсной последовательности изображенрна граф. 3 (яых).

783975

Иа фиг. 3 представлен один из возможных вариантов реализации функциональной схемы элемента задержки и график временного анализа.

На вход устройства поступают как импульсы последовательности так и импульсы помехи, нормированные по длительности. Длина последовательно соединенных триггеров (1Т, 4Т), (2T, 5Т), (3T, 6T) определяется максимальной частотой импульсной помехи в канале. Количество разрядов числа времени прихода импульсов определяется требуемой величиной ра=-решающей способности элемента задержки. В примере число разрядов равно двум. На графиках фиг. 3 15 рассмотрен случай, когда на вход устройства пришел второй импульс до момента выявления предыдущего импульса. Этот случай возможен при приеме импульса последовательности и щ помехи. Иэ графиков фиг. 3 видно, что входной импульс (код) появляет-. ся на выходе элемента задержки со скоростью, определяемой тактовой частотой генератора импульсов. Код числа (10) на выходе элемента задержки будет находиться до тех пор пока не.появится импульс на втором управляющем входе элемента задержки. Второе число (01) в элементе задержки всегда должно декодироваться следующим по порядку записи и появится на выходе элемента задержки после выявления предыдущего.

Триггеры 1Т, 4Т, и элементы 1С, 2С служат для определения места ин- 35 формации по длине элемента задержки и участвуют и организации продвижения информации по основным элементам задержки (2T, 5Т), (ЗТ, 6T).

Использование цифровой записи 4g импульса и момента его декодирования с учетом очередности интервалов декодирования последовательности в элементах задержки, позволяет повысить помехоустойчивость устройства.

ФоРмУла изобретения

Устройство декодирования импульсной последовательности, содержащее генератор импульсов, выход которого соедийен"с =первйй управля- ющим входом элемента задержки, пороговый элемент, один вход которого соединен с входной шиной и с первым информационным входом элемента задержки, а выход подключен к выходной шине, о т л и ч а ю щ е е с я тем, что, с целью повышения помехоустойчивости, в него введены дополнительные элементы задержки, счетчик, сумматоры, элементы числовых констант элементы поразрядного сравнения чисел, расширители импульсов, причем вход счетчика подключен к выходу генератора импульсов и к

I первым управляющим входам дополнительных элементов задержки, а выходы - к первым входам первого сумматора и к первым входам элементов поразрядного сравнения чисел, управляющий вход первого сумматора соединен с входной шиной,,выходы каждого предыдущего сумматора через элементы задержки соединены с первыми входами последующих сумматоров и с вторыми входами соответствующих элементов поразрядного сравнения чисел, выходы которых подключены к вторым управляющим входам всех элементов задержки, к управляющим входам остальных сумматоров и через расширители импульсов — к остальным входам порогового элемента, выходы элементов, числовых констант соединены с вторыми входами сумматоров.

Источники информации, принятые во внимание при экспертизе

1. Глобус И.Л. Двоичное кодирование в асинхронных системах М.,"Связь"

1972.

2. Авторское свидетельство СССР

М 566348, кл. Н 03 К 13/22, 1977.

783975 ф

3 4 S 6 7 8 9 1о 111213 14151Б171В 192021222324252Б2728293031

3+1f *19 11+ 1á 27 27+ 1Б -" 43

$-1

19 В=27

27+В =3Б

6-2.

3(Lr

Фиг.2 (лероый gnp. оход/ к ген., имяуль ирой уар. оход) охоЯ у т-да генера т. има (пероь ко Р устердый ива. оы ход/

1Т

„0

2Т

3Т

4Т

> к гордым оходам БТ сумматора гитарой уира Юяяющий

&од

Фиг. 3 к оь сумм тора

Составитель Т. Краснова

Редактор Н. Кол а Тех едA.Ùåïàíñêàÿ КорректорЛ

Заказ 8569/61 Тираж 995 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035 Москва Ж-35 Раушская наб., д. 4 5

Филиал ППП Патент, .г. Ужгород, ул. -Проектная, 4