Делитель частоты с коэффициентом пересчета 2 -1

Иллюстрации

Показать всеРеферат

НИЕ

ИЗОБРЕТЕНИЯ («)?8400?

Союз Советских

Социалистинесиих

Республик

К АВТОРСКОМУ СВИ 6ТЮЛЬСТВУ (61) Дополнительное к авт, саид-ву (22) Заявлено 1502.79 (21) 2725308/18-21 (51)М, Кл.з с присоединением заявки Ио—

Н 03 К 23/02

Государствеииый комитет

СССР ао делам изобретений и открытий (23) Приоритет

Опубликовано 30д 1.8 0. Бюллетень М 44

Дата опубликования описания 301180 {53) УДКб 21 . .374 (088. 8) (723 Авторы изобретения

Е,К. Иосипов, М.A.Ñîëîõà и Л.N.Ôåëüäìàí.. (71) Заявитель (54 ) ДЕЛИТЕЛЬ ЧАСТОТЫ С КОЭФФИЦИЕНТОМ

ПЕРЕСЧЕТА 2М-1

Изобретение относится к области импульсной техники и может быть использовано в устройствах обработки цифровой информации в измерительных приборах и вычислительных устройст- 5 вах.

Известен делитель частоты с коэффициентом пересчета 2N-l, содержащий

N-разрядный регистр сдвига, дополни« тельный триггер, элемент НЕ и два 10 элемента И-НЕ.

Недостатком известного делителя является его относительная сложность-.

Известен делитель частоты с коэффициентом пересчета 2N-l, содержащий 1$

N-разря,.(ный регистр сдвига, каждый разряд которого построен íà D-тригге-ре, и входную шину, которая соединена с тактовыми входами разрядов регистра сдвига, инверсный выход послед-0 него разряда которого соединен с входами D и установки в 0 перво»

ro разряда регистра сдвига, Недостатком известного делителя является несимметричность выходного 25 сигнала.

Целью изобретения является получение симметричного выходного сигнала.

Для достижения поставленной цели в делитель частоты с коэффициен- )p том пересчета 2N-1, содержащий N-разрядный регистр сдвига, каждый разряд которого построен на D-триггере, и входную шину, которая соединена с тактовыми входами разрядов регистра сдвига, инверсный выход последнего разряда которого соединен с входами

D и установки в 0 первого разряда регистра сдвига, введен.установочный триггер, вход установки и 0 которого соединен с входной шиной, а. вход установки в 1 — с инверсным ,выходом последнего раэряда регистра сдвига.

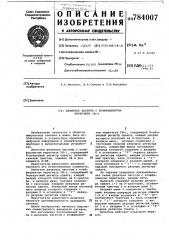

На чертеже приведена принципиальная схема делителя частоты с коэффициентом пересчета, равным пяти.

Делитель содержит разряды регистра сдвига 1-3 на О-триггерах, установочный триггер 4 и входную шину 5.

Входная шина 5 соединена с тактовыми входами разрядов регистра сдвига

1-3 и с входом установки в 0 установочного триггера 4, вход установки s 1 которого соединен с инверсным выходом разряда регистра сдвига 3 и с входами 0 и установки в О разряда регистра сдвига 1.

Делитель работает следующим образом, 784007

Составитель Р,Ранов

Редактор Н.Суханова Техред N. Табакович Корректор O.Ковинская

Эакаэ 8571/63 Тираж 995 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж=35, Раушская наб,, д .4/5 \

Филиал ППП Патент, г, Ужгород, ул, Проектная, 4

В исходном состоянии разряды регистра сдвига 1-3 находятся в нулевом состоянии, т,е, регистр сдвига находится в состоянии 000, на прямом выходе триггера 4, который является выходом устройства, присутствует также нулевой потенциал, При поступлении по входной шине переднего фронта первого тактового импульса регистр . сдвига переходит в сос- .. тояние 100, при поступлении перед-. него фронта второго тактового импуль-, са регистр сдвига переходит в состояние 110, при поступлении переднего фронта третьего тактового импульса регистр сдвига переходит в состояние

011, а на прямом выходе триггера 4 (с задержкой на сумму времен переключения разряда 3 и триггера 4) появля ется единичный потенциал, При .. поступлении переднего фронта четвертого тактового импульса регистр сдви- о га переходит в состояние 001, при поступлении переднего фронта пятого тактового импульса регистр сдвига переходит в исходное состояние, т,е, в

000; на прямом выходе триггера 4 со- 25 храняется единичный потенциал (эа счет того, что нулевой потен.циал на его входе установки в 1 сохраняется дольше на время задержки срабатывания разряда 3, чем на его Я входЕ установки. в О ), При поступленйи заднего фронта пятого тактового импульса на прямом выходе триггера 4 появляется нулевой потейци-. ал и устройство приходит к исходному 3$ состоянию.

Таким образом, делитель частоты синхронно формирует на прямом выходе ) триггера импульсы, дли гельность которых равна

=т ЪА

Ььб ЬХ Я. где N — число триггеров в делителе

Т вЂ” период следов ан ия входных импульсов, Период следования выходных импульсов равен. Т,,ы = >g (2N-1) .

Следует отметить, что в предлагаемом устройстве в регистре сдвига с обратной связью исключено состояние

111, но может быть исключено и любое другое состояние, Последнее достигается соеДинением входа установки в 1 или О какого-то разряда регистра сдвига к соответствукщему выходу предшествунхаего в кольце разряда регистра сдвига. При этом при распространении в кольцевом регистре

N единиц и N-1 нулей, естественно, вход установки в 1 триггера 4 следует соединить с прямым выходом

;последнего разряда регистра сдвига.

Формула изобретения

Делитель частоты с коэффициентом пересчета 2N-1„ содержаШий N-разрядный регистр сдвига, каждый разряд которого построен íà D-триггере, и входную шину, которая соединена. с тактовыми входами разрядов регистра сдвига, инверсный выход последнего разряда которого соединен с входами

П и установки в 0 первого разряда регистра сдвига, о т л и ч а юш и и с я тем, что, с целью получения симметричного выходного сигнала, в него введен установочный триггер, вход установки в 0 которого соединен с входной шиной, а вход установки в 1 . — с инверснцм ВыходОМ последнего разряда регистра сдвига,