Устройство для выбора адреса

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

<1>784814

1

/ (61) Дополнительный к патенту (22) Заявлено 2007 73 (21) 19 4 76 80/18-2 4 (511М. КЛ.З

0 11 С 8/00 (23) приоритет — (32) 21. 07. 72

Государственный комитет

СССР по делам изобретений и открытий (31) 274040 (33) Ср1А

Опубликовано 301180,Бюллетень ¹44 с.

Дата опубликования описания 3011,80 (53) 4Ê 681. 327 (088. 8) (72) Авторы изобретения

Иностранцы

Уоррен Джон Келли и Лоренс Эдвард Ларсон (США) Иностранная фирма

"Интернэшнл Бизнес Машинз Корпорейшн" (CUTA) (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ВЫБОРА АДРЕСА

Изобретение относится к области запоминающих устройств.

Известно устройство для выбора адреса, содержащее ассоциативный блока памяти, адресный блок памяти, блок памяти на магнитных дисках, в котором используется преобразование адресов, по которым производится обращение к адресному блоку памяти (11 .

Недостатком этого устройства явля ется малая скорость работы.

Наиболее близким техническим решением к данному изобретению является устройство для выбора адреса, содержащее регистры, блоки адресной и ассоциативной памяти, логические элементы )2j .

В этом устройстве каждый виртуальный адрес преобразуется в реальный 2() (абсолютный) адрес блока адресной памяти, т.е. виртуальные адреса не используются для непосрЕдственной адресации к блоку адресной памяти. Это приводит к снижению быстродействия 25 устройства.

Целью изобретения является повышение быстродействия устройства.

Поставленная цель достигается тем, что в устройство лля выбора адреса,, 30 содержащее блок оперативной памяти, один из входов которого подключен к выходу первого адресного регистра, второй адресный регистр, выход которого соединен со входом блока ассоци"тивной памяти, первую. группу логических элементов, одни из входов которых подключены к первому выходу блока ассоциативной памяти, а выходы — ко входу логического блока, соединенного со вторым адресным регистром и с блоком оперативной памяти, введены вторан и третья группы логических элементов, информационный регистр и схема сравнения, входы которой подключены к выходам второго адресного регистра и информационного регистра, а выходы— к одним из входов логических элементов второй и третьей групп, выходы которых соединены со входом первого адресного регистра, другие входы логических элементов подключены соответственно к выходам схемы сравнения, второго адресного регистра и второму выходу блока ассоциативной памяти.

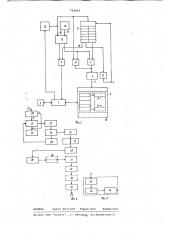

На фиг. 1 изображена структурная схема предложенного устройства, фиг.2 является графической иллнк:трацией процесса адресного прес. р а жвания и

784814 страничной обработки, фиг. 3 иллюстрирует альтернативный метод для установления величины, которая может быть занесена в граничный регистр.

Устройство для выбора адреса (см. фиг. 1) содержит логический блок 1, служащий для обработки данных; блок оперативной памяти 2, блок памяти на магнитных дисках 3, первый адресный регистр 4, служащий для хранения реального адреса и имеющий выход 5, блок ассоциативной памяти б. Блок оперативной памяти 2 содержит зоны 7, 8, называемые таблицей сегментов (7) и таблицами страниц (8-1 — R-N)

Устройство также содержит первую

9, вторую 10 и третью 11 группы логических элементов, блок установки адресов 12, схему сравнения 13, информационный регистр 14, второй адресный регистр 15, служащий для хранения виртуального адреса. Блок оперативной памяти 2 содержит также ядерную зону 16. Входы 17 и 18 схемы сравнения 13 подключены к выходам второго адресного регистра 15 и информационного регистра 14, а один из выходов к одним из входов логических элементов 10 и 11. Одни из входов логическйх элементов 9 соединены с первым выходом 19 блока 6. Другие входы логических элементов 9-11 подключены соответственно к другому выходу схемы сравнения 13, выходу второго адресного регистра 15 и второму выходу блока б. Выходы логических. элементов 10 и 11 соединены со входом первого адресного регистра 4.

Устройство работ<зет следующим образом.

Когда требуется выбрать ячейку из блока 2 (см. фиг.1), то блок 1 передает виртуальный адрес на схему сравнения 13 и блок 6 через регистр 15.

Ре истр 14 хранит величину, равную старшим разрядам (величину страницы) граничного адреса в блоке 2, ниже которого виртуальные и соответствующие им реальные адреса равны. Напри мер, "если "страница равна двум тысячам бит, то нижние двенадцать бит странич ного адреса не хранятся в регистре 14

Сегментная таблица 7 и страничные таблицы с 8-1 по 8-)(находятся в блоке 2. Таблица 7 имеет вход для каж дого из К сегментов виртуальной памяти в блоке 3. Каждый вход имеет адресййй< указатель начала соответствующей страницы таблицы с 8-1 по 8- N.

Каждая страничная таблица имеет множество входов для страниц соответствующего сегмента, который может

Г ть вызван в блок 2 из блока 3. Кажиl!A вход действительной страничной

1аблиц1-.1 содержит в себе указатель

llа>1 <1 >!

Сигнал " одного Ilç выходов схемы

L сравн- 1и>1 13 <: тр< биг>уотс я ног>ически—

11и ">л> меllта!111 1 (>, >."Я тог >, 1то1>1>1 пР<> пустить виртуальный адрес в регистр 4, когда старшие разряды виртуального адреса, подаваемого с блока 1, меньше, чем величина, храня1аяся в регистре

14. Этот же сигнал поступает также в качестве запрещающего сигнала в логические элементы 11 для того, чтобы препятствовать передаче какого нибудь реального адреса из блока 6 в регистр 4, когда преобразование ,не требуется.

Сигналы с логических элементов 9 необходимы для того, чтобы вести поиск таблиц 7 и с 8-1 до 8-Я, когда сигналы прикладываются ко входам этих элементов. Сигналы подаются на входы 5 логических элементов 9 тогда, когда текущий виртуальный адрес в регистре

15 больше или равен граничной величине в регистре 14 и не находится в блоке 6. Блок 12 устанавливает новое

gQ значение виртуального и соответствующего реального адреса в блоке б.

Более подробно работа устройства поясняется с помощью фиг. 2 и 3.

Этапы 20-22 (cM.фиг.2) представляют собой описанную выше работу устройства, Виртуальный адрес, который поступает из блока 1, сравнивается с величиной, хранящейся в регистре 14. Если виртуальный адрес меньше, чем граничный адрес, то блок 2 выбирается виртуальным адресом. Если виртуальный адрес больше или рутвен граничному адресу, то виртуальный адрес используется как аргумент поиска в блоке б. Ассоциативная матрица блока 6 зондируется для того, чтобы определить, содержит ли матрица виртуальный адрес и соответствующий ему реальный адрес. Если виртуальный адрес находится в ассоциативной матрице, то ее реальный ад40 рес используется для выборки блока 2.

Если виртуального адреса нет в ассоциативной матрице, то контроль передается к этапу 23.

На этапах 23, 24 блок 1 передает таблицы 7 и с 8-1 до 8-3 в блок 2, . например, с помощью микропрограммы для того, чтобы определить место требуемого реального адреса в таблицах. Если соответствующая страница имеется в блоке 2, то соответствующий ей реальный адрес будет найден в одной из таблиц с 8-1 до 8-hJ. Действительный бит в страничной таблице используется для того, чтобь> определить, является ли виртуальная страница действительной или нет, то есть, находится ли она в блоке 2 и доступна ли для выборки.

Если страница не является действительной, то контроль передается на этап 25.

В предлагаемом устройстве каждыи виртуальный адрес включает в се>1я сегментную часть, представленнун> самыми старшими разряд<зми адреса, страничную часть, представленну> тц. >м<жу-тОЧН1 1МИ РаЗРЯДаМИ, И Своя;>Pl! х 1" ll >ll!

784814 формула изобретения

Устройство для выбора адреса, содержащее блок оперативной памяти, один из входов которого подклю ен к выходу первого адресного регистра, второй адресный регистр, выход которого соединен со входом блока ассоциативной памяти, первую группу логических элементов, одни из входов которых подключены к первому выходу блока ассоциативной памяти, а выходы — ко входу логического блока, соединенного со с блоком оперативной памяти, о т л и ч а » щ е е с я тем, что, с целью повышецц быстродействия устройства, о«о содержит вторую и третью группы логически: элементов, информационный регистр и схему сравнения, входы которой подкл| чены к выходам второго адресного регистра и информационного регистра,,а выходы — к одним из входов логических элементов второй и третьей групп, выходы которых соединены со входом первого адресного регистра, другие входы логических элементов подключены соответствеццо к выходам схемы сравцсния, второго адресного регистра и второму выходу блока ассоциативной памяти.

Источники информации, принятые во внимание при экспертизе

1. Патент СНА li" 3412382, кл. 340-172. 5, опублик . 1 968.

2. Патент США Р 35 3307 кл. 340-172.5, onvi.лцк. )970 (прототип). битовую часть, представленную млад шими разрядами. Сегментная часть виртуального адреса вместе с сегментной таблицей указателя начала (хранится в регистре, который на фиг. 1-3 не показан) выбирает требуемый вход в таблице 7. Страничная часть виртуального адреса и вход считывания таблицы 7 во время поиска на этапах 23-24 используется для выборки требуемого входа и выбранной таблице с 8-1 до 8-N.

Выбранные табличные данные н одной из таблиц с 8-1 до 8- »4 имеют словарную часть виртуального адреса, связанного, к тому же, с соответствующим реальным адресом.

Если страница действительная, то контроль передается на этап 26, в котором виртуальный адрес и реальный адрес устанавливается в блоке б для контроля наименее недавно используемого адреса (с помощью блока 12). 28

Блок 2 теперь может быть выбран передачей сигналов блока б.

Передача контроля к этапу 25 определяется аппаратурой, обеспечивающей хранение виртуального адреса в ранее 5 определенном месте в ячейках блока 2.

Далее блок 1 выбирает новый дирек:ивный адрес из другой ранее определенной зоны и начинает выполнение нового директивного действия в этапе 27.

На этапе 27 страница в блоке 2 выбирается для восстановления. Передача контроля далее осуществляется на эта-. пах 28 и 29, где табличная директива используется для того, чтобы очистить З (сбросить все битовые позиции до нуля) блок б с целью согласования аннулирования страницы, которая была заменена.

Последующий этап 29 или взаимно исключающий последующий этап 30 пред- 40 ставленного устройства вызывает изменение содержимого регистра 14, Этот процесс может или восстановить ранее определенную величину или сканировать страничные таблицы. 45

Подача сигналов "1" и "0",, необходимая для ввода н требуемую страницу, выполняется н этапе 31 и реальный адрес запоминается на соответствующем входе страничной таблицы и делается О действительным на этапе 30.

Директинный адрес., запоминаемый на этапе 25, повторно загружается в блок 2 с помо»,ью инструкции загрузки и процесс возвращается к этапу 20.

Этапы 32, 33 (см. фиг. 3) представляют собой микропрограммный контур, который начинается при нулевом виртуальном адресе н страничных таблицах и осуществляет установку реального адреса н виртуальный адрес, т.е. ц» реальный адрес считывается и сравнивается с BHpTv

На этапе 34 самая большая величина виртуального адреса, появившаяся н этапах 32 и 33, поступает в регистр

4, как граничный адрес в блоке 2.

В типовом устройстве этапы, представленные позициями 27, 28, 31, 30 и

35 (и, возможно, 36» выполняются методом директивных подпрограмм.

В описанном устройстве в противоположность известному устройству производится преобразование не всех виртуальных адресов. Определенные виртуальные адреса используются для обращения к блоку оперативной памяти непосредственно, без преобразования.

Указанные адреса соответствуют ячейкам памяти, к которым часто обращаются. Обращение к таким ячейкам занимает меньше времени, так как не требуется преобразования адреса. Таким образом, удается получить общее повышение быстродействия, равное

15-25%.