Устройство для сравнения чисел

Иллюстрации

Показать всеРеферат

С АНИ

Союз Советсник

Соцмалистическмк

Республйк (1)785866

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

f61) Дополнительное к авт. свид-ву (22) Заявлено 201178 (23) 2718823/18-24 (5) ) Ah. КП. с присоединением заявки Йо (23) Приоритет

G F 7/02

Государственный комитет

СССР яо делан изобретений и открытий

Опубликовано 07.1280. Бюллетень ¹45

Дата опубликования описания 07.1280 (>3) Ю)(681.325,5 (088.8) (72) Авторы изобретения (73) Заявитель (54) УСТРОЙСТВО ДЛЯ СРАВНЕНИЯ ЧИСЕЛ выражением многовходовыми элементами И и ИЛИ Egg.

Основным недостатком устройства является его сложность при использовании для сравнения многоразрядных кодов.

Целью изобретения является упрощение устройства.

Указанная цель достигается тем, что в устройство для сравнения чисел, содержащее элемент исключающее

ИЛИ, выход которого соединен с первыми входами первого и второго элементов И и с входом элемента НЕ, а выходы первого и второго элементов

И подключены к входам установки в единичное состояние первого и второ" го элементов памяти, выход элемента

HE соединен с входом установки в единичное состояние третьего элемента памяти, введены генератор, счетчик, узлы коммутации, формирователь одиночных импульсов, причем выход генератора соединен с входом счетчика, выход которого подключен к входам первого и второго узлов коммутации, информационные входы которых соединены с информационными входами устройства, выход первого узла коммутации подключен к первому входу

Изобретение относится к автоматике и вычислительной технике и может быть использовано в цифровых системах автоматического управления и регулирования. 5

Известно устройство сравнения кодов, выполненное на логических элементах ИЛИ-НЕ (1). Устройство является сложным и обладает низкой помехозащищенностью. 10

Наиболее близким к изобретению является устройство, выполненное на ячейках исключающее ИЛИ, собранных на элементах И-НЕ и И-ИЛИ-НЕ.

На каждую пару разрядов сравниваемых кодов используется одна двухвходовая ячейка исключающее ИЛИ . На входы этих ячеек подаются сигналы от одноименных разрядов сравниваемых кодов, а выходы всех ячеек подключены к вхо- 20 дам многовходового логического элемента ИЛИ-НЕ. На выходе этого элемента появляется сигнал, соответствующий логической единице; в случае равенства кодов. Кроме того, для вы- 25 деления большего из сравниваемых кодов в каждом разряде использовано по одному элементу 2И. Выходы этих элементов объединены в соответствии с минимизированным математическим 3() В.Д.Вавилов, В.А.Новичихин, С.В.Сарычев и B.A.Шмаров

785866 элемента исключающее ИЛИ и ко второму входу первого элемента И, выход второго узла коммутации соединен со вторыми входами элемента исключающее ИЛИ и второго элемента

И, выход переносов счетчика подключен к первому входу формирователя одиночных импульсов второй вход которого соединен с выходом элемента исключающее ИЛИ, выход которого подключен к входам установки в нулевое состояние счетчика и к управляющим вхо

30 дам элементов памяти.

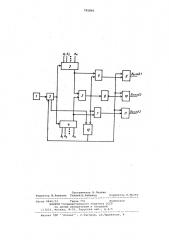

На чертеже представлейа структурная схема устройства.

Устройство содержит генератор l„ счетчик 2, узлы коммутации 3 и 4, эле-1Я мент исключающее ИЛИ 5, элементы

И 6 и 7, элемент HE B,çëåìåíòû памяти

9, 10 и 11 и формирователь 12 одиночных импульсов.

Устройство работает следующим об- © разом.

На входы узлов коммутации 3 и 4 подаются сигналы входных кодов. При включении устройства в работу счетчик

2 подключает поочередно на входы элемента исключающее ИЛИ 5 одноименные разряды сравниваемых кодов, начиная со старших. Если, например, О,, 7 b, то на выходе элемента исключающее ИЛИ и на .выходах элементов И 7 и НЕ 8 нулевые сигналы.В 3 3Q момент перехода сигнала из 0 в 1 на входе формирователя 12 одиночных сигналов на его выходе вырабатывается короткий единичный импульс, который дает разрешение в элементы 35 памяти 9, 10 и 11 на перезапись информации с выходов элементов И б и 7 и HE 8, а счетчик 2 этим же импульсом устанавливается в нуль и, продолжая работу, вновь опрашивает старшие разряды. На выходе 1 будет иметь место логическая единица, свидетельствующая о том, что первое число больше второго.

Если старшие разряды окажутся рав— ными, то счетчик 2 подключит к входу элемента исключающее ИЛИ 5 сле. дующие разряды и т.д. Если после опроса всех разрядов окажется, что коды равны, на выходе элемента исключающее ИЛИ 5 будет иметь место нулевой сигнал, а сигнал из старшего разряда счетчика 2 приведет к выработке короткого импульса на выходе формирователя одиночных импульсов.

Этот импульс перепишет информацию в 55 элементы памяти 9, 10 и 11. Таким образом, на выходе элемента 10 будет иметь место единичный сигнал, а на вь ходах двух других элементов чамяти нулевые.

Если сравнению подлежат коды, изменяющиеся во времени с частотой, меньшей частоты тактового генератора, то устройство будет отслеживать их знаки сравнения в каждый момент времени. предлагаемое устройство предназначается преимущественно для использования в цифровых системах автоматического управления.

Формула изобретения

Устройство для сравнения чисел, содержащее элемент исключающее ИЛИ выход которого соединен с первыми входами первого и второго элементов

И и с входом элемента НЕ, а выходы первого и второго элементов И подключены к входам установки в единичное состояние первого и второго элементов памяти, выход элемента НЕ соединен с входом установки в единичное состояние третьего элемента памяти, о т л и ч а ю щ е е с я тем,что, с целью упрощения устройства,в него введены генератор, счетчик, узлы коммутации, формирователь одиночных импульсов, причем выход генератора соединен с .входом счетчика, выходы которого подключены к входам первого и второго узлов коммутации, информационные входы ко .орых соединены с информационными входами устройства, выход первого узла коммутации подключен к первому входу элемента исключающее ИЛИ и ко второму входу первого элемента И, выход второго узла коммутации соединен со вторыми входами .элемента исключающее ИЛИ и второго элемента И, выход переносов счетчика подключен к первому входу формирователя одиночных импульсов, второй вход которого соединен с выходом элемента исКлючающее ИЛИ, выход которого подключен к входам установки в нулевое состояние счетчика и к управляющим входам элементов памяти.

Источники информации, принятые во внимание при экспертизе

1. Слежановский О.В. Устройство унифицированной блочной системы регулирования дискретного типа. И., "Энергия", 1975, с.49, рис. 15-2.

2. Авторское свидетельство СССР

Р 588542, кл.G F 7/04, 21.02.1975 (прототип).

Составитель В.Яелкин

Редактор Ж.Рожкова Техред A,Áàáèíåö

Корректор И.Муска

Филиал ППП Патент, r.Óæãîðoä, ул.Проектная, 4

Заказ 8846/53 Тираж 7 51 Подписное

ВНИИХИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5