Синтезатор частот

Иллюстрации

Показать всеРеферат

Союз Советскии

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 10.01.79 (21)2714182/18-09 (1)М с присоединением заявки М (23) Приоритет

H 03 B 21/02

Государственный комитет

СССР но делам изобретений н открытий

Опубликовано 071280 Бюллетень М9 45

Дата опубликования описания 071280 (53) УДК б 21 .373.42 (088.8) (72) Авторы изобретения

И. П. Усачев, Б.И.Шлянкенич, Н.М.Корецкий и A.Е.Богданов (71) Заявитель (54) СИНТЕЗАТОР ЧАСТОТ

Изобретение относится к радиотех- нике и может использонаться в приемопередающих и контрольно-измерительных устройствах.

Известен синтезатор частот, содер- жащий последовательно соединенные опорный генератор, делитель частоты с фиксированным коэффициентом деления, фазовый детектор, фильтр нижних частот (ФНЧ), управляемый генератор и де-1О литель частоты с переменным коэффициентом деления, сигнальный выход которого подключен к другому входу фазового детектора, а между другим выходом делителя частоты с фиксирован- 35 ным коэффициентом деления и другим входом управляемого генератора включены последовательно соединенные цифровой компаратор частоты, счетчик и

Цифроаналоговый преобразователь (ЦАП).20 при этом поразрядные управляющие входы делителя частоты, с переменным коэффициентом деления соединены с соответствующими поразрядными ныходами блока управления 1).

Однако из в ест ный синтез атор ч астот обладает невысоким быстродействием.

Цель изобретеия — повышение быст .родействия. 30

Для этого в известном синтезаторе частот между поразрядными выходами блока управления и другим входом цифрового компаратора частоты введены последовательно соединенные блок управления цифровым умножителем.частоты и цифровой умножитель частоты, первый и второй сигнальные входы которого соединены соответственно с сигнальным и кодовым выходами делителя частоты с переменным коэффициентом деления.

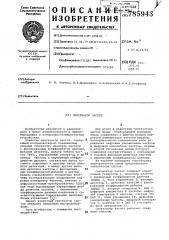

На чертеже приведена структурная электрическая схема предложенного синтезатора частот.

Синтезатор частот содержит управ ляемый генератор 1, делитель частоты с переменным коэффициентом деления (ДПКД) 2, блок управления 3, фазовый детектор 4, делитель частоты с фиксированным коэффициентом деления (ДФКД) 5, опорный генератор 6, ФНЧ 7, цифровой умножитель 8 частоты, цифроной компаратор 9 частоты, счетчик 10, ЦАП 11, блок управления 12, цифровым умножителем частоты. Цифровой компаратор 9, счетчик 10 и II@II 11 составляют блок автопоиска 13.

Синтезатор частот работает следу ющим образом.

785943

На фазовом детекторе 4 сравнивает,ся частота управляемого генератора 1, поделенная ДПКД 2 на коэффициент деления N с частотой f> опорного .генератора 6, поделенной ДФКД 5 на

1 коэффициент деления М. В режиме синхронизма эти частоты равны: f„)V =fо(М. о

На выходе фазового детектора 4 образуется постоянное управляющее напряжение, которое через ФНЧ 7 поступает на один из входов управляемого гене- ратора 1, на второй вход которого поступает постоянное напряжение с выхода блока автопоиска 13.

Это напряжение формируется на выходе ЦАП 11 и соответствует определенному состоянию счетчика 10 в двоич- 35 ном коде. Состояние счетчика 10 определяется тем числом импульсов разностной частоты, которое поступает на его вход с выхода цифрового компаратора

9 до момента установления синхронизма.gp

B режиме синхронизма на входы цифрового компаратора 9 поступают одинаковые частоты: одна частота — с выхода ДПКД 2 через цифровой умножитель

8, где она умножается на 2, и равная к

1,(Н ° 2", а вторая — с выхода ДФКД 5, равная f (М.2", где k-=1, 2, 3, Ф т. е. на входы цифрового компаратора

9 поступают последовательности импульсов с частотами1„(М 2" и1 JN 2К.

Поскольку поступающие в режиме синхронизма на входы цифрового компаратора 9 последовательности импульсов равны по частоте и распределение импульсов в них равномерное, то меж- . ду двумя импульсами одной последова- З5 тельности проходит только один импульс другой последовательности, т, е. они чередуются во времени. В этом случае на выходе цифрового компаратора 9 нет разностных импульсов 4р и счетчик 10 сохраняет свое состояние без изменения.

РавномерноСть распределения импульсов на выходе цифрового умножителя 8 обеспечивается блоком управ,пения 12, сопряженным с блоком управления 3.

На выходах блока управления 12 формируется двоичный код числа, сдвинутого на одну вторую относительно кода, которым управляется ДПКД 2. По- о скольку блок управления 12 сопряжен с блоком управления 3, то при изменении коэффициента деления ДПКД 2.изменяются соответственно и сигналы уп-: равления цифровым умножителем 8. 55

На выходе последнего всегда формируетжя последовательность импульсов, сдвинутая относительно последовательности импульсов с выхода ДПКД

2 на 180 . Таким образом, получается щ непрерывное слежение за равномерностЬю расстановки импульсов на выходе цифрового умножителя 8 при любых изменениях коэффициентов деления

ДПКД 2. 65

При нарушении синхронизма на выходе цифрового компаратора 9 формируется разностная частота импульсов, которая в 2к раз выше разностной частоты (частоты биений) на выходе фазового детектора 4. Эта разностная частота поступает на вход счетчика

10, который управляет работои ЦАП 11„

В результате на выходе ЦАП 11 образуется ступенчатсе напряжение, воздействующее на управляющий вход управляемого генератора 1 так, чтобы уменьшить возникшее рассогласование по частоте.

Использование предложенного синтезатора частот позволяет получить мак— симально возможное быстродействие по цепи грубой автоподстройки, что приводит к значительному уменьшению вре-, мени перехода с одной частоты на другую. Это один из основных параметров всех синтезаторов частот и особенно тех которые используются в устрой—

> ствах, где для улучшения помехозащищенности несущая частота все время меняетсч по какому †ли закону.

Формула изобретения

Синтезатор частот, содержащий последовательно соединенные опорный генератор, делитель частоты с фиксированным коэффициентом деления, фазовый детектор, фильтр нижних частот, управляемый генератор и делитель частоты с переменным коэффициентом деления, сигнальный выход которого подключен к другому входу фазового детектора, а между другим выходом делителя частоты с фиксированным коэффициентом деления и другим входом управляемого генератора включены последовательно соединенные цифровой компаратор частоты, счетчик и цифроаналоговый преобразователь, при этом поразрядные управляющие входы делителя частоты с переменным коэффициентом деления соединены с соответствующими поразрядными выходами блока управления, отличающийся тем, что, с целью повышения быстродействия, между поразрядными выходами блока управления и другим входом цифрового компаратора частоты введены последовательно соединенные блок управления цифровым умножителем частоты и цифроыой умножитель частоты, первый и второй сигнальные входы которого соединены соответственно с сигнальным и кодовым выходами делителя частоты с переменным коэффициентом деления.

Источники информации, принятые во внимание при экспертизе

1. Патент США М 3401353, кл кл. 331-11, опублик. 1968 (прототип) 785 943

Составитель Г. Теплова

Редактор С. Титова Техред Ж.Кастелевич Корректор 8 сутяга

Заказ 8859/56 Тираж 995 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал IIIIII "Патент", г. Ужгород, ул. Проектная, 4