Триггер

Иллюстрации

Показать всеРеферат

Н1С.. ОКЭ.НЬЯИ, р1" 1." . р, ".ДВ;Я 11; АШНАЯ

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ н„ о.. чэ. l4FA

< 785961

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (6I ) Дополнительное к «вт. свил-ву (22) Заявлено 08.01.79 (21) 2709421/18-21 (51)М, Кл.

Н 03 К 3/286 с присоединением заявки ¹

Гвсударстввнный каннтвт (28) Приоритет ао делам нзобретений

H отнрытнй

Опубликовано 07.12.80. Бюллетень № 45

Дата опубликования описания 07.12.80 (53 ) УД К 621.375. .083 (088.8) (72) Автор изобретения

Г. С. Брайловский (7I) Заявитель (54) ТРИГГЕР

Изобретение относится к радиоэлектронике, может быть использовано в вычислительной, импульсной и измерительной технике.

Известен триггер, построенный на восьми логических элементах И вЂ” НЕ (ИЛИ вЂ” HE), содержащий основной и вспомогательный RSтриггеры (1). В этом трнггерном устройстве основной RS-триггер переключается по фронту (срезу), а вспомогательный RS-триггер переключается по срезу.

Известен также синхронный JK-триггер, построенный на восьми логических элементах

И вЂ”,НЕ по схеме MS с запрещающими связями (2) .

Известные устройства обладают следующими недостатками:

1. Низкое быстродействие при работе в режиме управления. Так, для триггера, построенного на элементах И вЂ” HE, минимальная длительность паузы входных импульсов определяется временем последовательного переключения четырех логических элементов.

2. Низкая нагруэочная способность, так как выходы триггера имеют по две внутренние погрузки.

3, Невозможность использования в асинхронных распределительных схемах, построенных

5 на тех же логических элементах. что и сам триггер, так как на время переключения одного логического элемента на инверсном и прямом выходах триггера одновременно действу10 ют два сигнала логической единицы, если триггер построен иа логических элементах

И вЂ” НЕ или логического нуля, если триггер построен на логических элементах ИЛИ вЂ” НЕ.

Это сужает функциональные воэможности

15 устройства.

Цель изобретения — повышение быстродействия, увеличение нагрузочкой способности и расширение функциональных возможностей устройства.

Для этого в устройстве, содержащем восемь логических элементов И вЂ” НЕ (ИЛИ вЂ” HE), выход предыдущего элемента соединен с первым входом последующего. выход восьмого элемента соединен с первым входом первого

785961 4

2(6), в логический нуль и 3(7) в логическую единицу.

3 элемента, второй вход которого подключен к первому входу устройства, а выход соединен со вторым входом третьего элемента, выход второго элемента соединен со вторым входом шестого элемента, выход которого подключен ко второму входу второго элемента, второй вход седьмого элемента подключен к выходу пятого элемента, второй вход которого подключен ко второму входу устройства, выходы четвертого и восьмого элементов соответственно подключены к первому и второму выходам устройства, а выходы первого и пятого Элементов соответственно .соединены со вторыми входами восьмого и четвертого элементов.

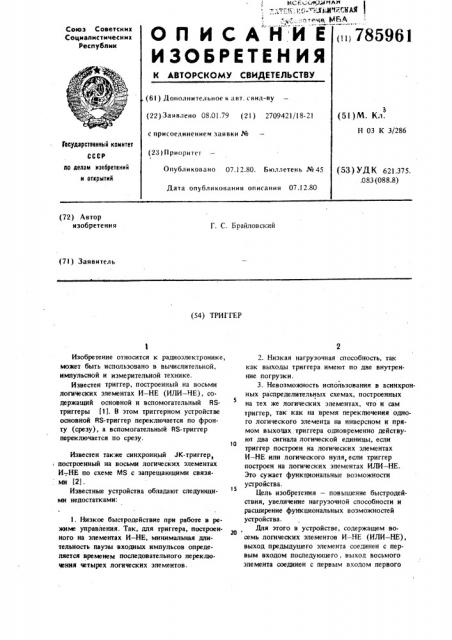

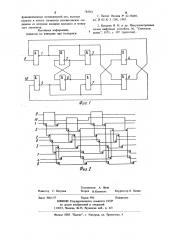

На фиг. 1 изображена принципиальная схема предлагаемого устройства, построенного на логи1 ческих элементах И вЂ” HE; на фиг. 2 — временная диаграмма, поясняющая его работу.

Триггер (фиг. 1) содержит логические элементы И вЂ” НЕ 1-8 и имеет входы 9 и 10.

Выход элемента 1 соединен с входами элементов 2„3 и 8, выход элемента 2 — с входами элементов 3 и 6, выход элемента 3 — с входом элемента 4, выход элемента 4 — с входом элемента 5, выход элемента 5 — с входами элементов 6, 7 и 4, выход элемента 6 — с входами элементов 2 и 7, выход элемента 7 с-входом элемента 8, выход элемента 8 — с входом элемента 1, вход триггера 9 — с входом элемента 1, вход триггера 10 -- с входом элемента 5.

При сигнале логической единицы на выходе

8(4) переключение входного сигнала 9 (10) из логического нуля в логическую единицу вызывает перекшочение элемента 1(5) в логический нуль. После этого переключается элемент 2(6) в логическую единицу, затем элемент 6 (2) в логический нуль и элемент 7(3) в логическую единицу.

Переключение сигнала 9 (10) из логической единицы в логический нуль вызывает переключение элемента 1(5) в логическую единицу.

После этого одновременно переключаются элементы 3 и 8 (7 и 4) в логический нуль, а затем элемент 4(8) переключается в логическую единицу, При этом состояние входа

10(9) не влияет на работу триггера, пока на выходе 4(8) действует сигнал логического нуля. Если в момент переключения элемента

4(8) в логическую единицу на входе 10(9) поддерживается сигнал логического нуля, то на том переключения элементов триггера заканчиваются. И если на входе 10(9) действует а сигнал логической единицы, то переключение элемента 4 (8) в логическую единицу вызовет переключение элемента 5(1) в логический нуль. После этого последовательно переключаются элементы 6(2) в логическую единицу

Если соединить входы 9 и 10 между собой (т.е. подать на входы 9 и 10 одинаковые сигна5 лы), то триггер будет работать в счетном режиме.

Триггер, построенный на логических элементах ИЛИ вЂ” НЕ, будет работать аналогично.

gp Как видно из временной диаграммы (фиг.2), минимальная длительность паузы входных импульсов для предлагаемого устройства, построенного на логических элементах И вЂ” ЧЕ и работающего в режиме управления, определяется временем переключения только трех логических элементов (1, 3, 4 или 5, 7, 8) вместо четырех для прототипа.

Переключения элементов 4 и 8 проходят через промежуточное состояние, при котором

2О на выходах оооих элементов 4 и 8 действуют сигналы логического нуля, вместо логических единиц для выходных сигналов прототипа. Это свойство позволяет использовать предлагаемый триггер в асинхронных распределительных схемах, построенных на тех же логических элементах, что и сам триггер.

Выходы элементов 4 и 8 предлагаемого устройства имеют только по одной внутренней нагрузке вместо двух у прототипа. Это позволит

30 нагрузить выходы предлагаемого триггера на один дополнительный вход по сравнению с прототипом.

Таким образом, предлагаемый триггер позволяет повысить быстродействие, нагрузочную

35 способность и расширить функциональные возможности его.

Формула изобретения

Триггер, содержащий восемь логических элементов И вЂ” НЕ (ИЛИ вЂ” НЕ), выход предыдущего элемента соединен с первым входом последую. щего, выход восьмого элемента соединен с первым входом первого элемента, второй вход которого. подключен к первому входу устройства, а выход соединен со вторым входом третьего элемента, выход второго элемента соединен со вторым входом шестого элемента, выход которого подключен ко второму входу второго элемента, второй вход седьмого элемента подключен к выходу пятого элемента, второй вход которого подключен ко второму входу устройства, выходы четвертого и восьмого элементов соответственно подключены к первому и второму выходам устройства, отличающийся тем, что, с целью повышения быстродействия, увеличения нагрузочной способности и расширения

785961

Составитель А. Янов

ТехРед H,Êoâàëåâà КоРРектоР О. Билак

Редактор Г. Петрова

Заказ 8861/57 Тираж 995 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб,, д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4 функциональных возможностей его, выходы ,первого и пятого элементов соответственно соединены со вторыми входами восьмого и четвертого элементов.

Источники и нформации, принятые во внимание при экспертизе

l. Патент Японии Х 42-58405, кл. Н 03 К 3, 286, 1967.

2. Букреев И. Н. и др. Микроэлектронные схемы цифровых устройств, М., "Советское. радио", 1975, с. 107 (прототип).