Декодирующее устройство

Иллюстрации

Показать всеРеферат

ОП ЙСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советскык

Соцыалыстыческие

Реслублык

II II 785993 (6! ) Дополнительное к ввт. свнд-ву— (22) Заявлено 01.11.78 (2! ) 2680898/18-09 (5l)M. Кл.

Н 03 К 13/34 //

Н 04 L 1/10 с присоединением заявки Ж

Государатееиный комитет (23) Приоритет оо делам изобретений н открытий

Опубликовано 07.12.80. Бюллетень М 45

Дата опубликования описания 07.12.80 (53) УДК 621.394..14(088.8) (72) Авторы изобретения

P. И. Юргенсон, A. С. Ибрагимов и A. В. Косолапов

Ленинградский ордена Ленина электротехнический инстигут им. B. И. Ульянова (Ленина) (7l) Заявитель (54) ЛЕКОДИРУ)ОШЕЕ УСТРОЙСТВО

Изобретение относится к радиотехнике и может быть использовачо в устройствах передачи и обработки информации.

Известно декодирующее устройство, содержащее блок фильтров, выходы которо5 го подключены ко входам блока запрета и блока синхронизации, а также блок элементов ИЛИ и последовательно соединенные блок памяти и декодер jl).

Однако известное устройство имеет низкую помехоустойчивость и небольшую скорость передачи информации.

Llem изобретения — повышение помехоустойчивости и скорости передачи информациии. 15

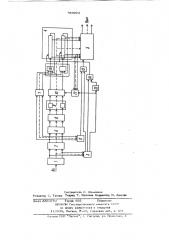

Зля этого в декодируюшее устройство, содержащее блок фильтров, выходы которого подключе»ы ко входам блока запрета и блока с»нхроннзаиии, а также блок элементов l,"ill » последовательно соединенные баoK памят» » декодер, введены счетчик контре»я о»>»бок, первый преобразователь, последовательно соед»ненные второй преобря;.сват IIb, IIo rpy1111»posaния сигналов, анализатор и кодер, а также два элемента И» последовательно соединенные генератор сигнала опроса и алемент ИЛИ, выход которого подключен к тактовому входу блока памяти, при этом выходы блока запрета подключены ко входам счетчика контроля ошибок, первого второго преобразователей, причем выходы первого преобразова еля подключены к первым входам блока элементов ИЛИ, а выходы кодера через»торые входы блока элементов ИЛИ подключены ко входам блока памяти, соответствунлиие выходы которого подключены к третьим входам блока элементов ИЛИ и входам первого алемента И, выход которого»одключен к управляющему входу кодера, в Ixoa "четчика контроля ошибок подключен к перво— му входу второго элема»т, ll, выход которого подключен к разре»ц1кшему входу декодера, а первый, IIòIl.т»» третий выходы блока си1лронизац»» подключены соответственно к вторым входам BtopoI элемента И и элемента ИЛИ и к объеди3 785993 ф пенным входам первого элемента И и равляюший вход кодера 10, который прс генератора сигнала опроса. изводит коррекцию искаженного сигнальНа чертеже изображена структурная ного признака, После т тактов генератоэлектрическая схема предложенного уст- ра 13 в блоке 4 происходит восстановлеро йства.

5 ние информации после чего блок 3 формиПредложенное устройство содержит блок рует ня первом выходе импульс, который

1 фильтров, блок 2 запрета, блок 3 син- через второй элемент И 15 поступает на хронизации, блок 4 амяти, декодер 5, преобразователи 6 и 7, блок 8 группиро- сигналу осуществляется декодирование при= вания сигналов, анализатор 9, кодер 10» 10 пятой комбинации. счетчик 11 контроля ошибок, первый эле- Более подробно работу предложенного мент И 12, генератор 13 сигнала опроса, устройства можно пояснить на примере элемент ИЛИ 14, второй элемент И 15, трехэпементного кода (w =3) с числом блок 16 элементов ИЛИ, сигнальных признаков (основанием кода)

ПРедложенное ycTPOAcTÂÎ Работает сле- 15 К=4. Число кодовых комбин,„ий опредедуюшим образом. ляется по формуле

На вход 1 поступает кодовая комбинация, подлежащая декодированию. Элементы кодовой комбинации выделяются блоком 1 и поступают на вход блоков 2 и 3. С (К-1) выходов блока 2 импульсы преобразователем 7 преобразуются в двоичный код с номером принятого сигнального признака и через блок 16 записываются в блок 4, В преобразователе 6 каждый импульс сигнального признака, за исключением К-го, преобразуется в числоимпульсный код с номером сигнального признака.

Импульс К-го сигнального признака по до- 30 полнительным (К-1) выходам преобразователя 6 преобразуется одновременно в числоимпульсный код с числом импульсов, пропорциональным номеру выхода. Импульсы на 2 (К-1) выходах преобразователя

6 с помощью блока 8 объединяются и поступают на (К-1) входы анализатора 9, который осуществляет проверку по модулю (K-1) на всех (К-1) входах. Результат проверок кодируется кодером 10 в двоичный код обнаруженного искаженного одиночного сигнального признака. B зависимости от кода по сигналу с первого элемента И 12 осуществляется восстановление искаженного элемента в блоке 4. В 45 случае уничтожения двух или более сигнальных признаков кода срабатывает счетчик 11 и не разрешает прохождение импульса с блока 3 на разрешающий вход декодера 5. После окончания приема кода блок: 3 запускает генератор 13, который через элемент ИЛИ 14 осуществляет тактирование блока 4. В случае одиночной ошибки в коде в блоке 4 находится значение 0 сигнального признака, которое будет обнаружено первым элементов И 12 на очередном тактовом импульсе генератора 13. В этом случае импульс с выхода первого элемента И 12 поступает на уп д=(1 - т) =(4.-.1) =9. где Х,), Х --значение сигнального признака на Р позициях, ® — сумма по модулю (К-1).

Использование дополнительной позиции увеличивает кодовое расстояние до д= 2.

Нулевой сигнальный признак заменяется ня, К-й сигнальный признак, что повышает кодовое расстояние до Ol=- 4. 11ри этом код позволяет обнаружить две ошибHH H одну HG HHx исправить. TBKHM образом, при К 4, и = 3, M = (К-1)

>т- т

= 3 =- 9 имеем: х„х х х xъ

1. 0 0 0 3 3 3

2. 0 1 2

3. 0 2 1

3 1 2

3 2 1

1 0 2 1 3 2

1 1 1С: 1 1 1

1 2 3

6, 1 2 0

7 ° 2 0 1 2 3 1

8. 2 1 0 2 1 3

9. 2 2 2

2 2 2

Г!ринимаемый код разбивается HB (К-1)=3 группы кодов. В первую группу входят сигнальные признаки (1, 2) при

Метод построения кода заключается в том, что строится избыточный (К-1) = 3 основной код ня (тт — 1) = 2 позициях. Кодовое расстояние равно cil = 1. Затем ня дополнительной (третьей) контрольной позиции устанавливаются символы с помо)пью проверки:

Х О - Х О+X)-0

78.iOe3

5 этом признак (3) заменяется нулем. Во вто(>ук> группу входят признаки (3,. ), я признак (1) заменяется нулем. В третью группу входят признаки (3,1), и признак (2) заменяется нулем. Тогда имеем:

333 чить увеличение скорости и .дачи информации.

Формула изобретения

3 1 2

321

1 3 2

Т"

0,3,2,3,1

333 333

0,1,2

000

012 02 3 10

0 2 1

320 301

1 02 032 130 20

Результат проверок кодовых групп по модулю (К-1) следующий

25 зох

001 j 00 201

X8X®X Ô0 X®X ;, 6 0 XÞ éX = 0

На основании результата проверок может быть сделан однозначный вывод об искаженном одиночном сигнальном признаке, что и положено в основу принципа коррекции одиночной ошибки.

При одновременном приходе двух сигнальных признаков на одной позиции кода, одним из которых является помеха, я другим — рабочий сигнал, на выходе блока 2 будет сформирован нулевой сигнальный признак, что соответствует одиночной ошибке подавления, Использование К-ичных корректирующих колов позволяет испольэовать линии и каналы, где число сигнальных признаков боль- 45 ше двух. В свою очередь, К-ичные колы позволяют существенно расширить множество передаваемых кодовых комбаниций или при том же множестве комбинаций обеспеЛекодируюшее устройство, содержащее блок фильтров, выходы которого подключены ко входам блока запрета и блока синхронизации, а также блок элементов ИЛИ и последовательно соединенные блок памяти и декодер, о т л и ч я ю щ е е с я тем, что, с целью повьпиения помехоустойчивости и скорости передачи информации, введены счетчик контроля ошибок, первый преобразователь, последовательно соединенные второй преобразователь, блок группирования сигналов, анализатор и кодер, а также два элемента И и последовательно соединенные генератор сигналя опроса и элемента ИЛИ, выход которого подключен к тактовому входу блока памяти, при этом выходы блока запретя полключены ко входам счетчика контроля ошибок, первого и второго преобразователей, причем выходы первого преобразователя подключены к первым входам блока элементов ИЛИ, а выходы кодера через вторые входы блскя элементов ИЛИ подключены ко входам блока памяти, соответствующие выходы которого подключены к третьим входам блока элементов ИЛИ и входам первого элемента И, BblxoEj которого подключен к управляющему входу кодера, лыхоц счетчика контроля ошибок подключен к первому входу второго элемента И, выход которого подключен к разрешающему входу декодера, а первый, второй и третий выходы блока синхронизации подключены соответственно к вторым входам второго элемента И и элемента IIIII! и к объединенным входам первого элемента И и генератора сигнала опроса.

Источники информации, принятые во внимание при экспертизе

1. Юргенсон P. И. Помехоустойчивбсть цифровых систем передачи телемехл нпческой информации. Л., "Энергия", 1 974, с. 188 (прототип).

785983

Составитель И. Шамонина

Редактор С, Титова Техред Т. Маточка Корректор М. Демчик

Заказ 886 3/59 Тираж 995 Подпис но»

ВНИИ ПИ Государственного комитета ССС> по делам изобретений и открытий

113035, Москва, Ж-З5, i аушская наб., и. 4/5

С>нлнал ППП "Патент, r. Ужгород, ул. Проектная, 4