Делитель частоты следования импульсов с переменным коэффициентом деления

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТО РСХОМУ СВИДЕТЕЛЬСТВУ

Союз Советскик

Социалистических

Республик

Н 03 К 23/00

Гесударственный комитет

СССР (53) УДК 621.374..44 (088.8) Опубликовано 07.12.80. Бюллетень № 45

Дата опубликования описания 15.12.80 пе делам изобретений н открытий " «м», С. Ш. Бикбаев, Е. И. Верещак, П. Н. Смирнов, Е. Н. Шмелева и С. М. Филашов (72) Авторы изобретения (71) Заявитель (54) ДЕЛИТЕЛЬ ЧАСТОТЫ СЛЕДОВАНИЯ ИМПУЛЬСОВ

С ПЕРЕМЕННЫМ КОЭФФИЦИЕНТОМ ДЕЛЕНИЯ

Изобретение относится к импульсной технике и может использоваться в автоматике и вычислительной технике.

Известен делитель частоты следования импульсов, содержащий генератор импульсов, программный блок, первый выход которого подключен к входу дешифратора дробного коэффициента, а остальные выходы— к одному из входов цифрового компаратора, другие входы которого соединены с выходами счетчика целого коэффициента, а выход — с первым входом переключателя.

Однако данное устройство недостаточно надежно в работе при повышении частоты входного сигнала.

Наиболее близким по технической сущности к изобретению является делитель частоты следования импульсов с программным заданием дробного коэффициента деления, содержащий генератор импульсов, программный блок, первый выход которого подключен к входу дешифратора дробного коэффициента, а остальные выходы — к одному из входов цифрового компаратора, другие входы которого соединены с выходами счетчика целого коэффициента, а выход — с перBbIM входом переключателя, фазосдвигаю2 щий элемент, элемент ИЛИ, счетчик дробного коэффициента, дешифратор частот и вентили выделения целевого импульса, первые входы которых -через фазосдвигающий элемент соединены с выходом генератора импульсов, вторые входы — с выходами дешифратора частот, а выходы — с входами элемента ИЛИ, выход которого подключен к счетному. входу счетчика целого коэффициента и ко второму входу переключателя, выход которого соединен с входом обнуления

10 счетчика целого коэффициента и с одним из входов счетчика дробного коэффициента, другой вход которого подключен к выходу дешифратора дробного коэффициента, а выход — к входу дешифратора частот, причем выход цифрового компаратора подключен к входу программного блока

Недостатком этого устройства является невысокая надежность его при увеличении входной частоты следования импульсов.

Целью изобретения является расширение диапазона рабочих частот при одновременном повышении надежности делителя.

Эта цель достигается тем, что в делитель частоты следования импульсов, содержащий фазосдвигающий элемент, вход которого сое786010 динен с выходом генератора импульсов, блок переключения частот, первая группа входов которого соединена с выходами фазосдвигающего элемента, управляющий вход — с выходом дешифратора, вход которого соединен с выходом дробной части программного блока, и счетчик целого коэффициента, введены сдвигающий регистр, дополнительный блок переключения частот, первая группа входов которого объединена с первой группой входов блока переключения частот, управляющий вход — с управляющим входом блока перек,.ючения частот, а выход соединен с первым входом сдвигающего регистра, блок переноса, блок совпадения, инвертор, триггер, выход которого подключен через элемент совпадения, второй вход которого подключен к выxqpy блока переключения частот, соединен со счетчным входом счетчика целого коэффициента, входы записей которого через блок переноса соединены с выходами целой части программного блока, и дополнительный дешифратор, управляющий вход которого через инвертор соединен с выходом блока переключения частот, входы разрядов —— с выходами разрядов счетчика целого коэффициента, а выход — со вторым входом сдвкгающего регистра, выход первого разряд". которого соединен с первым входом триггера и управляющим входом блока перекоса. выход второго разряда — с дополнительным входом блока переключения частот, выход теретьего разряда — со вторым входом TppJгера, выход четвертого разряда — с допол— нительным вхсдом дополнительного блока переключения частот.

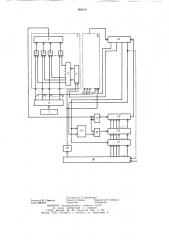

На чертеже изображена структурная электрическая схема делителя частоты следования импульсов с переменным коэффициентом времени.

Оно содержит генератор 1 импульсов, фазосдвигающий элемент 2, блок 3 переключения частот, счетчик 4 дробного коэффициента блока переключения частот, дешифратор

5 дробного коэффициента блока переключения частот, элемент И 6 блока переключения частот, элемент ИЛИ 7 блока переключения частот, дополнительный блок 8 переключения частот, программнь|й блок 9, дешифратор 10 дробного коэффициента., блок

11 переноса, счетчик 12 целого коэффициента, дополнительный дешифратор 13 конечного состояния счетчика целого коэффициен та, сдвигающий регистр 14, триггер 15, элемент 16 совпадения, инвертор 17.

Устройство работает следующим образом.

Импульсы генератора 1 поступают на фазосдвигающий элемент 2, где преобразуются в импульсы Fq, Fq,...Ft,...F, частоты которых равны частоте F генератора импульсов, а фазы сдвинуты друг относительно друга на величину Л Р; = — ".

Импульсы Fo, Fj,...F„-,... Р„,поступают на элементы блока 3 и дополнительного блока.

На выход элемента 7 блока 3 проходит только та последовательность, которая поступает на элемент 6, открытый сигналом дешифратора 5, состояние которого задается счетчиком 4. Счетчик 4 может работать в М-!-1 режимах, каждый из которых соответствует своему значению дробной части коэффициента деления и задается дешифратором

10.Например, для случая М = 5, т.е. для случая шести входов фазосдвигающего элемента, может быть шесть режимов работы.

В первом режиме счетчик 4 закрыт по счетному входу и не меняет своего состояния. В этом случае m=0, m — дробная часть коэффициента деления. Во втором режиме +1, т.е. с приходом каждого счетного импульса число в счетчике увеличивается на единицу, что соответствует m=1/6. Третий режим

+2, т.е. с приходом каждого счетного импульса содержимое счетчика увеличивается на два, что соответствует оп=2/6, и так Ilo режима шесть, который может быть образован как +5 или как - 1, т.е. либо к содержимому счетчика добавляется пять, либо содержимое уменьшается на единицу, при этом

m== )г °

Импульсы с элемента 7 блока 3 поступают на вход элемента 16 и далее на счетчик. 12 и через инвертор 17 поступают на вход дополнительного дешифратора 13. Имцульсь. с элемента ? доголнительного блока 8 поступают на вход, сдвигающего регистра 14. На входы записи счетчика 12 через блок 1! поступает код целой части, задаваемый программным блоком 9. Код дробной части коэффициента деления поступает из программного блока 9 на дешифратор

10. Трипер 15 в зависимости от состояния устройства разрешает или запрещает прохождение импульсов на счетный вход счетчика 12.

В исходном состоянии сдвигающий регистр 14 обнулен, триггер 15 установлен в состояние, разрешающее прохождение счетных импульсов через блок 16 на счетный вход счетчика 12. В счетчик 12 записано число К, равное: ДPK = (К-Е) п.ой(")-$, где "."-число разрядов в счетчике;

Е -заданный коэффициент деления (целая часть);

" ь-выбранное конечное состояние, задаваемое дешифратором счетчика целого коэффициента.

Счетчик 4 блока 3 и дополнительного блска 8 установлены в одинаковое состояние, т.е. импульсы на счетный вход счетчика 12 и на сдвигающий вход сдвигающего регистра 14 идут с одинаковой фазой.

После установления счетчика 12 в состояние, определяемое дополнительным дешифратором 13, сигнал на выходе дешифра786010

Формула изобретения тора появится только после окончания счетного импульса, по его «паузе»,так как управляющий вход дополнительного дешифратора соединен с шиной импульсов, поступающих на счетный вход счетчика, через инвертор. В этом случае записи «1» в первый разряд сдвигающего регистра по этому такту не произойдет. Записи «1» в первый разряд сдвигающего регистра по этому такту не произойдет по следующему счетному импульсу, так как фазы импульсов с выходов блоков 3 и 8 совпадают. Продвижение «1» по сдвигающему регистру 14 вызывает следующие переключения в устройстве.

Сигнал с первого разряда сдвигающего регистра 14 переключает триггер 15 в состояние, запрещающее прохождение счетных импульсов на вход счетчика 12 и разрешает перепись целой части коэффициента деления из программнного блока 9 через блок 11 в счетчик 12.

Сигнал со второго разряда сдвигающего регистра 14 поступает на счетчик 4 блока 3, что вызывает его переключение в соответствии с режимом работы, задаваемым программным блоком 9 через дешифратор 10, что определяет дробную часть коэффициента деления.

Сигнал с третьего разряда регистра 14 поступает на вход триггера 15 и вызывает его переключение в состояние, разрешающее прохождение счетных импульсов на вход счетчика 12.

Сигнал с четвертого разряда сдвигающего регистра 14 поступает на счетный вход счетчика 4 блока 8 и переводит его в то же состояние, что счетчик блока 3, т.е. сигналы, подаваемые на счетный вход счетчика 12 и на сдвигающий вход регистра 14, с0впадают по фазе.

В дальнейшем цикл работы устройства повторяется.

Работа программного блока 9 может осуществляться по командам, подаваемым, например, с третьего разряда регистра 14 или по внешним командам.

Разделение устройства на две взаимосвязанные части позволяет разделить число необходимых для работы устройства последо1О

is

25 зе

35 аю вательно включенных элементов также на две части, что позволяет уменьшить минимально необходимый для надежной работы интервал времени, т.е. повысить максимальную рабочую частоту.

Делитель частоты следования импульсов с переменным коэффициентом деления, содержащий фазосдвигающий элемент, вход которого соединен с выходом генератора импульсов, блок переключения частот, первая группа входов которого соединена с выходами фазосдвигающего элемента, управляющий вход — с выходом дешифратора, вход которого соединен с выходом дробной части программного блока, и счетчик целого коэффициента, отличающийся тем, что, с целью расширения диапазона рабочих частот при одновременном повышении надежности, в него введены сдвигающий регистр, дополнительный блок переключения частот, первая группа входов которого объединена с первой группой входов блока переключения частот, управляющий вход — с управляющим входом блока переключения, частот, а выход соединен с первым входом сдвигающего регистра, блок переноса, элемент совпадения, инв ртор, триггер, выход которого через элемент совпадения, второй вход которого подключен к выходу блока переключения частот, соединен со счетным входом счетчика целого коэффициента, входы записи которого через блок переноса соединены с выходами целой части программного блока и дополнительный дешифратор, управляющий вход которого через инвертор соединен с выходом блока переключения частот, входы разрядов — с выходами разрядов счетчика целого коэффициента, а выход — со вторым входом сдвигающего регистра, выход первого разряда которого соединен с первым входом триггера и управляющим входом блока переноса, выход второго разряда — с дополнительным входом блока переключения частот, выход третьего разряда со вторым входом триггера.

786010

Составитель О. Кружилина

Редактор Ж. Рожкова Тех ред А. Бо и к а с Корректор Н. Бабинец

Заказ 8864/60 Тираж 995 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

1!3035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4