Устройство для автоматической подстройки тактовой частоты

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Веслублмк

ОП И

ИЗОБРЕТЕНИЯ

<и)786032

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 223.178 (21) 2689099/18-09 с присоединением заявки ¹ (51)М. Кл 3

Н 04 l 7/02

Государственный комитет

СССР по делам изобретений и открытий (23) Приоритет

Опубликовано 071280. Бюллетень № 45 (53) УДК 621.З94. .662(088.8) Дата опубликования описания 071280 (72) Авторы изобретения

Б.К. Болдин, A.Â. Бурмистров и A.È. Синдирев (71) Заявитель (54) УСТРОЙСТВО ДЛЯ АВТОМАТИЧЕСКОЙ ПОДСТРОЙКИ

ТАКТОВОЙ ЧАСТОТЫ

Изобретение относится к радиотехнике и может быть использовано в аппаратуре передачи данных для подстройки тактовой частоты.

Известно устройство для автоматической подстройки тактовой частоты, содержащее управляемый генЕратор,выходы которого подключены соответственно к одному из входов формирователя и фазового дискриминатора, а также управляющий блок, соединенный со входом управляемого генераторами, Однако известное устройство обладает большим временем подстройки тактовой частоты по фазе.

Цель изобретения †. уменьшение времени подстройки тактовой частоты по фй(зе.

С этой целью в устройство для автоматической подстройки тактовой частоты, содержащее управляемый ге-. нератор, выходы которого подключены соответственно к-одному из входов формирователя и фазового дискриминатора, а также управляющий блок, соединенный со входом управляемого генератора, введены блок памяти, пос ледовательно соединенные дополнительный формирователь, первый элемент запрета и.элемент ИЛИ и последовательно соединенные анализатор величины рассогласования,,элемент И, второй элемснт запрета, выход которого подключен к другому входу элемента

ИЛИ. Выход фазового дискриминатора подключен ко входу блока памяти, выход которого подключен к другому входу элемента И и к одному из входов управляющего блока, к другому входу которого подключен через элемент ИЛИ второй выход дополнительного формирователя, третий выход кото рого подключен к другому входу вто15 рого элемента запрета. К другому входу первого элемента запрета подключен выход анализатора величины рассогласования, первый вход которого объединен с сигнальным входом

20 фазового дискриминатора и дополнительного формирователя,-а второф вход соединен с выходом формирователя.

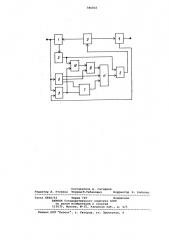

25 Ба чертеже. приведена структурная электрическая схема предложенного устройства.

Устройство содержит фазовый диск-. риминатор 1, управляющий блок 2, уп3О равляемый генератор 3, формирователь

786032

4, блок памяти, дополнительный формирователь 6, первый и второй элементы 7 и 8 запрета, анализатор 9 величины рассогласования, элемент 10 И и элемент 11 ИЛИ.

Устройство работает следующим образом.

Пусть на вход устройства поступает сигнал в виде посылок постоянно-,. го тока (или напряжения), моменты перепадов которого (фронты) несут информацию о значащих моментах восстановления (ЗМВ), тактовой частоте и ее фазе. Он поступает на сигнальный вход фазового дискриминатора 1, вход формирователя б и вход анализатора 9. На другой вход фазового диск риминатора 1 с генератора 3 поступает тактовая частота в виде импульcoB co скважностью "2". Фазовый дискриминатор 1 вырабатывает двоичный сигнал, значение которого соответст- 39 вует знаку рассогласования момента

ЗМВ и положительного (отрицательноIo) фронта тактовой частоты. Этот сигнал поступает на вход блока 5 и запоминается там. Результат с блока щ

5 поступает на один из входов элемента 10 и вход блока 2. Импульсы ЗМВ, поступающие на вход формирователя б, размножаются там таким образом, что на каждом из трех выходов они появляются последовательно, не перекрываясь по времени. С первого выхода импульс через элемент 11 поступает на блок 2, который формирует сигнал 1 изменения фазы в ту или другую сторону в зависимости от сигнала, поступающего на блок 2 с выхода блока

5. С двух других выходов формирователя б импульсы через элементы 7 и

8 запрета поступают на элемент 11.

Элемент 8 открыт только в том случае, если на элемент 10 поступают логические единицы с блока 5 и ана" лиэатора 9. Логическая единица на выходе анализатора 9 формируется при большой степени рассогласования 4 фазы тактовой частоты и ЗМВ, усредненных на некотором интервале. Эта логическая единица, открывая элементы 7 и 8, обеспечивает многократное воздействие сигнала с выхода фазового дискриминатора 1 на генератор 3 через блок 2, что позволяет. увеличить скорость подстройки. Одновременно об спечивается асимметрия величины по стройки путем подачи дополнительно -импульса на блок 2 через элемент 11 и элемент 8, который открыт только,в том случае, если наряду с логической единицей, поступающей на элемент 10 с выхода анализатора 9,на второй вход элемента 10 поступает 40 логическая единица с выхода блока 5.

Последнее означает, что импульс с выхода элемента 10 может сдвигать фазу только в одном направлении. При наличии преобладаний и начальной разности фаз равной Ж указанная асимметрия, совместно с ускоренной подстройкой, обеспечивает быстрый выход системы из состояния ложного равновесия, которое в противном случае (прн наличии преобладания) может . оказаться устойчивым.

Таким образом, предложенное устройство обеспечивает быстрое вхождение в синхронизм, в то же время (при достигнутом синхронизме) обладает большой помехоустойчивостью, что позволяет достигнуть большого времени удержания в синхронизме при кратковременных ухудшениях соотношения сигнал/шум в канале.

Формула изобретения

Устройство для автоматической подстройки тактовой частоты, содержащее управляемый генератор, выходы которого подключены соответственно к одному из входов формирователя и фазового дискриминатора, а также управляющий блок, соединенный со входом управляемого генератора, о тл и ч а ю щ е е с я тем, что, с целью уменьшения времени подстройки тактовой частоты по фазе, в него введены блок памяти, последовательно соединенные дополнительный формирователь, первый элемент запрета и элемент ЙЛИ и последовательно соединенные анализатор величины рассогласования, элемент И, второй элемент запрета, выход которого подключен к другому входу элемента ИЛИ, при этом выход фазового дискриминатора .подключен ко входу блока памяти, выход которого подключен к другому входу элемента И и к одному из входов управляющего блока, к другому входу которого подключен через эдемент ИЛИ второй выход дополнительного формирователя, третий выход которого подключен к другому входу второго элемента запрета, а к другому входу первого элемента запрета подключен выход анализатора величины рассогласования, первый вход которого объеди- нен с сигнальным входом фазового дискриминатора и дополнительного формирователя, а второй вход соединен. с выходом формирователя.

Источники информации, принятые во внимание при экспертизе

1. Мартынов B.È. Синхронизация в системах передачи дискретных сообщений. М., ".Связь", 1972, с. 35 (прототип).

786032

Составитель A. Сагадиев

Редактор Л. Утехина ТехредМ.Табакович Корректор Н. Бабинец

:Заказ 9866/б1 Тираж 729 Подписное

ВНИИПИ Государственного комитета. СССР по делам изобретений и откртий

113035, Москва, Ж-3 5, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4