Устройство для формирования опорной частоты

Иллюстрации

Показать всеРеферат

ЭСЕС9 ОЫнлЛ, ВАТЕ671!О-„ » . >:CÊßÿ

Фка MFi, ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистических

Республик

<и>786033

К АВТОРСКОМУ СВИ ЕТЕЛЬСТВУ (6! ) Дополнительное к авт. свид-ву (22) Заявлено 041278 (21) 2692477/18-09 (51) М. Кп.

H L 7/02

Н 03 К 5/08 с присоединением заявки Но (23) Приоритет

Государствеииый комитет

ССС P ио делам изооретеиий и открытий

Опубликовано 071280. Бюллетень HP 45 (53) УДК621. 394. .662(088.8) Дата опубликования описания 071280 (72) Авторы изобретения

Н.A. Карабчевская и А.С. Чистяков (71) Заявитель (54) УСТРОЙСТВО ФОР ИРОВАНИЯ ОПОРНОЙ ЧАСТОТЫ

Изобретение относится к технике связи и может использоваться для синхронизации передатчика с приемником.

Известно устройство формирования 5 опорной частоты, содержащее формирователь импульсов, коммутируемый делитель, пороговый блок, блок задержки и счетчик 1 .

Однако такое устройство имеет невысокую точность и небольшой диапазон рабочих частот.

Цель изобретения — расширение. рабочего диапазона частот. Цля этого в устройство формирования опорной частоты,. содержащее формирователь импульсов, коммутируемый делитель, пороговый блок, блок задержки и счетчик, введены блок сравнения и элемент ИЛИ, причем выход формирова- 20 теля импульсов через последовательно соединенные пороговый блок, блок задержки, блок сравнения, элемент ИЛИ и счетчик подключен к другому входу элемента ИЛИ и входу коммутируемого 25 делителя, другой вход которого соединен с выходом формирователя импульсов, вторым входом блока сравнения и другим входом блока задержки, а выход порогового блока подключен к 3п входу блока сравнения, другой вход которого подключен к другому входу счетчика, выход коммутируемого делителя подключен к четвертому входу блока сравнения, причем на вход формирователя импульсов и другой вход порогового блока подан входной сигнал; блок сравнения состоит из объединенных по первому и второму входам первого элемента И и элемента ИЛИ-НЕ, выходы которых через последовательно соединенные. элемент ИЛИ, второй элемент И подключены к первому входу третьего и.четвертого элементов И, вторые входы которых объединены, при этом входы элемента ИЛИ-НЕ, другой вход второго элемента И, вторые входы и выходы третьего и четвертого элементов И являются соответственно входами и выходами блока сравнения.

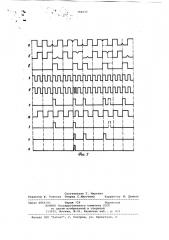

На фиг. 1 дана структурная электрическая схема предлагаемого устройства, на фиг. 2 — временные диаграммы, поясняющие работу устройства.

Устройство содержит формирователь

1 импульсов, коммутируемый делитель

2, пороговый блок 3, блок 4 задержки, счетчик 5, блок б сравнения, элемент

ИЛИ 7, блок б сравнения, состоящий

786033 из элементов И 8-11, элемента ИЛИ-HE

12 и элемента ИЛИ 13.

Устройство формирования опорной частоты работает следующим образом.

Случайный биимпульсный сигнал поступает на вход формирователя 1,стробируемого импульсами двойной тактовой частоты, при этом осуществляется формирование импульсов сигнала прямоугольной формы (фиг. 2а). Импульсный сигнал двойной тактовой частоты (фиг. 2г) поступает на коммутируемый делитель 2, на выходе которого формируется опорный сигнал тактовой частоты (фиг. 2ж), поступающий на один из входов блока 6 сравнения.На второй вход блока 6 сравнения поступает сформированный сигнал с порогового блока 3 (фиг.2а),а на третий— тот же сигнал, но задержанный блоком

4 на половину периода тактовой частоты (фиг. 2б). На четвертый вход блока 6 поступает импульсный сигнал двойной тактовой частоты (фиг. 2г).

Работа блока 6 основана на особенности биимпульсного сигнала,заключающейся в следующем: значения биимпульсного сигнала в обеих половинах тактового периода всегда различны. Таким образом, совпадение значений биимпульсного сигнала в обеих половинах тактового периода свидетельствует либо о нарушении закона кодирования, либо о режиме обратной работы устройства формирования опорной частоты. Блок 6 сравнивает значение биимпульсного сигнала в первой половине тактового периода с его значением во второй половине этого же периода. При совпадении значений биимпульсного сигнала в обеих половинах тактового периода на первом выходе блока 6 сравнения появляется импульс "ошибки" (фиг. 2з), проходящий на вход счетчика 5. При совпадении значений биимпульсного сигнала в соседних половинах смежных периоцов на втором выходе блока 6 сравнения появляется импульс "сброса" (фиг. 2и). В параллельно соединенных элементах ИЛИ-НЕ 12 и И 8 происходит сравнение значения биимпульсного сигнала с выхода порогового блока 3 со значением этого сигнала после задержки на половину периода тактовой частоты (фиг. 2б). При совпадении значений этих сигналов на выходе элемента ИЛИ 13 появляется импульсный.сигнал (фиг. 2в). Этот сигнал стробируется в элементе И 9 импульсами.цвойной тактовой частоты (фиг. 2г), в результате чего ..orv«ается сигнал (фиг. 2е). Стробирование необходимо для обеспечения работоспособности устройства независимо от разброса параметров элементов,их сТарения и температурных условий.

Простробировацный сигнал объединяется на элементах И 10> 11 с выход

Формула изобретения

1. Устройство формирования опорной частоты, содержащее. формирователь импульсов, коммутируемый делитель, пороговый блок, блок задержки и счетчик, о т л и ч а ю щ е е с я ным сигналом тактовой частоты (фиг. 2 ), причем при совпадении импульсов этих сигналов на выходе элемента И 10 появляется импульс

"сброса". Если импульс сигнала (фиг. 2е) не совпадает с импульсами тактовой частоты (фиг. 2ж), то на выходе элемента И 11 появляется импульс "ошибки" (фиг. 2з).

Для повышения помехозащищенности устройства от ошибок в законе кодирования применен счетчик 5, на выходе которого после приема K импульсов ошибки появляется сигнал (фиг. 2к), меняющий фазу тактовой частоты на 180 и сбрасывающий счет1» чик 5 в нулевое состояние, тем самым подготавливая его к дальнейшей работе. Число К определяется необходимой помехозащищенностью устройства и временем вхождения его в синхgg ронизм. Изменение фазы тактовой частоты происходит за счет того, что импульс с выхода счетчика 5 добавляется в последовательность двойной тактовой частоты, поступающую на вход коммутируемого делителя 2. Импульсы сброса (фиг. 2и), появляющиеся на выходе блока б, свидетельствуют о правильном выборе фазы тактовой частоты и сбрасывают счетчик 5 в нулевое состояние. Импульс с выхода счетчика 5 оказывается задержанным по времени относительно импульса двойной тактовой частоты за счет собственных задержек счетчика 5. Эта задержка обеспечивает формирование сигнала (фиг. 2д), который поступает на вход коммутируемого делителя 2.

Устройство формирования опорной частоты может использоваться для об4() наружения ошибок в принимаемом биимпульсном сигнале. При этом сигнал, свидртельствующий о появлении ошибки, снимается с выхода элемента

И 11.

Устройство формирования опорного сигнала по сравнению с прототипом более просто, может быть технически легче реализовано в широком диапазоне частот, в частности на низких и средних частотах, где наиболее

"О целесообразно использование биимпульсного сигнала. Устройство обладает меньшим временем восстановления синхронизма при том же объеме памяти счетчика 5 за счет подготовN ки счетчика 5 к дальнейшей работе после сбоя синхронизма устройства.

786033 тем, что, с целью расширения рабоче- го диапазона частот, в устройство введены блок сравнения и элемент ИЛИ, причем выход формирователя импульсов через последовательно соединенные пороговый блок блок задержки

I I

5 блок сравнения, элемент ИЛИ и счетчик подключен к другому входу элемента ИЛИ и входу коммутируемого делителя, другой вход которого соедйнен с выходом формирователя импульсов, вторым входом блока сравнения и с другим входом блока задержки, а выход порогового блока подключен к входу блока сравнения; другой выход ко-i торого подключен к другому входу счетчика> а выход коммутируемого де- 15 лителя подключен к четвертому входу блока сравнения, причем на вход формирователя импульсов и другой вход порогового блока подан входной сигнал.

2. Устройство по и. 1, о т л и — Щ ч а ю щ е е с я тем, что блок сравнения состоит из объединенных по первому и второму входам первого элемента И и элемента ИЛИ-НЕ, выходы которых через последовательно. соединенные элемент ИЛИ и второй элемент И подключены к первому входу третьего и четвертого элементов И, вторые входы которых объединены, при этом входы элемента ИЛИ-НЕ, другой вход второго элемента И, вторые входы и выходы третьего и четвертого элементов И являются соответственно входами и выходами блока сравнения.

Источники информации, принятые во внимание при экспертизе

1. Порохов О. Н. Некоторые вопросы построения устройств синхронизации в каналах передачи биимпульсных сигналов. Доклад на конференции, пос-. вященной 50-летию ЦНИИС. М., 1968 (прототип).

786033

Составитель Т. Маркина

Редактор Ж. Рожкова Техред С.Мигунова Корректор М. Демчик

Заказ 8866/61 Тираж 729 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патонт", r. Ужгород, ул. Проектная, 4