Устройство для выделения текущей фазы

Иллюстрации

Показать всеРеферат

Ютеи:-ио е1ь,в,,во„

A н

Союз Советских

Социалистических

Республик

ОПИС Е

ИЗОБРЕТЕНИЯ (») 788023

К АВТОРСКОМУ СВИДЕТЙЛЬСТВУ (61) Дополнительное к авт. сеид-ву— (22) За явлено 2 51 0 78 (21) 2 6 77 8 3 7/18-21 с присоединением заявки М (23) Приоритет—

Опубликовано 15.1280. Бюллетень М 46

Дата опубликования описания 201280 (51) М KB B3

G 01 R 25/00

Государствеииый комитет

СССР по делам изобретеиий и открытий (53) УДК621. 317. .373(088.8) (72) Автор изобретения

Ю. A. Глухов (71) Заявитель! 54 ) УСТРОЙСТВО ДЛЯ ВЫДЕЛЕНИЯ ТЕКУЩЕЙ ФАЗЫ

Изобретение относится к устройствам выделения текущей фазы случайных процессов и может быть использовано для исследования закономерностей изменения во времени фазы пряьых и рассеянных сигналов активной и пассивной гидролокации.

Известно устройство для выделения текущей фазы, которое содержит блок .1п аналого-цифрового выделения кнадратурных составляющих, двухканальный преобразователь напряжение-код, цифровое вычислительное устройство и блок преобразования код-напряжение t1j, Недостатком известного устройства является сложность технической реализации и невозможность работы в реальном масштабе времени.

Известно устройство для выделения 2О текущей фазы, которое содержит блок аналогового выделения квадратурных составляющих, гетеродин, блок компенсации сдвига фаз, блок суммы или разности квадратурных составляющих, два 25 формирователя калибровочных импульсов и накопитель (2).

Недостатком известного устройства является узкий диапазон рабочих мест особенно в низкочастотной области.

Цель изобретения — расширение частотного диапазона.

Цель достигается тем, что устройство для выделения текущей фазы, содержа1дее первый и второй формирователи импульсов, выходы которых соединены соответственно с первым и вторым входами накопителя, снабжено первым и вторым формирователями двоичного напряжения, делителем частоты, перньм, вторым, третьим и четвертым индикаторами, йервым и вторым триггерами с логическими входами причем выход первого формирователя двоичного напряжения соединен с первыми входами первого H второго индикаторон, вторые входы которых соединены соответственно с первым и вторым выходами делителя частоты, а первый и второй выходы соединены соответственно с перным и вторым входами первого и второго триггера, выходы которых подсоединены соответственно к первому нходу третьего и нторому входу четвертого, и второму входу третьего,и первому входу четвертого индикаторов, первый выход третьего и второй выход четвертого индикаторов соединены с нхо)дом первого формирователя импульсов, 788023 а второй выход первого и первый выход второго индикатора — с входом второго формирователя импульсов, выход второго формирователя двоичного напряжения соединен со входом делителя частоты.

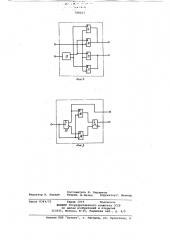

Каждый из индикаторов содержит элемент дифференцирования, первый и второй элементы И и первый и второй элементы Запрет, причем первый и второй выходы элемента дифференцирования соединены соответственно с первыми входами первого элемента Запрет и второго элемента И, и второго элемента Запрет, и первого элемента И, вторые входы всех элементов Запрет и элементов И соединены и являются первым входом индикатора, вторым входом ин- 1э дикатора является вход элемента дифференцирования, выходы первых элемента И и элемента Запрет соединены и являются первым выходом индикатора, а выходы вторых элемента И и элемента 2Q

Запрет также соединены и являются вторым выходом индикатора. Делитель частоты содержит триггер со счетным входом, триггер с логическими входами и третий и четвертый элементы Запрет, причем вход триггера со счетным входом, являющийся входом делителя частоты, соединен со вторыми входами третьего и четвертого элементов

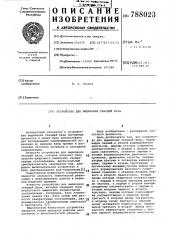

Запрет, а первый и второй выходы соответственно с первыми входами третьего и четвертого элементов Запрет, выходы которых соединены соответственно с первым и вторым входами логического триггера, выходы триггеров со счетным и логическими входами являются первым и вторым выходами делителя частоты. На фиг. 1 изображена блок-схема устройства; на фиг. 2 — схема индикатора; на фиг. 3 — схема делителя час- 4О тоты.

Устройство содержит первый и второй блоки формирования двоичного напряжения 1 и 2, делитель частоты 3, первый, второй, третий и четвертый ин-А дикаторы 4, 5, 6 и 7, первый и второй триггеры 8 и 9, первый и второй формирователи импульсов 10 и 11 и накопитель 12. Каждый из индикаторов содержит элемент дифференцирования 13, первый и второй логические элементы

И 14 и 15 и первый и второй элементы

Запрет 16 и 17. Делитель частоты содержит третий и четвертый логические элементы Запрет 18 и 19, триггер со счетным входом 20 и триггер с логическим входом 21.

На вход первого формирователя двоичного напряжения 1 поступает исследуемый сигнал с частотой Uu, а на вход второго формирователя двоичного go напряжения 2 — опорный сигнал с частотой 2 >... который после делителя частоты 3 на каждом из его выходов становится с частотой во и сдвинут в одну сторону на четверть периода. Сигналы с формирователей двоичного напряжения 1 и 2 и делителя частоты 3 поступают на первый и второй индикаторы 4 5. Индикаторы 4, 5, 6 и 7 индицируют во времени попадания положительного (отрицательного) перепада одного двоичного сигнала в единичный (нулевой) полупериод другого двоичного сигнала на одном выходе, а на ,цругом — попадания положительного (отрицательного) перепада одного сигнала в нулевой (единичный) полупериод другого сигнала. Вследствие стробоскопического эффекта на входах первого и второго триггеров 8 и 9 формируется двоичный сигнал, частота которого равна разности частот опорного исследуемого сигнала, причем переходы от единичного значения к нулевому и наоборот соответствуют переходам через нуль квадратурных составляющих с точностью до 2f /и.: . При изменении знака разности частот опорного и исследуемого сигналов меняется знак одной из составляющих, а другой знак не меняется. Третий и четвертый индикаторы 6 и 7 по полярности переходов через нуль квадратурных составляющих и по значению соответствующих им двоичных сигналов в моменты времени перехода через нуль индицируют знак разности частоты опорного и исследуемого сигналов. Если знак этой разности

"плюс" то формирователем импульсов

10 формируется импульс, если "минус", то формирователем 11. Накопитель 12 суммирует эти импульсы, причем с блока 10 со знаком "плюс", а с блока 11 со знаком,"минус".

Рассмотрим работу йндикаторов 4-7.

На вход дифференцирования 13 поступает двоичный сигнал, который дифференцируется и в положительный переход напряжения входного сигнала формируется импульс на первом выходе, а при отрицательном — на втором выходе той же полярности. Два сигнала (исследуемый и опорный) после дифференцирования, поступая на первый и второй элементы И 14 и 15 и первый и второй элементы Запрет 16 и 17, индицируют на его выходе во времени попадание положительного (отрицательного) перепада одного двоичного сигнала в единичный (нулевой) полупериод другого двоичного сигнала на одном выходе, а на другом — попадание положительного (отрицательного) перепада одного сигнала в нулевой (единичный) полупериод другого сигнала.

В делителе частоты 3 триггер со счетным входом 20 делит частоту сигнала 20>о на два и опрокидывается положительным перепадом напряжения входного сигнала. Триггер с логическим входом 21 также делит частоту входного сигнала на два, но опрокидывается отрицательным перепадом. Третий и четвертый элементы Запрет 18 и

788023

19 разрешают опрокидывание триггера

21 по первому или второму логическому входам в зависимости от потенциала напряжения на выходах триггера 20.

Использование цифровой элементной базы отличает устройство от известного, так как увеличивает дискретность отсчета текущей фазы в два раза и составляет /2 и значительно расширяет диапазон рабочих частот, который при современной элементной базе может составлять от частот близких к нулю до нескольких МГц.

Формула изобретения

1. Устройство для выделения теку- !5 щей фазы, содержащее первый и второй формирователи импульсов, выходы которых соединены соответственно с первым и вторым входами накопителя, отличающееся тем, что, щ с целью расширения частотного диапазона, оно снабжено первым и вторым формирователями двоичного напряжения, делителем частоты, первым, вторым, третьим и четвертым индикаторами, пер-2 вым и вторым триггерами с логическими входами, причем выход первого формирователя двоичного напряжения соединен с первыми входами первого и второго индикаторов, вторые входы которых соединены соответственно с пер- ЗО вым и вторым выходами делителя частоты, а первый и второй выходы соедине ны соответственно с первым и вторым входами первого и второго триггера, выходы которых подсоединены соотввтст-35 венно к первому входу третьего и второму входу четвертого, и второму входу третьего, и первому входу четвертого индикаторов, первый выход третьего и второй выход четвертого индикато-4О ров соединены с входом первого формирователя импульсов, а второй выход первого и первый выход второго индикатора — с входом второго формирователя импульсов, выход второго форми рователя двоичного напряжения соединен со входом делителя частоты.

2 Устройс во по и 1, о т л и ч а ю щ е е с я тем, что каждый из индикаторов содержит элемент дифференцирования, первый и второй элементы

И и первый и второй элементы .Запрет, причем первый и второй выходы элемента дифференцирования соединены соответственно с первыми входами первого элемента Запрет и второго элемента И и второго элемента Запрет, и первого элемента И, вторые входы всех элементов Запрет и элементов И соединены и являются первым входом индикатора, вторым входом индикатора является вход элемента дифференцирования, выходы первых элемента И и элемента

Запрет соединены и являются первым выходом индикатора, а выходы вторых элемента И и элемента .Запрет также соединены и являются вторым выходом индикатора.

3. Устройство по пп. 1 и 2, о т л и ч а ю щ е е с я тем, что делитель частоты содержит триггер со счетным входом, триггер с логическими входами и третий и четвертый элементы Запрет, причем вход триггера со счетным входом, являющийся входом делителя частоты, соединен со вторыми входами третьего и четвертого элементов Запрет, а первый и второй выходы соответственно с первыми входами третьего и четвертого элементов

Запрет, выходы которых соединены соответственно с первым и вторым входами логического триггера, выходы триггеров со счетным и логическими входами являются первым и вторым выходами делителя частоты.

Источники информации, принятЫе во внимание при экспертизе

1. Захаров В. A. О выделении огибающей и фазы случайного процесса (труды акустического института), 1966, вын. 1, с. 134-136.

2. Авторское свидетельство СССР по заявке Р 2481381/21, кл. G 01 R 25/00, 1977.

788023

Фие. 2

Составитель М. Барашков

Редактор Н. Кешелов . Техред М,Петко . КорректорС. Шекмар.

Заказ 8344/52 Тираж 1019 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5 филиал ППП "Патент", г. Ужгород, ул. Проектная, 4