Сумматор с контролем

Иллюстрации

Показать всеРеферат

Gll ИСАНИ-Е

И ЗОЬРЕТЕ Н ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик ш 788108 (6! ) Дополнительное к авт. саид-ву (2g) Заявлено 02.01,79 (21) 2705417/18 — 24 (51)M. Кл.

6 06 F 7/50

G 06 Е 11/26 с присоединением заявки Ж

Гоаударстванный квинтет (23) Приоритет

А0 A8/IBM нзобретеиий н атхрытнй

Опубликовано 15.12 80 Бюллетень Рй

Ната опубликования описания 15.12.80 (53) УДК 681.325 (088.8) В. В, Бугаенко, В. И. Корнейчук, В. И, Носаль, Л. А. Савченко, В. П, Тарасенко и Я. И. Торошанко (72) Авторы изобретения

Киевский ордена Ленина политехнический институт им, 50-летия

Великой Октябрьской сопналистической революции (7I) Заявитель (54) СУММАТОР С KOHTPOJIEM

Изобретение относится к вычислительной технике и может быть использовано при постооении ЦВМ повышенной надежности.

Известен сумматор с контролем ошибок, 5 каждый разряд которого содержит одноразрядный сумматор, входы и выходы которого подключены к декоднруюшему преобразователю, выходы которого через эмиттерный повторитель подключены к схеме неравнозначности, второй вход которой соединен с шиной опорного напряжения. Выходы схем неравноэначности всех разрядов соединены через многовходовой элемент ИЛИ с шиной ошибки. В таком сумматоре обнаружсние о1ыибок осуществляется на основе закономерностз, заключающейся в том, что при правильной работе арифметическая сумма инверсных входных сигналов одноразрядного сумматора и сигна . суммы, взятых с единичными весами, и сигнала переноса в следующий разряд, взятого с весом, равным 2, всегga равна 3. При неправильной работе это соотношение нарушается, что определяется схемой неравнозначности,1).

Наиболее близким техническим решением к изобретению является контролируемый и-разрядный сумматор, каждый разряд которого содержит два полусумматора для формирования сумм по модулю 2 и переносов, элемент

ИЛИ, объединяющий выходы переносов полусумматоров, элементы И и HE и два пороговых элемента, подключенных к прямым и инверсным входам и выходам полусумматорови элемента ИЛИ. Выходы пороговых элементов всех разрядов подключены через многовходовой элемент ИЛИ к шине ошибки сумматора. При правильной работе сумматора сумма входов пороговых элементов равна константе, при неправильной работе сумма входов одного из пороговых элементов превышает значение константы (порога) и на его выходе появляется сигнал ошибки (2)

Недостатком известных сумматоров являются значительные аппаратурные затраты.

Цель изобретения — сокращение аппаратурных затрат.

Поставленная цель достигается тем, что в сумматоре с контролем, содержащем элемент

ИЛИ, и одноразрядных сумматоров, соединенных последовательно цепями переноса, и пороговых элементов с порогом на 6, причем выходы всех пороговых элементов соединены с соответствующими входами элемента ИЛИ, выход которого является выходом устройства, первый, второй и третий входы каждого одноразрядного сумматора соединены соответственно с шинами i-ro разряда первого, второго операнда и с выходом переноса одноразрядного сумматора (i-!)-го разряда, шина i-го разряда первого операнда соединена с первым входом с весом 1 i-го порогового элемента и, с первым инверсным входом с весом 1 (itl) ° порогового элемента,.шина i-го разряда второго операнда соединена со вторым входом с весом 1 i-ro порогового элемента и со вторым инверсным входом с весом 1 (+1)-гоi порогового элемента, шина переноса из (i — !)-г разряда соединена с третьим входом с весом

1 i-го порогового элемента и с третьим инвер ным входом с весом 1 (i+1)-го порогового элемента, выход суммы i-го одноразрядного сумматора соединен с первым инверсным входом с весом 1 i-го порогового элемента и с первым входом с весом l (i+1)-ro пороговог элемента, выход переноса i-го одноразрядного сумматора соединен. со вторым инверсным вхо дом с весом 1 i-го порогового элемента и со вторым входом с весом 1 (i+1)-ro пороговог элемента, шина (+1)-го разряда первого операнда соединена с четвертым входом с весом

1 i-го порогового элемента и четвертым инвер ным входом с весом 1 (i+1)-го порогового элемента, шина (i+1)-го разряда второго операнда соединена с пятым входом с весом 1

i-го порогового элемента и с пятым инверснь входом с весом 1 (i+1)-ro порогового элемен та, выход суммы (i+I)-го одноразрядного су матора соединен с третьим инверсным входом с весом 1 i-го порогового элемента и с треть им входом с весом 1 (i+1) ãî порогового эл мента, выход переноса (i+1)-ro одноразрядного сумматора соединен с четвертым инверсным входом с весом 2 i-го порогового элемента и четвертым входом с весом 2 (i+1)-ãî порогового элемента, P„»„+ а„

+Р;, +2Р;=

4$ ь

+ Р„ +2Р;

+ b„

+ bü

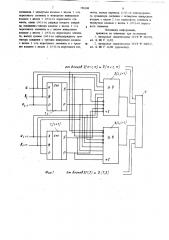

5 а+„+ bi+„ t Si + $ и (1) (2) 788108 4 (i, i+1) и 3. (i, i+1) с порогами срабатывания, равными 6. Обозначение пороговых элементов

2.(i, i+1) и 3.(i, i+1) говорит о том, что пороговые элементы относятся к i-му и (i+I)-му разрядам сумматора, Входы с весом 1 порогового элемента 2, (i, i+1) подключены ко входам операндов одноразрядных сумматоров I,i и 1.(itl), ко входу переноса одноразрядного сумматора l,i. Инверсные входы с весом 1 этого порогового элемента подключены к выходам сумм одноразрядных сумматоров I.i и 1.(i+1) и к выходу переноса одноразрядного сумматора I.i, Инверсный вход порогового го элемента с весом 2 подключен к выходу переноса одноразрядного сумматора 1.(i+1). Инверсные входы с весом 1 порогового элемента

3.(i, i+1) подключены ко входам операндов одноразрядных сумматоров 1. 1 и 1.(itI) i ко о входу переноса одноразрядного сумматора I.i.

Прямые входы с весом 1 этого порогового элемента подключены к выходам сумм одноразрядных сумматоров I.i u 1.(i+1) и к выходу переноса одноразрядного сумматора I.i.

Прямой вход порогового элемента с весом 2 подключен к выходу переноса одноразрядного о сумматора 1. (i+1). Выходы пороговых элементов 2. (i, i+1) и 3.(i, i+1) всех разрядов подключены через п-входовой элемент ИЛИ 4 к выходу ошибки сумматора.

Обнаружение ошибок осуществляется на основании следуюшей закономерности: арифметическая сумма, составленная из операндов а>, с b>, а „„, Ь„, i-го и (i+1)-го разрядов, входного переноса P,.!, обратных кодов сумм

i-ro и (i+1) ãî разрядов, инверсных значений

35 переноса i-го и (i+1)-го разрядов, а также

rM арифметическая сумма, составленная из обратных кодов операндов а, Ь;, à„„, b; „ i ãî м- и (+1)-ro разрядов, инверсного входного переноса Р„», выходов сумм i-го и (i+1)-го разрядов, значений переноса i-го и (i+1)-го е- разрядов должна быть равной где а„, b „, а

Р;»

Р„, Р;ti

На фиг. 1 изображена функциональная схема i-го и (i+1)-ro разрядов сумматора; на фиг. 2 — таблица, поясняюшая работу сумматора.

Устройство содержит и одноразрядных сумматоров 1, соединенных последовательно цепями переноса. Входы каждого одноразрядного сумматора 1 подключены ко входам соответствуюших разрядов операндов. Ко входам и выходам каждого i-го 1 i и (i+1)-го

1. (+1) одноразрядных сумматоров подключены два девятивходовых пороговых элемента 2.

Ы ° ь+1

b — значения соответственно i-го и (i+1)-ro разрядов входных операндов; — значение переноса из пред ыдуше го (i — 1 ) - го разряда; — значения сумм i-го и (i -1) - ro разрядов; — значения переноса i-го и (i+1) -го раэрядов . сумматора 1. и 1.(j+I}

788108 ь

Очевидно, что C-. Разница между сложностью известного и предлагаемого сумматоров P = С вЂ” С = С1, — С, Сложность схемы контроля известного устройства

S С1, = 7п + 8п = 15п, так как для контроля каждого разряда требуется два ПЭ с количеством входов 7 и 8.

Сложность схемы контроля предлагаемого устройства

1О С = 9п

Сравним сложность известного (1) и предлагаемого сумматоров, Если схема неравнозначности этого. сумматора построена на двух 5-ти входовых ПЭ, то сложность схемы сумматора

1S Равна

С1 = 2п 5 = 10п.

Таким образом, рассматриваемый сумматор требует меньше аппаратурных затрат для постщ роения схемы контроля по сравнению с известным, При появлении неисправности на одном из выходов сумматоров I.i или 1.(i+1) появляется ошибочный сигнал, в результате чего соотношение (1) и (2) нарушается, т,е. сумма входных сигналов одного иэ пороговых элементов 2, (i, i+1) и 3.(i, i+1) превышает поpor его срабатывания, в результате чего на выходе этого порогового элемента 2, (i, I+I) и 3,(i, i+1) появляется сигнал ошибки.

На фиг. 2 показана таблица состояний

i-го и (i+1)-го разрядов сумматора, в которой приведены значения сумм входных сигналов ПЭ, срабатываюшего при появлении ошибки на одном из выходов i-го или (i+1) ãî разрядов сумматора. В графе Р„1, а, Ь„, а.„+„, Ь„,< указан рассматриваемый входной набор, в графе Si $;+, Р„, Р,„— соответствуюшнй входному выходной набор, в остальных четырех графах — арифметическая сумма значений входных сигналов (с учетом весов) срабатываемого порогового элемента при появлении ошибочного сигнала на одном из выходов i-го.или (i+1)-ro разряда $, Р„, S„

Р,<, Рассмотрим работу сумматора на входном наборе Р„ = О, а;= 1, Ь.„= 1, а„ = О, Ь„, = 1 при появлении ошибочного сигнала переноса

Р„,, При правильной работе иа выходе (i+1)-ãî сумматора сигнал переноса равен 1. При появлении на этом выходе сигнала 0 на входы пора-ц> гового элемента 2. (I, 1+1) поступает код

011011120 (с учетом весов). Сумма значений входных сигналов равна 7, что превышает порог срабатывания порогового элемента 2 (i, i+1) и на его выходе появляется сигнал ошибки. Значения входных сигналов приведены в том же порядке, что н в таблице, т.е. Р„,, а „, Ь„, аь+„, Ь ic, $;, Bi+1, Pi >, Р; . При появлении ошибочного сигнала ("О™ вместо

"l") на выходе Р„на вход порогового элемен-41 та 2.(i, i+1) поступает код 011011021, сумма весов равна 7 и на выходе порогового элемента 2.(i, i+I) появляется сигнал ошибки. В сумматоре обнаруживаются все ошибки, вызванные одиночными неисправностями. Кроме того, 45 анализируя состояние выходов пороговых элементов, можно обнаружить неисправный разряд.

Оценкой сложности цифровых схем может быть цена по Квайну С =,2 К .С,, где К; количество элементов i-ro тйпа, используемых в схеме; С; — цена элемента по Квайну, которая определяется числом входов элемента.

Сложность известно о сумматора С С,0 +

+ С, сложность предлагаемого сумматора

С = C2oc+ C >

И где индексы 1 н 2 отнесены соответственно к известному и предлагаемому сумматорам:

С„, — сложность одноразрядного сумматора;

С; — сложность схем контроля.

Формула изобретения

Сумматор с контролем, содержашнй элемент

ИЛИ, и одноразрядных сумматоров, соединенных последовательно цепями переноса, и пороговых элементов с порогом на 6, причем выходы всех пороговых элементов соединены с соответствуюпшми входами элемента ИЛИ, выход которого является выходом устронства, первый, второй и третий входы каждого i-го одноразрядного сумматора соединены соответственно с шинами i-го разряда первого, второго операнда и с выходом переноса одноразрядного сумматора (i — 1)-го разряда, о т л н ч аю ш н и с я тем, что, с целью сокрашения аппаратурных затрат, шина i-го разряда первого операнда соединена с первым входом с весом 1 i-го порогового элемента и с первым инверсным входом с весом 1 (i+1)-го порогового элемента, шина i-го разряда второго операнда соединена со вторым входом с весом 1

i-го порогового элемента и со вторым инверсным входом с весом 1 (i+I) ãî порогового элемента, шина переноса из (i — 1)-ro разряда соединена с третьим входом с весом 1 i-го порогового элемента и с третьим инверсным входом с весом 1 (i+1)-го порогового элемента, выход суммы i-го одноразрядного сумматора соединен с первым инверсным входом с весом 1 i-ro порогового элемента и с первым входом с весом 1 (i+I)-го порогового элемента, выход переноса i-го одноразрядного сумматора соединен со вторым инверсным входом с весом 1 i-го порогового элемента и со вторым входом с весом 1 (i+1)-го порогового элемента, шина (i+1)-го разряда первого операнда

788108

10 соединена с четвертым входом с весом 1 i-ro порогового элемента и четвертым инверсным входом с весом 1 (i+1)-ro порогового элемента, шина (i+1)-ãî разряда второго операнда соединена с пятым, входом с весом 1 i-го порогового элемента и с пятым инверсным входом с весом 1 (i+1)-ro порогового элемента, выход суммы (i+1)-го одноразрядного сумматора соединен с третьим инверсным входом с весом 1 i-го порогового элемента и с третьим входом с весом 1 . (!+1)-ro порогового элемента, выход переноса (i+1)-го одноразрядного сумматора соединен с четвертым инверсным входом с весом 2 i-го порогового элемента и четвертым входом с весом 2 (i+1)-го порогового элемента, Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР Н 3657033., кл. G 06 F 11/02.

2. Авторское свидетельство СССР Н 50052, кл. 6 06 F 11/00 (прототип).

7S810S й) 4 (lt ши3нч си х м.!и

6 . Р.!! ! б Х, пппб и« Ае ;,

П32 ПУЗ!

7.!г ЛЯЗ

n7Z ЛЭЯ

i 6! 6

6 а о

1 !

Ь, 6

6

6 д

7 1 б — 1 б б! Л 7

6 1 б! 7

6 — 1

7

7 — б

7 б

, 7

У 7

7

- -4б

У

1

7

7 ° б

6 б

6 а о

0 !

1 б б

7"

-!7

7

0

6

6 б

7 !! 7

6 б

6 б

6 б б

1

1 б 6

7

6 б

- +

7 б

Put 2

Составитель И. Сигалов

Техред И, Асталош

И. Нанкина

Корректор С, Иекмар

Редактор

Заказ 8352j56

Тираж 751 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4! 5

Филиал ППП "Патент", r Ужгород, ул. Проектная, 4

Р

0 д

7

0 !

Ю

6

1

1

1

Р

Р

1

1

f

4 !

1 7

7

7 т

--1

-- ---1.—

7

7

7 — 1 — ——

t==

7 т-" —7

7

7 !