Оперативное запоминающее устройство

Иллюстрации

Показать всеРеферат

тг ц .г °

ОПИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз . Советских

Социалистических

Республик (i ii 788173 (61) Дополнительное к авт. свид-ву— (22) Заявлено 05.12.78 (21) 2707178/18-24 с присоединением заявки №вЂ” (23) Приоритет— (51) M. Кл, з

G 11 С 11/00

Гасударственный комнтет

СССР

Опубликовано 15.12.80. Бюллетень № 46

Дата опубликования описания 25.12.80 (53) УДК 681.327..6 (088.8) ао делам нзобретеннй н атхрытнй (72} Авторы изобретения

В. П. Видоменко, Б. Г. Иванов, А. П. Рыбкин и В. И. Сидоров

Государственное союзное конструкторско-технологическое бюро по проектированию счетных машин и Опытный завод

Государственного союзного конструкторско-технологического бюро по проектированию счетных машин (71) Заявители (54) ОПЕРАТИВНОЕ ЗАПОМИНА10ЩЕЕ УСТРОЙСТВО

Изобретение относится к вычислительной технике, а именно к организации памяти ЭВМ, и может быть использовано преимущественно в автоматизированных системах обработки данных.

Известны оперативные запоминающие устройства адресного типа, которые применяются для формирования вторичных информационных массивов по данному первичному массиву путем дублирования записей или организации индексированных массивов 11).

Наиболее близким по технической сущности к предлагаемому изобретению является оперативное запоминающее устройство, содержащее накопитель, устройство управления накопителем, выходы которого соединены с входами накопителя, шину управления, адресную шину, счетчик адреса, дешифратор и регистр. Такая конструкция позволяет повысить информационную емкость устройс-.ва (2I .

Недостатками известного устройства являются ограниченные функциональные воэможности, исключающие автономное выполнение программно-управляемых арифметико логических операций над адресами, и низ2 кое быстродействие в режиме последовательной выборки информации по разреженному массиву флагов, обусловленное поразрядным опросом регистра флагов и «холостойь работой счетчика адреса при просмотре битов, не отмеченных флагом.

Цель изобретения — повышение быстродействия устройства при выборе информации.

Поставленная цель достигается тем, что в устройство, содержащее блок управления, выход которого подключен к управляющим

to входам счетчика, накопителя и регистра, адресную, информационную шину и шину управления, введены блок регистров, одни входы которого подключены к входной шине, первым входам счетчика и блока управления, арифметико-логический блок, одни вход которого подключен к выходу счетчика и входу дешифратор ., другие — к соотвутствующим выходам блока регистров, информацион ный выход арифметико-логического блока подключен к адресной шине накопителя и другим входам блока регистров, а выход переноса — ко второму входу блока управления, сумматор, один вход которого подклю.чен к выходу дешифратора и одному иэ входов регистра, другой вход которого подклю788173

Формула изобретения чен к информационному выходу накопителя, выход регистра соединен с другим входом сумматора, последовательно соединенные вентили окончания переноса и шифратор, выход которого подключен ко второму входу счетчика, один вход вентилей окончания переноса подключен к выходу сумматора, другои — к информационным входам накопителя и выходу регистра, выход переноса сумматора подключен к третьму входу блока управления, причем управляющие входы арифметико-логического блока и блока регистров подключены к выходу блока управления.

Выполненное таким образом устройство позволяет хранить и с высоким быстродействием обрабатывать отображенную в битовые массивы вторичную информацию центральной памяти.

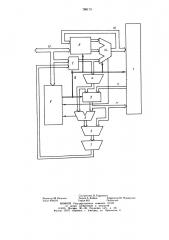

На чертеже изображена структурная схема многофункционального оперативного запоминающего устройства.

Устройство содержит флаговую память, которая состоит из накопителя 1, счетчика 2 адреса, регистра 3, дешифратора 4, сумматора 6, вентилей 6 окончания переноса, шифратора 7, блока 8 регистров и блока 9 управления, адресную шину 10, информационную шину 1l и шину 12 управления. Код адреса опроса из 3ВМ поступает по входной шине 13 на счетчик 2 адреса. Младшие

m = log>r разрядов кода адреса (здесь r— разрядность ячеек флаговой памяти) поступают со счетчика 2 адреса на дополнительный дешифратор 4.

Особенность предлагаемого устройства заключается в том, что вместо схемы коммутации и схемы сравнения, используемых в известном устройстве для поиска информации, ближайщей к данной, введены сумматор, блок вентилей окончания переноса и шифратор. Поиск происходит не путем поразрядного опроса регистра с соответствующим увеличением или уменьшением содержимого реверсивного счетчика адреса, а сложением обратного кода регистра с выходом дешифратора. Так как с выхода-дешифратора поступает всего один единичный сигнал то он вызывает не больше одной цепочки переноса, который заканчивается на том разряде. где стоит ближайшая от начала поиска информация. Этот разряд выделяется специально введенным блоком вентилей окончания переноса. Выходной унитарный код преобразуется введенным шифратором в двоичный код младших разрядов адреса, который по соответствующему сигналу с бло ка управления записывается в младшие разряды счетчика адреса вместо ранее имевшегося в нем кода. Таким образом, поиск происходит за один цикл работы счетчика адреса.

Отличительной особенностью предлагаемого устройства является также наличие в

as

30 эь

SO

1 нем сверхоперативной памяти в виде дополнительного блока 8 регистров арифметикологического блока 14 и блока 9 управления, что придает устройству автономность, позволяя независимо от процессора ЭИМ выполнять арифметические и логические операции над адресами и ячейками памяти.

Преимуществами предлагаемого устройства по сравнению с известным являются более высокое быстродействие йри последовательной выборке информации и расщирение функциональных возможностей, позволяющее выполнять программно-управляемые операции по распределению памяти между различными массивами вторичной информации и такие операции над этими массивами, как объединение, пересечение, дублирование, инвертирование, а также сброс.

Оперативное запоминающее устройство, содержащее блок управления, выход которого подключен к управляющим вчодам счетчика, накопителя и регистра, адресную и информационную шины и шину управления, отличающееся тем, что, с целью повышения быстродействия устройства при выборе информации, оно содержит блок регистров, одни вход которого подключены к входной шине, первому входу счетчика и первому входу блока управления, арифметико-логический блок, один вход которого подключен к выходу счетчика и входу дешифратора, другие — к соответствующим выходам блока регистров, информационный. выход арифметико-логического блока подключен к адресной шине накопителя и другим входам блока регистров, а выход переноса — ко второму входу блока управления, сумматор, один вход которого подключен к выходу дешифратора и одному из входов регистра, другой вход которого подключен к информационному выходу накопителя, выход регистра соединен с другим входом сумматора, последовательно соединенные вентили окончания переноса и шифратор, выход которого подключен ко второму входу счетчика, один вход вентилей окончания переноса подключен к выходу сумматора, другой — к информационным входам накопителя и выходу регистра, выход переноса сумматора подключен к третьему входу блока управления, причем управляющие входы арифметикологического блока и блока регистров подключены к выходу блока управления.

Источники информации, принятые во внимание при экспертизе

1. Берзатис А. Т. Структура данных.

М., <<Статистика», 1974, с. 312. 2. Авторское свидетельство СССР кл. Ci 11 С 11/00, по заявке г1 2443708/I8-24, 28.12.76 (прототип) .

788!73

Составитель В. Гордонова

Редактор И. Нанкнна Техред А. Бойкас Корректор Ю. Макаренко

Закан 8360/59 Тираж 662 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП аПатент>, r. Ужгород, ул. Проектная, 4