Запоминающий элемент

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (61) Дополнительное к авт. сеид-ву (22) Заявлено 23. 11. 78 (21) 2687668/18-24 (51) M с присоединением заявки ¹ (23) Приоритет

G 11 С 11/40

Государственный комитет

СССР ио делам изобретений н открытий

Опубликовано 151?80, Бюллетень ¹ 46

Дата опубликования описания 1712ЯО (53) УДК681. 327. .66(088.8) (72) Авторы изобретения

Е. Б. Механцев, P. С. Кильметов и A. И. Сухоруков (71) Заявитель

Таганрогский радиотехнический институт им. В.Д. Калмыкова (54) ЗАПОМИНАЮЩИЙ ЭЛЕМЕНТ

Изобретение относится к вычисли. тельной технике и предназначено для использования в монолитных интегральных запоминающих устройствах различного назначения.

Известны запоминающие элементы статического типа на диодах с % -образной характеристикой (лямбда диод). Диод с % -образной характеристикой представляет собой двухполюсный полупро- 10 водниковый прибор с отрицательным сопротивлением, принцип действия которого основан на эффекте поля 111.

".ýâåñòåH запоминающий элемент содержащий диод с % -образной характе- 15 ристикой, нагрузочный и управляющий элементы, в качестве которых обычно используются полевые транзисторы (2) °

Основной недостаток запоминающего элемента — значительное потребление 2Q мощности в статическом состоянии, а также большое количество шин (две шины питания, адресная и разрядная шины).

Наиболее близким к предлагаемому 25 по технической сущности является запоминающий элемент статического типа, содержащий диод с -образной характеристикой, нагрузочный и допол.нительный управляющий МДП-транзисто- 30 ры. Сток управляющего транзистора со-,: единен с анодом диода. с % -образной характеристикой, исток и затвор подключены, соответственно, к разрядной и адресной шинам. В режиме хранения информации на затворе управляющего транзистора поддерживается нулевой потенциал. При записи информации на адресную шину подается импульс положительной полярности, а на разрядной.

"1" (при записи кода "1") .или "0" (при записи кода "0"). Считывание информации осуществляется подачей импульса положительной полярности в адресную шину. Такой запоминающий элемент имеет среднее быстродействие порядка 1 мкс и используется для реализации матрйц памяти интегрального запоминающего устройства (3) .

К недостаткам известного следует отнести то, что он потребляет значительную Мощность в статическом состоянии, имеет большое количество шин (две шины питания, а. также адресную и разрядную), что усложняет управление им, поскольку для нормальной работы необходимо подавать сигналы, совпадающие во времени в адресной н < разрядной шинах от двух формирующих устройств.

788174

Цель изобретения — снижение потребляемой мощности элементов в статическом состоянии и его упрощение.

Поставленная цель достигается тем, что в запоминающем элементе, содержащем диод с -образной характеристикой,анод которого соединен со стоком

МДП-транзистора, исток МДП-транзистора подсоединен к разрядной шине и к первой шине питания, затвор. МДПтранзистора соединен с адресной шиной, и вторую шину питания, затвор

МДП-транзистора соединен с катодом диода с -образной характеристикой и второй шиной питания, разрядная и адресная шины соответственно соединены с шинами питания.

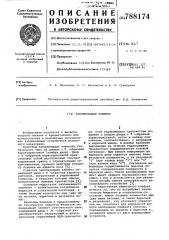

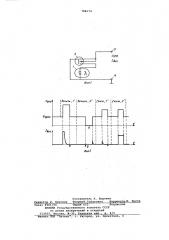

На фиг. 1 представлена электрическая схема предлагаемого запоминающего элемента; на фиг. 2 — временная диаграмма его работы.

Запоминающий элемент содержит диод 1 с Х -образной характеристикой 1, МДП-транзистор 2, разрядную шину, соединенную с первой шиной 3- питания, адресную шину, соединенную со второй шиной 4 питания. МДП-транзистор выбран таким образом, что его пороГовое напряжение больше, чем напряжения отсечки диода с 9 -образной характеристикой.

Запоминающий элемент работает следующим образом.

В режиме хранения информации на шине 3 поддерживается положительный потенциал (О „фиг. 2а), величина которого больше напряжения отсечки диода 1, но меньше порогового напряжения

МДП-транзистора 2. Если в запоминающем элементе хранится код "0", то этому соответствует низкий потенциал на аноде диода 1, при этом МДП-транзистор 2 закрыт, а диод 1 открыт. Ток в выходной цепи запоминающего элемента равен остаточному току закрытого

МДП-транзистора 2. Коду "1" соответствует высокий потенциал на аноде ди-. ода 1, при этом диод 1 закрыт. Ток в цепи равен току утечки закрытого диода 1. Таким образом, в статических состояниях "0" и "1" ток в выходной . цепи запоминающего элемента практически не протекает, и потребляемая мощность составляет малую величину.

При записи кода "1" в шину 3 подается положительный импульс, величина которого превышает пороговое напряжение

МД1-транзистора 2. Тогда напряжение на аноде диода 1 увеличивается, и при достижении напряжения отсечки ои эакрывае гся. При снятии импульса запоминающий элемент сохраняет это состояние. Для записи кода "0" в шине 3 потенциал уменьшается от Us „до О, при этом диод 1 открывается и на его аноде устанавливается низкий потенциал., Считывание информации осуществляется подачей импульса положительной полярности в шину 3, амплитуда

Формула изобретения

Запоминающий элемент, содержащий диод с4 -образной характеристикой, анод которого соединен со стоком

МДП-транзистора, исток МДП-транзисто45 ра подсоединен к разрядной шине и к первой шине питания, затвор МДП-транзистора соединен с адресной шиной, и вторую шину питания, о т л и ч,аю шийся тем, что, с целью сни50 жения потребляемой мощности элементом в статическом состоянии и его упрощения, в нем затвор МДП-транзистора соединен с катодом диода с образной характеристикой и второй шиной питания, разрядная и адресная шины соответственно соединены с шина-. ми питания.

Источники информации, принятые во внимание при экспертизе

1. "Радиоэлектронйка", том 17, 9 5 е0 1974, с. 38-44.

2. Заявка Франции М 2290759, Ьл. G 11 С 11/40, 09.07.76.

3. 1ЕЕЕ Transtions on .Е1есtron

0evices vot ЕО-24 jun.е, 1977, 65 рр . 751-756.

35 которого выбирается из условия неазрушающего считывания U „

Таким образом, использование в запоминающем элементе в качестве нагрузки МДП-транзистора, затвор которого соединен с шиной питания и катодом диода 1, позволяет существенно уменьшить потребляемую мощность в статическом состоянии, уменьшить общее количество шин до минимального значения (две шины, включая шины источника), чем достигается упрощение управления и, тем самым, получить положительный технико-экономический эффект.

Лабораторные испытания показали устойчивую работу модели запоминающего элемента в широком интервале изменения входных сигналов. При этом в устойчивых состояниях "0" и "1" через элемент протекают только токи утечки

МДП-транзистора и диода с Ь -образной характеристикой, и потребляемая мощность практически составляет единицы пиковатт, что на 2 порядка меньше, чем у известного. Уменьшение количества элементов и информационных шин до минимального значения (до двух элементов: диод и МДП-транзистор, до двух шин, включая и шины питания) позволяет при использовании таких запоминающих элементов для построения больших интегральных матриц па.яти уменьшить площадь кристалла в 2-3 раза, снизить паразитные емкости, увеличить быстродействие и надежность в работе.

788174

Ebir.

Оупр

Составитель A. Воронин

Заказ 8361/60 Тираж 662 Подписное

ВНИИПИ Госдуарственного комитета СССР по делам изобретений и открытий

113035, Москва, *-33 Ва3авскаа каа. д. 443

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4