Цифровой генератор псевдослучайной последовательности импульсов

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

<1 788357

И АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. сеид-ву— (22) Заявлено 1912.78 (21) 2697825/18-21 с присоединением заявки Hо— (23) Приоритет—

Опубликовано 151280. Бюллетень И9 46

Дата опубликования описания 15.1280 (51) М К 3

Н 03 К 3/84

Государственный комитет

СССР по делам изобретений и открытий (53) УДК 621.317.. 7 (088. 8) (72) Авторы изобретения

N. И. Травкин и О. В. Данилова

Ленинградский ордена Ленина электротехнический институт им. В.И. Ульянова (Ленина) (71) Заявитель (54) ЦИФРОВОЯ ГЕHEPATOP ПСЕВДОСЛУЧАЙНОЙ ПОСЛЕДОВАТЕЛЬНОСТИ

ИМПУЛЬСОВ

Изобретение относится к вычислительной технике и может быть использовано для моделирования псевдослучайной двоичной последовательности максимальной длины с одинаковым числом "единиц" и "нулей".

Известен генератор, содержащий два регистра псевдослучайной последовательности, дешифратор, генератор, схему И, блок сравнения и блок вычитания, причем выход генератора соединен со входом первого регистра и с первым входом схемы И. Выходы разрядов первого регистра соединены с входами. дешифратора, выход которого соединен со вторым входом схемы И, с управляющим входом блока вычитания.

Вход второго регистра псевдослучайной последовательности соединен с выходом схемы И, а его выход соединен с первым входом блока сравнения. Второй вход блока сравнения соединен с выходом первого регистра, а его выходы соединены с информационными входами блока вычитания, выход которого является выходом устройства.

По сигналу генератора первый п-разрядный регистр псевдослучайной последовательности формирует последовательности из (2 -1) разрядов. Дешифратор выделяет одно из состояний первого регистра и блокирует на один такт формирование псевдослучайной (2 -1) nocftl ледовательности вторым m-разрядным регистром. B реэультате имеет место фазовый сдвиг на один такт Т в фор мировании (2 -1) последовательности относительно (2"-1) последовательности.

Максимальное число фазовых сдвигов равно m. На выходе схеьы блока сравнения формируется псевдослучайная последовательность, являющаяся результатом суммирования по модулю 2 двух исходных последовательностей, и имеет длину (и ° m) разрядов. Блок вычитания вычисляет количество совпадающих и несовпадающих элементов в двух последовательностях эа период пТ. Выходной сигнал является L — уровневым аналоговым сигналом f1) .

Недостатками из вестного устройства при использовании его в качестве формирователя псевдослучайной последовательности максимальной длины являются сложность cxema, неравновероятность

"нулей" и "единиц" в последовательности, частотные ограничения, обусловленные обратными связями.

788357

Наиболее близким к предлагаемому является генератор псевдослучайной последов ател ьности, содержащий кол ьцевой регистр, первая группа выходов которого соединена с дешифратором, выходом подключенного к входу триггера, логические элементы И, выходы которых соединены с входами логического элемента или, первый выход триггера соединен с первым входом первого логического элемента И, второй выход триггера с перным входом второго логического элемента И (2) .

Недостатком устройства является то, что период генерируемой псевдослучайной последовательности линейно связан с дли ной кольце но ro сдни гово го ре гистра и, следовательно, с объемом дешифратора, поэтому устройство экономически невыгодно в случае генерации длинных последовательностей, что умень шает диапазон работы устройства.

Цель изобретения — расширение диапазона работы устройства.

Цель достигается тем, что н цифровой генератор псевдослучайной последовательности импульсов, содержащий кольцевой регистр, первая группа выходов которого соединена с дешифратором, выходом подключенного к входу триггера, логические элименты И, выходы которых соединены с входами логического элемента ИЛИ, первый выход триггера соединен с первым входом первого логического элемента И, второй выход триггера — с первым входом второго логического элемента И, введены коммутатор фазы и инвертор, причем вторая группа выходов кольцевого регистра соединена с группой управляющих входов коммутатора фазы, вход которого соединен с первым выходом триггера, а выход через инвертор со вторым входом первого логического элемент а И непосредст вен но — с вторым входом второго логического элемента

И, выход логического элемента ИЛИ соединен с выходной шиной устройст- ва.

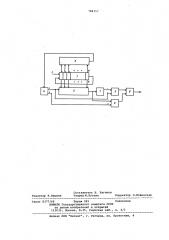

На. чертеже приведена функциональная схема устройства.

В устройстве выходы кольцевого регистра 1 соединены со входами дешифратора 2 и с информационными входами коммутатора фазы 3. Выход дешифратора 2 соединен со входом триггера 4 режима, первый выход которого соединен с управляющим входом ком>утатора фазы 3 и со вторым входом первого логического элемента И 5, а второй выход соединен со вторым входом второго логического элемента И б. Выход коммутатора фазы 3 соединен со входом инвертора 7 и с первым входом второго логического элемента И 6, а выход инвертора 7 соединен с первым входом первого логического элемента И 5. Выход логического элемента ИЛИ 8 является выходом устройства.

Устройство работает следующим образом.

Исходный N-значный код псевдослучайной последовательности по тактовому сигналу циклически сдвигается в

N-разрядном кольцевом регистре 1. Выходы всех разрядов регистра 1 соединены с информационными входами дешифратора 2, которые дешифрируя одно из

N возмо>кных состояний регистра 1, формируют на своем выходе сигнал, изменяющий состояние триггера 4 режима.

При этом разрешающий сигнал с триггера 4 режима приходит на первый или на второй логические элементы И 5,6, пропуская через логический элемент

15 ИЛИ 8 на выход устройства попеременно прямую и через инвертор 7 инверсную фазоманипулированную псевдослучайную последовательность с выхода коммутатора фазы 3. Выходы К разрядов кольцевого регистра 1 соединены с информационными входами коммутатора фазы 3, который по управляющему сигналу с первого выхода триггера 4 режима коммутирует последовательно выходы

К разрядов сднигового кольцевого ðåгистра 1. Таким образом, выходной сигнал состоит из К пар прямой и инвертированной исходной составляющих, отличается фазовым сдвигом, имеет период н 2К раз больший, чем период

ЗО исходной N-значной ПСП, записанной в кольцевом сдвиговом регистре и одинаковое число "единиц" и "нулей" .

Формула изобретения.

Цифровой генератор псевдослучайной последовательности импульсов, содержащий кольцевой регистр, первая группа выходов которого соединена с де®О шифратором, выходом подключенного к входу триггера, логические элементы И, выходы которых соединены с входами. логического элемента ИЛИ, первый выход триггера соединен с первым входом первого логического элемента И, второй выход триггера — с первым входом логического элемента И, о т л и ч а юшийся тем, что, с целью расширения диапазона работы, в него внедены

5g коммутатоР фазы и инвертор, пРичем вторая группа выходов кольцевого регистра соединена с группой управляющих входов коммутатора фазы, вход которого соединен с первым выходом триггера, а выход через инвертор со вторым входом первого логического элемента И, непосредственно — с вторым входом второго логического элемента

И, выход логического элемента ИЛИ соединен с выходной шиной устройства.

60 Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Р 524174, кл. Н 03 К 3/84, 1977.

2. Заявка Франции 9 2504222, 65 кл. Н 03 К>197б.

788357

Сост ави тель В. Ваганов

Техред М. Кузьма

Редактор Н.Кешеля

Корректор О.Ковинская

Подписное

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4

Заказ 8377/69 Тираж 995

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5