Цифровой умножитель частоты

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик (ii)788363

И Е

ИЗОБРЕТЕНИЯ (61) Дополнительное к авт. саид-ву— (22) Заявлено 240179 (21) 2717344/18-21 (51)М. Кл.

Н 03 К 5/01 с присоединением заявки №Государственный комитет

СССР по делам изобретений и открытий (23) Приоритет—

Опубликовано 15,1280, Бюллетень ¹ 48

{53) УДК 621. 374. .4(088.8) Дата опубликования описания 15.1? 80 (72) Авторы изобретения

В. И. Микулович и Н. Н . Скриган (71) Заявитель Белорусский ордена 1рудового Красного Знамени государственный университет им. В.И.Ленина (54 ) ЦИФРОВОЙ УИНО КИТЕЛЪ ЧАСТОТЫ последовательности в пределе, достигающем T„„.

Изобретение относится к измерительной и вычислительной технике и может найти применение в устройствах различного назначения, в частности в устройствах контроля состояния механи — 5 ческих систем с вращающимися частями с помощью электронных методов анализа и измерения частотных составляющих вибраций .

Известно устройство для умножения 10 частоты следования периодических импульсов, содержащее делитель опорной частоты с коэффициентом деления, равным коэффициенту умножения К, счетчик импульсов опорной частоты, счет- 15 чик импульсов, формирователи, запоминающий регистр, два блока переноса и блок управления (1(.

Однако это устройство характеризуется погрешностью дискретности, обусловленной некратностью числа К импульсов генератора опорной частоты f, поступакщих в течение периода Тх входной частоты fq и коэффициента К деления. В результате к кон- 25 цу каждого периода Тх в делителе может остаться число,, представляющее дробную часть частного от деления

М/К, что выражается в погрешности периода следования импульсов выходной

Известен также умножитель частоты следования периодических импульсов, содержащий делитель опорной частоты с коэффициентом деления, равным коэффициенту умножения, счетчик импульсов, счетчик импульсов опорной частоты, формирователи, запоминающий регистр, два блока переноса и блок управления, в него введены дополнительный з апоии н ающий ре гистр, дЕшифр атор, элементы совпадения, линии задержки и элемент ИЛИ, причем выходы делителя опорной частоты подключены к дополнительному запоминающему регистру, выходы которого подключены к входам дешифратора. Выходы дешифратора соединены с первыми входами элементов совпадения, вторые входы которых объединены и подключены к выходу выходного формирователя, выход первого непосредственно, а выходы остальных через линии задержки подключены ко входам элемента ИЛИ. В устройстве для уменьшения погрешности последовательность импульсов с выхода выходного формирователя пропускается через линию с задержкой с, определяемой по соСтоянию

788363 дополнительного регистра дешифрато ром 2) .

Цель изобретения — повышение точности умножения частоты.

Цель достигается тем, что в умножитель частоты, содержащий делитель опорной частоты, последовательно включенные счетчик импульсов, первый запоминающий регистр, блок переноса и счетчик импульсов опорной частоты, причем управляющий вход блока переноса подключен к выходу счетчика импульсов опорной частоты, а также второй запоминающий регистр, входы которого подключены к выходам делителя опорной частоты, блок управления, на вход которого подан входной сигнал, 35 первый выход соединен с установочными входами делителя опорной частоты и счетчика импульсов, второй выход со входами записи регистров, элемент

ИЛИ, линии задержки, элементы совпа- ;щ дения и дешифратор, выходы которого соединены с первыми входами элементов совпадения, вторые входы которых объединены и подключены к выходу счетчика импульсов опорной частоты, выход первого элемента совпадения непосредственно,а выходы остальных через линии задержки подключены ко входам элемента ИЛИ, введены элемент запрета, выход которого подключен к счетному входу счетчика импульсов опорной час- 30 тоты, и сумматор по модулю коэффициента умножения, входы которого подключены к выходам второго запоминающего регистра, тактовый вход — к выходу элемента HJIH, выход сумьы — ко 35 входам дешифратора, а выход переполнения — к первому, входу элемента запрета, на второй вход которого подан опорный сигнал .

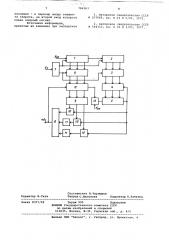

На чертеже представлена структур- 40 ная электрическая схема цифрового умножителя частоты.

Устройство содержит делитель 1 опорной частоты с коэффициентом деления К, счетчик 2 импульсов, образу- 45 емых при делении, первый запоминающий регистр 3, блок 4 переноса, счетчик 5 импульсов опорной частоты, второй запоминающий регистр 6, блок 7 управления, элемент ИЛИ 8, дешифратор 9, элементы 10 совпадения, линии 11 задержки, сумматор 12 по модулю коэффициента умножения К и элемент 13 запрета.

Первый выход блока 7 управления подключен к установочным входам делителя 1 опорной частоты и счетчика 2 импульсов, второй †.к входам за--.èñè регистров 3 и 6. На вход блока 7 управления подан входной сигнал, а на вход делителя 1 — опорный сигнал 40

Информационные выходы делителя 1 подключены К входам регистра б, выходы которого подключены к входам сумматора 12, тактовый вход которого подключен к выходу элемента ИЛИ 8, выход переполнения — к первому входу элемента 13 запрета, на второй вход которого подан опорный сигнал, выходы суммы — к входам дешифратор а 9 . И нформационные выходы счетчика 2 импульсов подключены к входам регистра 3, выходи которого через блок 4 переноса подключены к счетчику 5 импульсов опорной частоты. Тактовый вход счетчика 5 импульсов подключен к выходу элемента 13 запрета, к управляющему входу блока 4 переноса и к объединенным входам элемента 10 совпадения, первые входы которых подключены к выходам дешифратора 9. Выходы элементов 10 совпадения (первого непосредственно, а остальных через линии 11 задержки) подключены к входам элемента ИЛИ 8.

Устройство работает следующим образом.

Каждый импульс умножаемой частоты поступает на вход блока 7 управления, в котором формируется импульс записи информации в регистры 3 и 6 и импульс установки в нулевое состояние делителя 1 и счетчика 2. Импульсы с выхода делителя 1, частота следования которых равна f /К, подаются на вход счетчика 2. За один период Т) умножаемой частоты f< на вход счетчика 2 поступает число импульсов, авное р Оп

Ик= Гх—

К

При этом в делителе 1 к концу периода Т g образуется остаточное число

m, обусловленное некратностью числа N импульсов опорной частоты,,поступивших на вход делителя 1 эа время Т, коэффициенту деления К(а4К).

Чйсло N после поступления очередного импульса умножаемой частоты переписывается в регистр 3, одновременно (этим же сигналом) число m иэ делителя 1 переписывается в регистр б и пОступает на вход накапливакщего сумматора 12.

Импульсы опорной частоты непрерывно поступают через элемент 13 запрета на вход счетчика 5 импульсов опорной частоты, который работает в режиме вычитания и уменьшает записанное в нем число. Как только состояние всех триггеров счетчика станет нулевым, на выходе его появляется импульс, который, поступая на управляющий вход блока 4 переноса, осуществляет перенос числа и из регистра 3 в счетчик

5. В результате на выходе счетчика 5 образуется последовательность импульсов с периодом (в случае m=0) Vr

Однако, если вф0, период импульс в на выходе счетчика 5 оказывается меньше требуемого значения и величина ошй0 3 и опр.-:дел Р - -,." т чс р: -.б re

78836З п1

Т = — — — 7 =T- — 7

on, оп

Отсюда

15 тх аых х 1оп

Т

ВЫx

Т=Т + — Т

fYI

К Оп

Таким образом, если увеличить период следования импульсов на выходе счетчика 5 на величину m P и то оп ° погрешност ь дискретности будет умен ьшена. Для этого необходимо задержать первый импульс с выхода счетчика 5 на время — Toï, второй — на — Т г и g ttl 10 третий — на — -Т „и т.д. В этом

3v случае период следования импульсов на выходе устройства будет иметь значение

Корректировка периода выходной импульсной последовательности осуществляется следующим образом. 20

Первый импульс с выхода счетчика 5 поступает на входы элементов 10 совпадения. Дешифратор 9 анализирует состояние сумматора 12, на выходах суммы которого будет число m, и выдает разрешающий потенциал на вход соответствующего элемента 10 совпадения. Число выходных шин дешифратора 9 определяется тем, во сколько "n" раз необходимо уменьшить погрешность дискретности периода на выходе устройства, и может достигать значения К.

При этом, если m (К/и то разрешающий потенциал появляется на первом входе того элемента 10 совпадения, который непосредственно связан со входом элемента ИЛИ 8. При К/и и m (2K/п разрешающий потенциал появляется на шине дешифратора 9, связанный с элементом 10 совпадения, выход которого соединен с элементом ИЛИ 8 через линию 40

11 .задержки с временем задержки г,-70gg, при 2 К/n m a 3К/и соединение происходит через линию 11 задержки с временегл задержки 2 г, и т.д. Таким образом, первый импульс на выходе уст- 45 ройства появится с задержкой, пропорциональной значению числа m. Поступая на тактовый вход накапливающего сумматора 12 этот импульс прибавляет умме и Ha aaaxoztax cyme 50 сумматора 12 появляется число m Состояние дешифратора 9 изменяется и второй импульс с выхода счетчика 5 получает задержку, пропорциональную 2m, третий — пропорциональную 3m, четвертый — 4m и т.д. Если на каком-либо этапе работы устройства число im где i — номер очередного импульса, превысит число К, то на выходе переполнения сумматора появляется импульс переполнения, который означает, что щ следующий импульс с выхода счетчика

5 необходимо задержать на величину, большую,чем Топ Элемент 13 запрета по сигналу переполнения запрещает

Р;, н импульс последовательности хогг, 5 что эквивалентно задержке очередного импульса с выхода счетчика 5 на величину Тпгг . С помощью дешифратора 9, элементов 10 совпадения и линий 11 задержки осуществляется дополнительная задержка этого импульса на величину, пропорциональную остатку числа в сумматоре

4.

m = im — К.

Аналогичным образом осуществляет"я коррекция временного положения последующих импульсов и при

m t I

Ф элемент. 13 запрета опять исключает один импульс из последовательности на входе счетчика 5.

Таким образом, период повторения импульсов на выходе элемента ИЛИ 8 будет определяться, с учетом максимальнои погрешности, выражением т. е. максимальная погрешность дискретности уменьшается . формула изобретения

Цифровой углножитель частоты, со держащий делитель опорной частоты, последовательно включенные счетчик иглпульсов, первын запоминающий регистр, блок переноса и счетчик импульсов опорной частоты, причем управляющий вход блока переноса подключен к выхоцу счетчика импульсов опорной частоты, а также второй запоминающий регистр, входы которого подключены к выходам целителя опорной частоты, блок управления, на вход которого подан входной сигнал, первый выход соединен с установочными входами делителя опорной частоты и счетчика импульсов, второй выход — со входами записи первого и второго запоминающих регистров, элемент ИЛИ, линии задержки, элементы совпадения и дешифратор, выходы которого соединены с первыми входами элементов совпадения, вторые входы которых объединены и подключены к выходу счетчика импульсов опорной частоты, выход первого элемента совпадения непосредственно, а выходы остальных через линии задержки подключены ко входам элемента ИЛИ, о тл и ч а ю шийся тем, что, с целью повышения точности умножения, в него введены элемент запрета, выход которого подключен к счетному входу счетчика импульсов опорной частоты, и накапливающий сумматор по модулю коэффициента умножения, входы которого подключены к выходам второго запоминающегося регистра, тактовый вход к выходу элемента ИЛИ, выход сумьы ко входам дешифратора, а вцход пера788363

Составитель В.Чернышев

Техред С.Мигунова Корректор Н.Бабинец

Редактор М.Ткач

Тираж 995 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж35, Раушская наб., д. 4/5

Эакаэ 8377/69

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4 полнения — к первому входу элемента запрета, на второй вход которого подан опорный сигнал.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

М 357668, кл. Н 03 К 5/01, 1972.

2. Авторское свидетельство СССР

9 544112, кл. Н 03 К 5/01, 1977.