Быстродействующий аналого-цифровой преобразователь

Иллюстрации

Показать всеРеферат

Союз Советских

Сс1циалистических

Республик

ОП И

ИЗОБРЕТЕНИЯ о>788373

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву(22) Заявлено 27.0779 (21) 2649377/18-21 с присоединением заявки ¹ (23) Приоритет—

Опубликовано 151280, Бюллетень ¹ 46

Дата опубликования описания 151280

Р1)М. К .

Н 03 К 13/08

Государственный комитет

СССР по делам изобретений и открытий (53) УДК 681. 325 (088. 8) (72) Автор . изобретения

Н.А. Филиппов (71) 3а яв и тель

Фрунзенский политехнический институт (54 ) БЫСТРОДЕЙСТВУЮЩИЙ АНАЛОГО-ЦИФРОВОЙ ПР ЕОБР АЗОВАТЕЛ Ь

Изобретение относится к измерительной технике для измерения быстроизменяющихся напряжений.

Известен кодирующий преобразователь напряжения в код, содержащий блоки сравнения, элементы, фиксирующие значение данного разряда, источник образцового напряжения и узлы уравновешивания значения измеряемой величины с образцовым значением очередного разряда 1(. Недостатком йреобразователя является низкая вероятность его правильной работы вследствие использованного принципа самозапуска его тактов работы (изменение измеряемого напряжения за пределы кванта вызывает автоматический запуск любого такта работы известного,(АЦП). Это приводит к то- 20 му, что при интервалах времени изменения измеряемого напряжения на один квант меньших или равных, чем интервал времени полного преобразования АЦП, его все показания будут недостоверными (не успев выдать результат измерения, он начнет новое измерение или частичное переизмерение).

Цель изобретения — повышение точности преобразования.

Дель достигается тем, что в быстродействующий аналого-цифровой преобразователь, содержащий блоки сравнения, первые входы которых соединены с шиной входного сигнала, а вторые входы соединены с выходами соответствующих делителей образцового напряжения, входы которых соединены с шиной образцового напряжения, при этом единичные выходы блоков сравнения каждого разряда через дешифраторы знаков разрядов соединены с управляющими входами делителей образцового напряжения следующего разряда, введены диоды, элемент И, элемент НЕ, элемент задержки и выходные элементы И, причем первый и второй выходы блоков сравнения соединены с анодами диодов, катоды которых объединены и подключены ко входам элемента И, выход которого соединен с первым входом элемента задержки и через элемент НЕ с его входом, выход которого соединен с первыми входами выходных элементов И, вторые входы которых соединены с шиной опроса, а третьи входы выходных элементов И каждого разряда соединены с соответствующими выходами дешифратора знака ссютветствующего разряда.

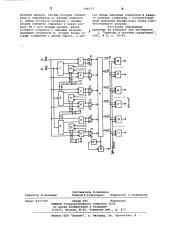

788373

На чертеже представлена структурная электрическая схема быстродействующего аналого-цифрового преобразователя, содержащего блоки сравнения 1,2,3,4,5,6, / делители образцового напряжения 7, 8, 9, диод 10, элемент И 11, элемент НЕ 12, элемент задержки 13, выходные элементы И 14, 15,16,17,18,19, дешифраторы знаков разрядов 20,21,22, шина входного сигнала 23, шина образцового напряжения 24, шина опроса 25.

Работа быстродействующего аналого-цифрового преОбразователя осуществляется следующим образом.

После подачи на него измеряемого напряжения Ох и образцового 0 подача местного питания (на чертеже не показано) приводит к одновременному срабатыванию всех его сравнивающих блоков 1-6 и, как следствие этого, срабатывают все связанные с ними дешифраторы знаков 20,21,22 каждых раз- Ю рядов. Последнее приводит к изменению состояния делителей 8,9, формирующих образцовые напряжения (изменяются состояния всех делителей, кроме старшего 7). Это заставит в случае изменения состояний делителей 8, 9 изменить состояние сравнивающих блоков 3,4,5,6. Примут новые состояния дешифраторы 21,22 и, как следствие этого, делитель 9 сформирует новые значения образцовых величин. Это заставит. изменить состояние сравнивающих блоков 5,6. Аналогичным образом волна дискретного уравновешивания, в каком бы она разряде не возникла, пробежит в сторону младшего разряда.

При этом с изменением состояния любого одного сравнивающего блока на вход логического элемента И 11 на время этого переходного режима не будет подано высокое напряжение. С выхода 40 логического элемента И 11 на вход логического элемента НЕ 12 за этот интервал времени не будет подано высокое напряжение (единица), отчего с выхода логического элемента НЕ 12 бу- дет подан сбросной сигнал на элемент задержки 13 и последний придет в исходное положение. При восстановлении на выходе логического элемента И 11 единицы, а на выходе логического эле- ( мента НЕ 12 нуля, элемент задержки 13 начнет новый отсчет времени задержки, не подавая при этом разрешающего сигнала на описывание результата преобразования. И только в случае, если волна дискретного уравновешивания не возобновится, элемент задержки 13 зафиксирует этот факт на время, превышающее наибольший интервал между одноименными точками переходного режима соседних разрядов при непрерывном ус- 60 танавливающемся режиме преобразователя и выдаст разрешающий сигнал на считывание результата дискретного уравновешивания. Это разрешение будет продолжаться до тех пор, пока с вы- 45 хода элемента И 11 будет выдават ься высокое напряжение (единица). Начало изменения состояния хотя бы одного сравнивающего устройства, являющееся следствием нарушения дискретного равновесия, ведет к прекращению выдачи результата преобразования минимум на время задержки элемента 13. Цифры кода результата дискретного уравновешивания, выявленные дешифраторами

20,21,22 знаков разрядов, подаются с последних на один из трех входов каждого логического элемента И 14-19 и при наличии на их вторых входах разрешающего потенциала элемента задержки 13 и подаче опросного сигнала на их третьи входы снимается с них результат дискретного уравновешивания.

Преимущество быстродействующего аналого-цифрового преобразователя состоит в том, что в нем при сохранении высокого быстродействия исключена выдача ложных результатов измерительного преобразования. Это обусловле но тем, что результат преобразования выдается только после того, как установится факт прекращения переходного режима дискретного уравновешивания и выдаст разрешение на его считывание.

Преобразователь может успешно использоваться при определенных частотных характеристиках измеряемого сигнала в следящем режиме. Он обеспечивает получение достоверной информации о значениях быстропротекающих процессов, изменяющихся в большом динамическом диапазоне или с большим количеством уровней, которые невозможно перекрыть однотактным аналого-цифровым преобразователем. Структура преобразователя пригодна как для равномерного квантования, так и для неравномерного, в частности по геометрической прогрессии, необходимой для равноточных измерений.

Формула изобретения

Быстродействующий аналого-цифровой преобразователь, содержащий блоки сравнения, первые входы которых соединены с шиной входного сигнала, а вторые входы соедннены с выходами соответствующих делителей образцового напряжения, входы которых соединены с шиной образцового напряжения, при этом единичные выходы блоков сравнения каждого разряда через дешифраторы знаков разрядов соединены с управляющими входами делителей образцового напряжения следующего разряда, отличающийся тем, что, с целью повышения точности преобразования, введены диоды, элемент И, элемент НЕ, элемент задержки и выходные элементы И, причем первый и второй выходы блоков сравнения соединены с

788373

Составитель Л. Беляева

Техред;Е.Гаврилешко -Корректор О.Ковинская

Редактор М. Келемеш

Тираж 995 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ 8377/69

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4 ° анодами диодов, катоды которых объединены и подключены ко входам элемента

И, выход которого соединен с первым входом элемента задержки и через элемент НЕ с его вторым входом, выход которого соединен с первыми входами выходных элементов И, вторые входы,которых соединены с шиной опроса, а третьи входы выходных элементов К каждо« го разряда соединены с соответствуюшими выходами дешифратора знака соответствующего разряда.

Источники информации принятые во внимание при экспеРтиэе

1. "Приборы и системы управления", 1969, М 9, с. 39-42.