Преобразователь интервала времени в цифровой код

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советскик

Социалисткческик

Реслублмк ()788375 (61) Дополнительное к авт. свид-ву— (22) Заявлено 18.12.78 (21) 2697604/18-21 с присоединением заявки №вЂ” (23) Приоритет— (51) М. Кл. з

Н 03 К 13/20Ц(G OCI F 10/04

Государственный комитет

СССР

Опубликовано 15.12.80. Бюллетень № 46

Дата опубликования описания 25.12.80 (53) УДК 621.317..76 (088.8) по делам изобретений и открытий (72) Авторы изобретения

В. И. Мяснов и В. Б. Смирнов (71) Заявитель (54) ПРЕОБРАЗОВАТЕЛЬ ИНТЕРВАЛА ВРЕМЕНИ

В ЦИФРОВОЙ КОД

Изобретение относится к электроизмерительной технике и может быть использовано для преобразования интервала времени в цифровой код.

Известен преобразователь интервала времени в цифровой код, содержащий m-тактный генератор эталонной частоты f, схему управления, состоящую, например, из m электронных ключей, управляемых старт- и стопимпульсами, m-тактный счетчик, имеющий

m счетных каналов, каждый из которых включен на соответствующий выход схемы управления, однотактный счетчик и схему переноса, связывающую m-тактный счетчик со входом однотактного счетчика (1).

Недостатком известного устройства является высокая частота переключения элементов схемы переноса и триггера младшего разряда однотактного счетчика.

Известен преобразователь интервала времени в цифровой код, содержащий m-тактный генератор эталонной частоты, выходы которого подключены ко входам блока управления, выходы которого соединены со счетными входами разрядных триггеров mтактного счетчика, однотактный счетчик (2).

Недостатком этого преобразователя интервала времени в цифровой код является необходимость применения быстродействующих элементов при m )2, что приводит к снижению надежности.

Цель изобретения — повышение надежности.

Поставленная цель достигается тем, что в преобразователь интервала времени в цифровой код, содержащий m-тактный генератор эталонной частоты, выходы которого

1о подключены ко входам блока управления, выходы которого соединены со счетными входами разрядных триггеров m-тактного счетчика, однотактный счетчик, введены два mвходовых логических элемента И-ИЛИ и — пар четырехвходовых логических элементов И-ИЛИ, прямые входы одного четырехвходового логического элемента И-ИЛИ в каждой паре соединены с прямыми выходами соответствующей пары разрядных триггеров m-тактного счетчика, прямые входы другого четырехвходового логического элемента И-ИЛИ каждой пары соединены с инверсными выходами этой же пары разрядных триггеров m-тактного счетчика, выход каждого четырехвходового логического

788375

S0

Формула изобретения элемента И-ИЛИ в каждой паре соединен с инверсными входами другого четырехвходового логического элемента И-ИЛИ этой же пары, причем выходы первых четырехвходовых логических элементов И-ИЛИ всех пар соединены с прямыми входами первого

m-входового логического элемента И-ИЛИ, выходы вторых четырехвходовых логических элементов И-ИЛИ всех пар соединены с прямыми входами второго m-входового логического элемента И-ИЛИ, выход каждого из m-входовых логических элементов ИИЛИ соединен с инверсными входами другого, выход первого m-входового логического элемента И-ИЛИ соединен со входом однотактного счетчика.

В предлагаемом устройстве независимо от количества тактов m максимальная частота переключения элементов не превысит значения f, а длительность импульса переноса будет равна т .

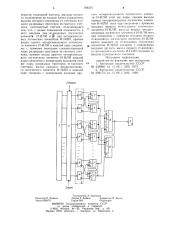

На чертеже представлена схема преобразователя интервала времени в цифровой код.

Схема содержит m-тактный генератор эталонной частоты 1, блок управления 2, управляемый старт- и стоп-импульсами, m-тактный счетчик 3, имеющий m разрядных триггеров 4 со счетным входом, однотактный счетчик 5, два m-входовых логических элемента И-ИЛИ 6, у пар четырехвходовых логических элементов И-ИЛИ 7.

При поступлении в блок управления 2 старт-импульса на его выходах появляются импульсы m-тактного генератора эталонной частоты 1, которые поступают на счетные входы соответствующих разрядных триггеров 4 m-тактного счетчика. Разрядные триггеры 4 объединены в пары, на счетные входы разрядных триггеров 4 каждой пары с соответствующего выхода блока управления 2 поступают противофазные сигналы. На прямые входы одного четырехвходового логического элемента И-ИЛИ 7 в каждой паре подаются сигналы с прямых выходов соотетствующей пары разрядных триггеров 4, на входы которых поступают противофазные сигналы с соответствующего выхода блока управления 2, а на прямые входы другого четырехвходового логического элемента

И-ИЛИ каждой пары подаются сигналы с инверсных выходов этой же пары разрядных триггеров 4. Изменение сигналов на выходах каждого четырехвходового логического элемента И-ИЛИ 7 в каждой паре происходит в моменты времени, когда соединенные с ними соответствующие разрядные триггеры 4 оказываются или в состоянии логического нуля, или в состоянии логической единицы. 3а счет цепи обратной связи, связывающей выход каждого четырехвходового логического элемента И-ИЛИ 7 в каждой паре с инверсными входами другого четырехвходового логического элемента И-ИЛИ 7 в той же паре, это состояние сохраняется

Зо

40 до момента очередного совпадения сигналов на прямых выходах другого четырехвходового логического элемента И-ИЛИ 7 этой же пары. Выходные сигналы с первых четырехвходовых логических элементов ИИЛИ 7 всех пар поступают на прямые входы первого m-входового логического элемента ИИЛИ 6, а выходные сигналы со вторых четырехвходовых логических элементов ИИЛИ 7 всех пар поступают на прямые входы второго m-входового логического элемента И-ИЛИ 6. При совпадении сигналов на прямых входах первого или второго m-входового логического элемента И-ИЛИ 6, которое происходит в моменты совпадения сигналов на выходах соответственно первых или вторых четырехвходовых логических элементов И-ИЛИ 7 всех пар, изменяется сигнал на противоположный на выходах каждого m-входового логического элемента ИИЛИ 6. Это состояние за счет цепи обратной связи, связывающей выход каждого mвходового логического элемента И-ИЛИ 6 с инверсными входами другого m-входового логического элемента И-ИЛИ 6, сохраняется до очередного момента совпадения сигналов на прямых входах другого m-входового логического элемента И-ИЛИ 6. Период сигналов на выходе каждого m-входового логического элемента И-ИЛИ 6, так же, как и на выходе каждого четырехвходового логического элемента И-ИЛИ 7, равен 2т;.

Форма сигналов на указанных выходах— меандр, т.е. длительность импульса переноса независимо от. количества тактов будет равнаТ. Сигнал с выхода первого m-входового логического элемента И-ИЛИ 6 поступает на счетный вход однотактного счетчика 5. В момент поступления в блок управления 2 стопимпульса прекращается подача эталонной частоты на входы разрядных триггеров 4. Результат преобразования фиксируется в однотактном счетчике 5, в m-входовых логических элементах И-ИЛИ 6 и в разрядных триггерах 4 с дискретностью †. Суммарная максимальная

Х погрешность дискретности такого преобразователя интервала времени в цифровой код равна

6= ++

В предлагаемом преобразователе интервала времени в цифровой код можно получить погрешность - —,„на элементах с предельной частотой переключения, равной (для разрядных триггеров 4) и равной (для элементов 6, 7) и однотактного счетчика 5. Отсутствие быстродействующих элементов приводит к уменьшению потребляемой мощности и упрощению устройства, что и обеспечивает повышение надежности преобразователя интервала времени в цифровой код.

Преобразователь интервала времени в цифровой код, содержащий m-тактный ге788375

Cmu)re

Crnurr

С оста вит ель Л. Плетнев а

Редактор Н. Кешеля Техред А. Бойкас Корректор М. Коста

Заказ 8380/70 Тираж 995 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, )Ь,— 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4 нератор эталонной частоты, выходы которого подключены ко входам блока управления, выходы которого соединены со счетными входами разрядных триггеров m-тактного счетчика, однотактный счетчик, отличающийся тем, что, с целью повышения надежности, в него введены два m-входовых логических элемента И-ИЛИ и пар четырехвходоz вых логических элементов И-ИЛИ, прямые входы одного четырехвходового логического элемента И-ИЛИ в каждой паре соединены с прямыми выходами соответствующей пары разрядных триггеров m-тактного счетчика, прямые входы другого четырехвходового логического элемента И-ИЛИ каждой пары соединены с инверсными выходами этой же пары разрядных триггеров m-тактного счетчика, выход каждого четырехвходового логического элемента И-ИЛИ в каждой паре соединен с инверсными входами другого четырехвходового логического элемента И-ИЛИ этой же пары, причем выходы первых четырехвходовых логических элемен тов И-ИЛИ всех пар соединены с прямыми входами первого m-nvozoaoro логического элемента И-ИЛИ, выходы вторых четырехвходовых логических элементов И-ИЛИ всех пар соединены с прямыми входами второго

m-входово-о логического элемента И-ИЛИ, выход каждого из m-входовых логических элементов И-ИЛИ соединен с инверсными входами другого, выход первого m-входового логического элемента И-ИЛИ соединен со входом однотактного счетчика.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 438998, кл. G 06 J 3/00, 1972.

2. Авторское свидетельство СССР № 292173, кл. G 06 J 3/00, !969.