Устройство для измерения среднеквадратического значения напряжения случайного сигнала

Иллюстрации

Показать всеРеферат

Сеюз Севета4ик

СациаеФстищеатик

Раавублж (61) Дололиительиое к ант. сеид-ву (22) заявлено 180778 {2)) 2645Я21/13-21 с присоединением звнвки 4о (23) Приоритет

Опубликовано Э и 230. Бюллетень Не 4 7/

Дате ол бликоваиин описания 2 31 230

G O> Я 1e/02

Гюсумрстненнмй коянтет

АЗССР ю давая нзобретеннй и етнрмтнв (53) УДК 681. 325 (088 ° 8} (72) Авторы изабретеиил

Н,A. Дрязгов, В,В, Ионас и П.Т, Толмачев

/ (7! ) Завеитель (54 ) УСТРОИСТВО QJIR И йЕРЕНИЯ

СРЕДНЕКВАДРАТИЧЕСКОГО ЗНАЧЕНИЯ

НАПРЯЖЕНИЯ СЛУЧАЙНОГО СИГНАЛА

Изобретение относится к измерительной технике и может быть использовано в системах контроля и анализа параметров случайных процессов.

Известно устройство для измерения среднеквадратического значения напряжения случайного сигнала, содержащее мостовые схемы с термочувствительными элементами, усилители с цепями обратной связи и регулируемыми коэффициентами усиления (Ц .

Недостатком является малый измерительный динамический диапазон измеряемых сигналов.

Известно устройство для измерения среднеквадратического значения напряжения случайного сигнала, содержащее последовательно соединенные логарифмический усилитель, детектор, интегратор, блок коррекции и индикатор, причем другой вход блока коррекции подключен к выходу детектора E2i .

Однако устройство имеет недостаточную точность измерения и ограниченные функциональные возможности.

Цель изобретения — повышение точности измерения и расширение функциональных возможностей.

Укаэанная цель достигается тем, что в устройство для измерения среднеквадратического значения напряжения случайного сигнала, содержащее амп% литудный детектор, логарифмический усилитель, блок индикации, введены аналого-цифровой преобразователь, коммутатор, реверсинный счетчик, оперативное запоминающее устройство, i0 триггер записи, элемент И, счетчик результата, элемент запрета, форми-. рователь, блок управления, дешифратор, счетчик числа отсчетов, триггер режима, причем выход амплитудного

$5 детектора через последовательно соединенные аналого-цифровой преобразователь, коммутатор, реверсивный счетчик, оперативное запоминающее устройство, триггер записи, элемент

2О И и счетчик результата соединен с входами блока индикации, выход реверсивного счетчика через дешифратор соединен с первыми входами счетчика числа отсчетов и триггера= режима, 25 второй вход которого соединен с выходом счетчика числа отсчетов, второй вход которого соединен с управляющими входами аналого-цифрового преобразо-. вателя и элемента запрета и первым

Я выходом блока управления, выход

789787,триггера режима соединен со входами элемента запрета и формирователя, управляющими вхоцами блока управления, триггера записи, вторым входом реверсивного счетчика, управляющий вход которого соединен со вторым выходом блока управления, третий и четвертый выходы которого соединены с входами управления оперативного запоминающего устройства, выход которого соединен с входом блока управления, пятый выход которого соединен со вторым входом элемента

И, а выходы элемента запрета и формирователя соединены с входами коммутатора и вторым входом счетчика результата.

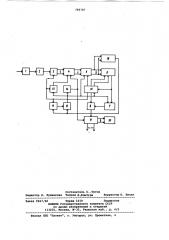

Иа чертеже изображена электрическая схема устройства.

Устройство содержит логарифмический усилитель 1, амилитудный детектор 2, аналого-цифровой преобразователь 3, коммутатор 4, реверсивный счетчик 5, оперативное запоминающее устройство 6, триггер 7 записи, элемент 8 И, счетчик 9 результата, блок 1О индикации, счетчик 11 числа отсчетов, триггер 12 режима, элемент

13 запрета, формирователь 14, блок

15 управления и дешифратор 16

Устройство работает следующим образом.

Измеряемый сигнал поступает на вход логарифмического усилителя 1, сжимающего его динамический диапазон.

Сигнал с выхода логарифмического усилителя через амплитудный детектор 2 поступает на вход аналогоцифрового преобразователя 3, который вырабатывает двоичный код числа И > пропорционального максимальному значению измеряемого напряжения входного сигнала в i-ой точке отсчета, выраженному в децибелах. Частота дискретизации аналогового сигнала в аналого-цифровом преобразователе 3 определяется частотой импульсов опроса, поступающих на его вход из блока 15.

В начале цикла измерения счетчик

11, реверсивный счетчик 5, триггер .12 и триггер 7 установлены в нулевое состояние,, а в ячейках оперативного запоминающего устройства 6 записаны

"нули". Сигнал с выхода триггера 12 определяет режим записи, при этом первый импульс опроса с выхода блока 15 поступает через элемент 13 на вход .перезаписи коммутатора 4 и переписывает код и с выходов аналого-цифрового преобразователя 3 в реверсивный счетчик 5, состояние которого определяет адрес Ag выбранной ячейки оперативного запоминающего устройства 6, иа выходе которого появляется записанный в ячейке по. тенциал "нуля", который поступает на управляющий вход блока 15. Блок

15 вырабатывает сигналы записи

"единицы" в ячейку A, которые поступают.на информационный и синхронизирующий входы оперативного запоминающего устройства 6.

Операция суммирования квадратов напряжений реализуется в оперативном запоминающем устройстве 6 следующим образом: i-ый импульс опроса с выхода блока 15 поступает на вход перезаписи коммутатора 4 через эле-. мент 13 запрета, переписывает код @ числа и с выходов аналого-цифрового

1 преобразователя 3 в реверсивный счетчик 5, при этом, если в ячейке

А . был ранее записан "нуль", то в йее записывается "единица". Если

35 в ячейке оперативного запоминающего

jjcTpoAcTBB. 6 по адресу Ag. была за1 писана "единица", то на его выходе появляется потенциал "единицы", и блок 15 сначала вырабатывает сигналы

gg записи "нуля" в эту ячейку, а затем импульс счета адреса, который поступает на счетный выход реверсивного счетчика 5 и устанавливает его в состояние й; + 1. Аналогично, если в ячейке й„ + 1 был записан "нуль", то в нее записывается "единица", если же была записана "единица", в нее записывается "нуль", а реверсивный счетчик 5 устанавливается в состояние К;+ 2 (перенос "единицы" в старший разряд суммы } и т.д. Таким образом, в оперативном запоминающем устройстве 6 реализуется операция поразрядного сложения двоичных чисел, Счетчик 11 подсчитывает импульсы

ЗЗ опроса и по окончании и = 2 импульк сов вырабатывает сигнал, устанавливающий триггер 12 в единичное состояние, соответствующее режиму считывания. ц Сигнал с выхода триггера 12 запрещает прохождение импульсов опроса через элемент 13 на вход коммутатора

4, переключает реверсивный счетчик

5 в режим "вычитание", снимает сигнал установки в нулевое состояние со входа триггера 7, Кроме того, по фронту сигнала с выхода триггера

12 формирователь 14 вырабатывает импульс записи, устанавливающий счетчик 9 в состояние "k" а также записывающий в реверсивный счетчик 5 код постоянного числа, которое вырабатывается коммутатором 4. Число

М выбирается большим или равным максимальному адресу ячейки ОЗУ, 55 в которую может быть записана "единица" при суммировании.

При поступлении сигнала с выхода триггера 12 блок 15 начинает вырабатывать импульсы счета адреса и сигна60 лы записи "нуля" в оперативное запоминающее устройство 6, при этом последовательно опрашиваются и обнуляются ячейки A A ..., Л„, I

При установке реверсивного счет65:чика 5 на адрес А единицы старшего разряда суммы сигнал с выхода опера- тивного запоминающего устройства 6 устанавливает триггер 7 в единичное: состояние, при этом сигнал с выхода триггера 7 разрешает поступление импульсов счета результата с выхода блока 15 через элемент 8 И на счетный вход счетчика 9.

При достижении реверсивным счетчикам адреса A>(j = ) дешифратор вырабатывает импульс сброса, устанавливающий в нулевое состояние счетчик 11 и триггер 12. Сигнал с выхода триггера 12 переводит устройства в режим записи, при этом триггер устанавливается в нулевое состояние и поступление импульсов на счетчик 9 прекращается. C переходом в режим записи начинается новый цикл измерения, аналогичный описанному выше.

Частота импульсов счета результата выбирается в три раза больше частоты импульсов счета адреса.

Кад, записанный в счетчике 9, поступает в блок 10, в котором отображается среднеквадратическое значение напряжения измеряемого случайного сигнала.

Таким образам, устройства позволяет повысить точность измерения среднеквадратическага значения напряжения, при этом точность измерения не зависит ат вида распределения уровней случайных сигналов.

Формула изобретения

Устройство для измерения среднеквадратического значения напряжения случайного сигнала, содержащее последовательно соединенные логарифмический усилитель и амплитудный детектор, а также блок индикации, а т л и ч а ю щ е е с я тем, чта, с целью повышения точности измерения

s расширения функциональных возмажнастей, введены аналого-цифровой преобразователь, коммутатор, реверсивный счетчик, оперативное запоминающее устройство, триггер записи, элемент И, счетчик результата, элемент запрета, формирователь, блок управления, дешифратор, счетчик числа отсчетов, триггер режима, причем выход амплитудного детектора через последовательна соединенные аналого-цифровой преобразователь, коммутатор, реверсивный счетчик,оперативное запоминающее устройство, триггер записи, элемент И и счетчик результата соединен с входами блока индикации, выход реверсивного счетt5 чика через дешифратор соединен с первыми входами счетчика числа отсчетов и триггера режима, второй вход которого соединен с выходом счетчика числа отсчетов, второй вход котарога

2О соединен с управляющими входами аналога-цифравага преобразователя и элемента запрета и первым выходам блока управления, выход триггера режима соединен са входами элемента запрета и формирователя, управляющими входами блока управления, триггера записи, вторым входом реверсивного счетчика, управляющий вход которого соединен со вторим выходом блока управления, третий и четвертый

30 выходы которого соединены с входами управления аперативнага запоминающего устройства, выход которого соединен с входом блока управления,пятый выход которого соединен со вторым

35 входам элемента И, а выходы элемента запрета и формирователя соединены с входами коммутатора и вторым входом счетчика результата.

Источники информации, принятые ва внимание при экспертизе

1. Патент Великобритании Ф 1364909, л. С а В 19 00, 1978.

2. Авторское свидетельство СССР

9 402813, кл. С 01 R 19/02, 1972 (прототип).

789787

Составитель A. Титов

Редактор Е. Лушникова Техред M,Кошара Корректор О. Билак

Заказ 9027/40 Тираж 1019 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж«35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгорол, ул. Проектная, 4