Устройство для сравнения фаз двух электрических величин

Иллюстрации

Показать всеРеферат

"оная

-С- jrн- ""

ОПИ НЕ

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистических

Республик рн790061

К АВТОРСКОМУ СВИДЕТЕЛВСТВУ

H H 3/38

Н 01 Н 83/16 с присоединением заявки ¹ (23) Приоритет

Государственный комитет

СССР по делам изобретений и открытия

Опубликовано 231280 Бюллетень ¹ 47 (53) УДН 621. 316. .925(088.8)

Дата опубликования описания 25.1280 (72) Авторы изобретения

В. Г. Бодунов, Г. Ф. Петренко и В. К. Скрипко (71) Заявитель

Омский политехнический институт (54) УСТРОЙСТВО ДЛЯ СРАВНЕНИЯ ФАЗ ДВУХ

ЭЛЕКТРИЧЕСКИХ ВЕЛИЧИН рователи, элементы 2 И-НЕ и первый триггер подключены таким образом, что в зависимости от фаз входных величин на одном или другом вхо- де второго R-5 триггера постоянно имеет место сигнал "1", а на другой вход один, раз в период, а именно, в момент совпадения положительных сигналов с формирователей, подаются установочные импульсы ("О") j2).

Однако при наличии на входе в определенный момент времени сигнала помехи происходит переброс выходного триггера, а установка его в исходное состояние происходит в течение периода сравниваемых сигналов, по приходу установочных импульсов.

Цель изобретения — повышение помехоустойчивости устройства.

Поставленная цель достигается тем, что в устройство для сравнения фаз двух электрических величин, содержащее первый и второй формирователи электрических величин, на входы которых подаются сравниваемые величины, а выходы подключены соответственно ко входам S u R первого R S триггера, выход О которого подключен к одному из входов первого элемента

2И-HE, выход О подключен к одному из

Изобретение относится к электротехнике и-может быть использовано для построения измерительных органов на основе сравнения по фазе двух электрических величин.

Известны устройства, реагирующие на разность фаз двух электрических величин, содержащие формирователи входных величин и блоки сравнения, выполненные на логических элементах, 10 в которых, с целью повьхаения быстродействия и помехоустойчивости, блок сравнения выполнен из двух каналов, входы которйх подключены к формирователям, а выходы — к логическим эле- 1$ ментам И или ИЛИ, выходы которых являются выходом устройства. При этом сравниваются импульсы как положительных, так и отрицательных полярностей входных сигналов f1). 20

Однако указанные устройства отличаются сложностью конструкции.

Наиболее близким по своей технической сущности к предлагаемому является устройство, содержащее форми- 2з рователи электрических величин, на входы которых подают сравниваемые величины, и логический блок, выполненный в виду двух R-5 триггеров и двух элементов 2И-HE При этом форми- 30 (61) Дополнительное к авт, сеид-ву (22) Заявлено 180 79 (21) 2715281/24-07 (5f ) M

790061 входов второго элемента 2И-НЕ, а выходы первого и второго элементов

2И-НЕ подключены соответственно ко входам S u R второго R S триггера, выходы которого являются выходом устройства дополнительно введены третий 2.-5 триггер и два инвертора, причем нходы первого и второго инверторов подключены соответственно к выходам первого и нторого формиро-, .вателей, а выходы подключены ко входам S u R третьего R-S триггера, выходы Q u Q которого подключены соответственно к другим входам первого и второго элементов 2И-НЕ.

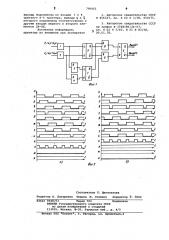

На фиг. 1 приведена функциональная схема устройства на фиг. 2 15 диаграммы а и б, поясняющие его работу.

Устройство содержит два фбрмиронателя 1 и 2, которые предназначены для получения прямоугольных импуль- щ сов со скважностью 2 из входных синусоидальных сигналов, два инвертора 3 и 4, которые предназначены для инвертирования сигнала, поступающего с формирователей 1 и 2, три к.-S 25 триггера 5, 6 и 7, первый из которых 5 изменяет свое состояние н зависимости от импульсов, поступающих с формирователей 1 и 2, второй б — н зависимости от импульсов, поступающих с логических элементов 2И-HE 8 30 и 9, на входы которых подаются сигналы с первого 5 и третьего 7 R-S триггеров, а третий R- S триггер 7 изменяет свое состояние в зависимости от импульсов, поступающих с двух инвер- 35 торов 3 и 4.

На фиг. 2 а рассмотрен режим работы устройства, когда синусоидальная величина Е опережает по фазе величину Е, а на фиг. 2 б — когда Е 40 отстает по фазе относительно Е . При этом на фиг. 2 а и 2 б обозначены сигналы с выходов элементов: а — формирователя 1, б — формирователя 2, в

Q триггера 5,,г — Q триггера 5, д— инвертора 3, Ж вЂ” инвертора 4, з — Я триггера 7, и — Q триггера 7, к элемента 2И вЂ” НЕ 8, л — элемента 2ИНЕ 9, м - Q триггера б, н — Q триггера 6.

$0

В первом режиме работы (фиг. 2а) на выходе триггера 5 имеют место импульсы со скважностью 2, которые представляют собой инвертированный сигнал по входу S а на выходе 9.— импульсы, обусловленные разностью по времени задних фронтов входных сигналов . (а,б). На выходе O триггера 7 также имеют место импульсы, которые представляют собой инвертированный сигнал по входу S, а на вы- 40 ходе Q — - импульсы, обусловленные разностью по времени передних фронтов импульсов (а, б ), поступающих с формирователей 1 и 2 на инверторы

Зи 4. 65

На выходе элемента 2H-HE 8 присутствует постоянно сирна

Ф так как на его входы поступают нзаимно инвертированные импульсы (н, з) .

На вход элемента 2И-HE 9 поступают сигналы(г, и) с выходов Q триггеров

5 и 7. При этом на выходе элемента

2И-НЕ 9 имеют место импульсы (л)с частотой повторения дна .раза в период. Сигналы с элементов 8 и 9(к, л) поступают на входы триггера б, при этом по входу S имеет место сигнал

"1", по входу R - установочные импульсы с двойной частотой повторения,. на выходе 9 — "0"(м), на выходе Q—

"1" (н ), Во втором режиме работы(фиг. 2 б) когда Е„отстает по фазе. относительно

Е, на выходе элемента 8 имеют место импульсы с двойной частотой(к), на выходе элемента 9 имеет место сигнал

"1" (л) . При этом на выходе Q триггера б присутствует сигнал "1"(м), а на выходе Ц вЂ” "0"(н) .

Таким образом, в зависимости от соотношения фаз входных сигналов выходной триггер 6 устанавливается в одно из двух устойчивых .состояний ("1",.) или ("0"), а установочные импульсы по входам поступают дна раза за период.

Выходы второго R - S триггера б являются выходом устройства. Быстродействие устройстна составляет полпериода подводимых частот.

Использование предлагаемого устройства в качестве реагирукщего элемента в быстродействующих устройстнах релейной защиты и автоматики, позволяет повысить помехоустойчивость устройств, что является важным фактором в работе энергосистем и потребителей электроэнергии.

Формула изобретения

Устройство для сравнения фаз двух электрических величин, содержащее первый и второй формирователи электрических величин, на входы которых подаются сравниваемые величины, а выходы подключены соответственно ко входам S u R первого R-5 триггера, выход Ц которого подключен к одному из входов первого элемента 2И-НЕ, а выход ф подключен к одному из .входов второго элемента 2И-НЕ, а выходы первого и второго элементов 2И-НЕ подключены соотнетственйо ко входам

S и и второго R S триггера, выходы которого являются выходом устройства, о т л и ч а ю щ е е с я тем, что, с целью повышения помехоустойчивости, дополнительно введены третий R-S триггер и два инвертора, причем входы первого и второго иннерторов подключены соответственно к выходам первого и второго формирователей, а

790061

Составитель T. Щеголькова

Редактор H. Лазаренко Техред М. Голинка Корректор E. Папп

Заказ 9048/53 Тираж 783 Подписное

ВНИИПИ Государственного комитета СССР

Ilo делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент", r. Ужгород, ул. Проектная,4 выходы подключены ко входам S u R третьего R-S триггера, выходы Q и Ц которого подключены соответственно к другим входам первого и второго элементов 2И-НЕ.

Источники информации, принятые во внимание при экспертизе

1 ° Авторское свидетельство СССР

9 456337, кл. H 02 H 3/38, 050175.

2. Авторское свидетельство СССР по заявке le 2568186/24-07, кл. H 02 H 3/40, H 01 H 83/18, 09.01.78.

U а