Селектор импульсов

Иллюстрации

Показать всеРеферат

Союз Советских

Соцналнстнческнх

Республик

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ о>790262

/ ф а

1 (б1) Дополнительное к авт. сеид-ву (51)м. К„.з

Н 03 К 5/26 (22) Заявлено 141077 (21) 2532940/18-21 с присоединением заявки ¹ (23) Приоритет

Опубликовано 23,1280 Бюллетень № 47

Дата опубликования описания 30. 12. 80

Государственный комитет

СССР но делам изобретений и открытий (53) УДК 621. 373.. 3 (088. 8) (72) Авторы изобретения

A.È.ÁoãäàHîâ, С.П.Куляшов и В.К.Якимовский (71) Заявитель (54) СЕЛЕКТОР ИМПУЛЬСОВ триггера памяти, выходы которого соединены с первыми входами логических элементов И, вторые входы которых соединены с выходом второго упомянутого формирователя импульсов, выход одного из логических элементов И соединен со входом счетчика посылок, вход сброса которого подключен к выходу второго логического элемента

ИЛИ, один вход котор го соединен с выходом второго логического элемен-. та И f2).

Недостатком данного селектора является недостаточная точность.

Цель изобрете:-:ие — повышение точности селектирования.

Поставленная цель достигается тем, что в селектор импульсов, содержащий управляемый генератор, вход которого соединен с одним входом распределителя, входом первого формирователя импульсов, входной шиной и входом инвертора, выход которого подключен ко входу второго формирователя импульсов и второму входу распределителя, третий вход которого подключен к выходу управляемого генератора, а вход сброса соединен с выходом первого логического элемента ИЛИ, два входа которого соединены с выхоИзобретение относится к импульс ной технике.

Известен селектор импульсов, содержащий вентильное устройство, двоичный счетчик, подсчитывающий число 5 импульсов, прошедших через вентильное устройство, сканирующее устройство, линейное суммирующее устройство, блок памяти, декодирующее устройство 111 . 10

Недостатком данного селектора является его сложность.

Наиболее близким по технической сущности к предлагаемому является селектор импульсов, содержащий упра- 15 вляемый генератор, вход которого соединен с одним входом распределителя, входом формирователя импульсов, входной шиной и входом инвертора, выход которого подклчен ко входу второго 2р

Формирователя импульсов и второму входу распределителя, третий вход которого подключен к выходу управляемого генератора, а вход сброса соединен с выходом первого логическо- 25 го элемента ИЛИ, два входа которого соединены с выходами упомянутых формирователей импульсов, выход распределителя соединен через третий Формирователь с информационным входом Зр и

Д Г

I.

790262 дами упомянутых формирователей импульсов, выход распределителя через третий формирователь импульсов соединен с информационным входом триггера памяти, выходы которого соединены с первыли входами логических,; элементов И, вторые входы которых соединены с выходом второго упомянутого формирователя импульсов, выход одного из логических элементов И соединен со ьходом счетчика посылок, вход сброса которого подключен к вы- iQ ходу второго логического элемента

ИЛИ, один вход которого соединен с выходом второго логического элемента

И, введен дополнительный логический элемент ИЛИ, выход которого соединен со входом сброса триггера памяти, и два дополнительных формирователя импульсов, входы которых соединены с выходами распределителя, а выходы со входами каждого из упомянутых 20 логических элементов ИЛИ, при этом третий вход дополнительного логического элемента ИЛИ соединен с выходом первого формирователя импульсов.

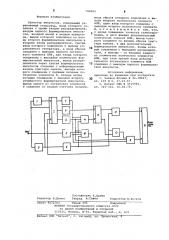

Структурная электрическая схема предлагаемого селектора приведена на чертеже.

Селектор содержит управляемый генератор 1, распределитель импульсов

2, состоящий из двоичного счетчика и дешифратора (не показан), инвертор 30

3, формирователи импульсов 4-6, дополнительные формировател:. им.-.ульсов

7 и 8, s:.îãè÷åñêèå элементы ИЛИ 9 и

10, триггер памяти 11, логические

0 элементы И 11 и 13, дополнительный 35 логический элемент ИЛИ 14, счетчик посылок 15.

Селектируемый сигнал подается на входч, ю шину 16, выходной сигнал снимается с выхода 17.

Принцип работы селектора заключается в следующеM.

С приходом заднего фронта сигнала паузы формирователем 5 вырабатывается короткии импульс, который через элементы ИЛИ 10 и 14 устанавливает в нуль соответственно запоминающий триггер 11, распределитель 2, а также выходным сигналом синхронизируется управляемый генератор импульсов 1 таким образом, чтобы начиналось форми- 50 рование нового периода оклебаний, к тому же подается разрешающий потенциал йа дешифратор распределителя 2 для выделения на его выходах отметок предельных значений длительности посылки. Начинается цикл -селектирования посылки.

В случае посылки длительностью менее минимального предела при ее окончании формирователем 6 вырабатывается .короткий импульс, который устанавливает в нуль двоичный счетчик распре делителя 2 через логический элемент

ИЛИ 10 и счетчик посылок 15 через логические элементы И 13 и ИЛИ 9.

Одновременно синхгонизируется генераб5 тор импульсов.1, и с инвертора 3 подается разрешающий потенциал на дешифратор распределителя 2 для выделения на его выходе отметки предельного значения паузы. Селектор готов к началу цикла селектирования паузы.

В случае посылки в пределах заданной длительности селектирование продолжается до ее окончания. B момент достижения минимума от переднего фронта импульса, выделенного дешифратором распределителя 2, формирователем 4 вырабатывается короткий импульс, который поступает на запоминающий вход триггера 11 и устанавливает его в состояние, при котором с прямого выхода подается потенциал на логический элемент H 12, разрешающий прохождение импульсов. Если посылка закончится в интервале времени между минимумом и максимумом предельных значений, то короткий импульс с формирователя б, образовавшийся от конца посылки, проходит через логический элемент И 12 на счетный вход двоичного счетчика посылок и запоминается. Процесс установки селектора в исходное состояние готовности к селектированию паузы происходит в соответствии с описанным.

В случае посылки длительностью более максимального лредела процесс селектирования продолжается в соответствии с описанным. В момент достижения максимума от переднего фронта импульса, выделенного дешифратором распределителя 2, формирователем 8 вырабатывается короткий импульс, который поступает через логические элементы ИЛИ на установочные входы соответственно запоминающего триггера

11, распределителя 2 и счетчика посылок 15 для сброса их в исходное состояние. Далее цикл селектирования продолжающейся посылки повторяется.

В случае паузы в пределах заданнои длительности ее селектирование начинается в соответствии с описани ем. При окончании паузы процесс начала селектирования посылки соответствует описанному.

В случае паузы длительностью более максимального предела процесс селектирования соответствует описанию до момента достижения максимума. В момент максимума предела паузы от переднего фронта импульса, выделенного дешифратором распределителя 2, формирователем 7 вырабатывается короткий импульс, который поступает через логические элементы ИЛИ на установочные входы соответственно запоминающего триггера, распределителя

2 и счетчика посылок 15 для сброса их в исходное (нулевое) состояние.

Далее цикл селекции продолжающейся паузы повторяется.

790262

Формула изобретения

Составитель A.Àðòþõ

Техред A-Савка Корректор В.Бутяга

Редактор В.Данко

Заказ 07 6

4 Тираж 9 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5 илиал ППП "Патент", r. Ужгород, ул. Проектная, Селектор импульсов, содержащий управляемый генератор, вход которого соединен c oäíèì входом распределителя, входом первого формирователя импульсов, входной шиной и входом инвертора, выход которого подключен ко входу второго формирователя импульсов и второму входу распределителя, третий вход которого подключен к выходу управляемого генератора, а вход сброса соединен с выходом первого логического элемента ИЛИ, два входа которого соединены с выходами упомянутых формирователей импульсов, выход распределителя через третий формирователь импульсов соединен с информационным входом триггера памяти, выходы которого соединены с первыми входами ло- гических элементов И, вторые входы которых соединены с выходом второго упомянутого формирователя импульсов, выход одного из логических элементов

И соединен со входом счетчика посылок, вход сброса которого подключен к выходу второго логического элемента

ИЛИ, один вход которого соединен с выходом второго логического элемента

И, отличающийся тем, что, с целью повышения точности селектирования, в него введен дополнительный логический элемент ИЛИ, выход которого соединен со входом сброса триг гера памяти, и два дополнительных формирователя импульсов, входы которых соединены с выходами распределителя, а выходы — со входами каждого из упомянутых логических элементов

ИЛИ, при этом третий вход дополнительного логического элемента ИЛИ соединен с выходом первого формирователя импульсов.

Источники информации, принятые во внимание при экспертизе

1. Заявка Японии М 42-18667, кл. 110 Д О, 27.03.67.

2. Патент США 9 3515992, кл. 325-322, 16,02.70.