Двухпороговый частотный компоратор

Иллюстрации

Показать всеРеферат

ОПИСАН

ИЗОБРЕТЕН

К АВТОРСКОМУ СВИ Е И

Союз Советскик

Социалистическид

Республик

264 (61) Дополнительное к ввт. саид-в

{22) Заявлено 08,06.78 (23) 262

5/26 с присоединением заявки М—

Государственный комитет

СССР ио делам июбретеиий и открытий (23) Приоритет

Опубликовано 231230. Ьюлл

Дата опубликования описания

21.373 (088.8) (72) Авторы изобретения

A. К. Каганюк, В. М. Славинский, 3. A Черняк, Г. М. Нунупаров, В. И. Силаев, К. Ф. Жданов и H. П. Омельченко

Ордена Октябрьской Революции и ордена Трудового Красного

Знамени Институт горного дела им. A. A. Скочинского и Научно-производственное объединение "йвтоматгормаш" (71) Заявители (54) ДВУХПОРОГОВЫЙ ЧАСТОТНЫЯ КОМПАРАТОР

Изобретение относится к импульсной технике и может быть использовано в приборах для анализа сигналов от источников стати .ески распределенных импульсов и является усовершенствованием известного устройства.

По основному авт.св. Р 450338 известен двухпороговий частотный компаратор, который содержит источник статического сигнала, синхронизатор начала измерения, схему совпадения, задатчик времени единичного измерения, накопитель анализируемых импульсов, два дешифратора, задатчики верхнего и нижнего порогов срабатывания, накопитель синхроимпульсов, блок формирования управляющих импульсов, задатчики.циклов обработки и анализа и исполнительные элементы,,1) ..

Недостатком этого устройства является то, что оно может работать только на стацнонврных объектах или объектах, имеющих определенную постоянную скорость перемещения.

Цель изобретения - расширение функциональных возможностей с сохранением точности при установке на движущемся объекте.

Указанная цель достигается тем, что в устройство, содержащее источник статического сигнала, синхронизатор начала измерения, схемы сов5 падения, накопитель анализируемых импульсов, и накопитель синхроимпульсов, дешифраторы, эадатчики верхнего и нижнего порогов срабатывания, задатчики циклов обработ t0 ки и анализа, блок формирования управляющих импульсов, исполнительные элементы, задатчик времени единичного измерения, при этом синхронизатор начала измерения подключен е5 к накопителю синхроимпульсов и через задатчик времени единичного измерения и схему совпадения к накопителю анализируемых импульсов, а выход накопителя синхроимпуль;ф сов через дешифратор, другие входы которого связаны с задатчиком циклов анализа и задатчиком циклов обработки, соединен с входами блока формирования управляющих импуль25 сов, введены дополнительный дешифратор, датчик скорости объекта и логический элемент, вход. которого соединен с датчиком скорости объекта, а выходы — со входами дополни30 тельного дешифратора выходы которо790264 го подключены ко входам задатчиков циклов анализа и обработки.

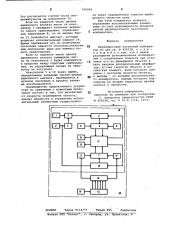

На чертеже изображена схема устройства.

Устройство содержит источник 1 статистического сигнала, синхронизатор 2 начала измерения, элемент 3 5 совпадения, эадатчик 4 времени единичного измерения, накопитель 5 анализируемых импульсов, дешифраторы 6 и 7, задатчики 8 и 9 верхнего и нижнего порогов срабатывания, 3© накопитель 10 синхроимпульсов, блок

11 формирования управляющих импульсов, задатчик 12 циклов обработки, задатчик 13 циклов анализа, исполнительные элементы 14 и 15, дополнительный дешифратор 16, логический блок 17,датчик 18 скорости объекта, двухпороговый частотный компаратор

19, движущийся объект 20.

Синхронизатор 2 начала измерения подключен к накопителю 10 синхроимпульсов и через датчик 4 времени единичного измерения и элемент

3 совпадения к другому выходу которого подключен источник 1 к накопителю 5 анализируемых импульсов, выход которого соединен через дешифратор 6, другие входы которого подключены к задатчику 8 верхнего порога срабатывания и задатчику 9 нижнего порога срабатывания, с блоком 11 30 формирования управляющих импульсов, выходы которого подключены к исполнительным элементам 14 и 15, а обнуляющие выходы — к обнуляющим входам накопителя 5 и накопителя 10, 3$ выход которого соединен через дешифратор 7 с другими входами блока

11 формирования. Вход блока 17 подклю. чен к датчику 18 скорости объекта, а выходы — к входам дешифратора 16, 4п выходы которого соединены с входами дешифратора 7 через задатчик 13 цикла анализа и задатчик 12 циклов обработки.

Ф»

М „= — -

1( обр ч .ЕслИ при заданном числе единичного ан ализа, число . на накопителе 5 не достигает значения, определенного задатчиком 9 нижнего порога.

55 срабатывания, то блок 11 формирования управляющих импульсов выдает импульс на включение исполнительного элемента 15, производящего обработку обнаруженного рассогласования.

Время обработки задается с помощью задатчика 12 числа циклов обработки, определяющего время нахождения испОлнительных элементов 14 и 15 во включенном состоянии.

Устройство работает следующим образом.

Статический сигнал от источника

1 поступает непрерывно на вход элемента 3 совпадения. Синхронизатор

2 в заданные моменты времени выдает единичные импульсы. Каждая из этих импульсов, пройдя задатчик 4, опреде. ляет момент начала и длительность единичного цикла анализа, открывая на заданное время элемент 3 совпадения. В течение такта импульсы от источника 1 поступают на накопитель

5 и запоминаются. В то же время синхроимпульс от синхронизатЬра 2 запоминается в накопителе 10 синхроимпульсов, С датчика 18 скорости объекта управляющий сигнал, пропор- циональный скорости движения объекта 20 поступает на блок 17, который форьырует квантованных уровней сигнала, обратно пропорциональных скорости движения объекта 20.

С блока 17 по управляющему каналу, соответствующему данной скорости движения объекта 20, сигнал поступает на входы дешифратора 16 управляющий сигнал поступает на задатчики

12 и 13. При этом на задатчиках 12 и 13 формируется число единичных циклов анализа и обработки, обратно пропорциональное скорости движения объекта 20, на котором установлен компаратор 19.

Частота управляющих импульсов, выдаваемая синхронизатором 2 постоянна. В результате дополнительно введенных элементов и узлов, при любых изменениях скорости движения объекта 20, расстояние, пройденное им за время анализа и обработки будет поддерживаться постоянным с точностью, определяемой числом N шагОв квантования датчика скорости объекта 18.

Расстоянне анализа и обработки определяется следующими зависимостями бои ЧФ, Ч Const

«ящ 1(, н Х, боер "+ =Ч вЂ” =const

Nos

os е дн- расстояние, пройденное объектом при анализе сигнала; (в— расстояние, пройденное . объектом при обработке сигнала; коэффициент анализа; коэффициент обработки; ч - скорость движения объекта; время анализа;

t - - время обработки; частота импульсов синхронизатора; и ; число единичных циклов анализа;

N - число единичных циклов обраОБР ботки.

790264

Формула изобретения

ВНИИПИ Заказ 9133/77 Тираж 995 Подписное

Филиал ППП "Патент", r. ужгород, ул. Проектная, 4

Это.достиГается счетом числа синхроимпульсов на накопителе 10.

Если на заданное число циклов единичного анализа число на накопителе 5 превышает значение верхнего порога срабатывания, определенное задатчиком 8, то на выходе блока 11 появляется импульс, который включает исполнительный элемент 14 °

Время пребывания его во включенном состоянии задается способом,аналогичным описанному выше для нижнего порога срабатывания.

Если на заданное число циклов единичного анализа суммарное число на накопителе 5 будет находиться в пределах между порогами срабатывания, то управляющий сигнал на обработку не поступает.

Накопители 5 и 10 через время, определяемое заданным числом циклов единичного анализа, переводятся в 20 нулевое состояние и процесс аналища возобновляется.

Преимущество предлагаемого устройства по сравнению с известным прототипом состоит в том, что независимо .от скорости перемещения объекта, анализ обработки и управление исполнительными элементами осуществляется через определенные отрезки пройденного объектом пути.

При этом повышается точность управления исполнительными элементами за счет равномерности процесса работы двухпорогового частотного компаратора.

Двухпороговый частотный компаратор по авт.ñâ. Р 450338, о т л и ч а ю шийся тем, что с целью расширения функциональных возможностей с сохранением точности при установке его на движущемся объекте в него введены дополнительный дешифратор, д.-.тчик скорости объекта и логический элемент, вход которого соединен с датчиком скорости объекта, а выходы — co входами дополнительного дешифратора, выходы которого подключены ко входам задатчиков цикЛов анализа и обработки.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

9 450338, кл. Н 03 К 5/18, 1973.