Преобразователь напряжения в код

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистических

Республик

<щ790291

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. саид-ву (22) Заявлено 260279 (21) 2729222/18-21 с присоединением заявки ¹ (23) Приоритет

Опубликовано 231280 Бюллетень ¹ 47

Дата опубликования описания 231280 (51)М. Кл.

Н 03 К 13/17

Государствеииый комитет

С С С Р ио делам изобретений и открытий (53) УДК 681, 328 (088. 8) (72) Автор изобретения

П.М.Ананичев (71) Заявитель (54 ) ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ В КОД

Изобретение относится к вычислительной технике и может использоваться в информационно-измерительных.системах различного назначения.

Известен преобразователь напряжения в код, содержащий источник эталонных уровней, линейку компаратора и деши*ратор, блок управления (1).

Недостатком устройства является низкая точность. 10

Известен преобразователь напряжения в код, содержащий вычитающее устройство, выход которого через ключи соединен с источником опорного и преобразуемого напряжения, а выход 35 подключен к компаратору, выход которого соединен с регистром приема кода и. управляющим входом первого ключах а выход вычитающего устройства подключен через третий ключ ко входу 20 первого конденсатора запоминающего устройства, выход которого через четвертый ключ соединен со входом второго конденсатора запоминаюцего устройства и выходом второго ключа 25 выход второго конденсатора запоминающего устройства подключен к одному из входов вычитающего устройства (2)

Недостатками устройства являются низкие быстродействие и точность. 30

Цель изобретения — повышение быстродействия и точности.

Указанная цель достигается тем, что в устройство, содержащее источник эталонного напряжения, вычитающее устройство, компаратор, два элемента запоминания, разделительный ключ, выходной ключ, ключ обратной связи, масштабирую ий усилитель, блок управления, введены разрядные ключи, устройство выделения старшей единицы, шифратор, делитель эталонного напряжения, дополнительные компараторы и дополнительные вычитающие устройства, причем первые входы дополнительных вычитаюцих устройств и вычитающего устройства соединены с выходами делителя эталонного напряжения, вторые входы соединены с выходом ключа обратной связи и выходом входного ключа, выходы дополнительных вычитающих устройств соединены с первыми входами дополнительных компараторов, вторые входы которых соединены с общей шиной, выходы компаратора и дополнительных компараторов соединены со входами блока выделения старшей единицы, выходы которого соединены со входами шифратора и соответствующими первыми входами разрядных ключей, вторые

790291 входы которых соединены с выходами вычитающего устройства и дополнительных вычитающих устройств, выходы раз— рядных ключей соединены со входом пер-. вого элемента запоминания и первым входом разделительного ключа, второй вход которого соединен с первым выходом блока управления, выход разделительс рого ключа соединен со входом второго элемента запоминания и входом масштабирующего усилителя, выход которого сое- о динен с первым входом ключа обратной связи, второй вход которого соединен со вторым выходом блока управления, третий выход которого соединен с входом входного ключа.

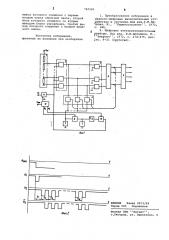

На фи". 1 приведена структурная электрическая схема устройства; на фиг. 2 — временные диаграммы работы устройства.

Преобразователь напряжения в код состоит из делителя 1 эталонного напряжения, вычитающих устройств 2, компаратора 3, блока 4 выделения старшей единицы, шифратора 5, разрядных ключей б, элементов 7 запоминания, разделительного ключа 8, масштабирую- 25 щего усилителя 9, ключа 10 обратной связи, входного ключа 11, блока 12 управления.

Преобразуемое напряжение Д подключено ко входу входного ключа 11, эталонное напряжение ц у- — ко входу делителя 1, запускающий сигнал U>«„ соединен со входом блока 12. При подаче сигнала Upc. блок 12 выдает сигнал U g открывающий входной ключ 11, и преобразуемое напряжение Uy поступает на одни входы вычитающих устройств 2., с выходов которых напряжения, равные разности меяду опорными и входными напряжениями, поступают на одни входы компараторов 3, ходы которых подсоединены ко входам .блока 4, С выхода шифратора 5 по сигналу ()л по "тупают старшие разряды выходногО кода преобразуемого напряжения. Напряяение, равное разности между преобразуемым и ближайшим нижним опорным напряжением, через один из разрядных ключей б, который открыт сигналом .с выхода блока 4, поступает на первый элемент 7, т.е. запоминается текущее значение разностного напряжения. За время действия импульсов (пауза меяду тактовыми импульсами) текущее значение разности через открытый разделительный ключ Э запоминае ся вторым элементом 7, который служит для запоминания предыдущего значения разности. С выхода второго элемента 7 .напряжение, усиленное масштабирующим усилителем 9 в К-раз (где К равно основанию системы счисле-60 ния, в который представлен выходной код), поступает на вход ключа 10, который открывается сигналом Uj, и

Напряжение с его выхода под ется на одни входы вычитающих устройств 2, 5$

Т. < начинается второй цикл преобразования. С каждым импульсом обобщенного сигнала Uz на выходе шифратора

5 появляется выходной код, соответстввующий следующим (более младшим) разрядам преобразуемого напряжения.

Количество импульсов в сигнале Д» блока 12 равно N-I где N — количество разрядов (или групп разрядов) в выходном. коде, равное количеству тактов за одно преобразование. Количество вы.читающих устройств 12 равно в общем и случае 2, где << — количество разрядов выходного кода (если преобразование производится в двоичный код), получаемых за один такт преобразования, масштабирующий усилитель 9 имеет коэффициент усиления К=2 при использовании пассивных вычитающих устройств при использовании вместо вычитающих устройств суммирующих усилителей мас-, Ытабирующий усилитель не нужен.

Оормула изобретения

Преобразователь напряжения в код, содержащий вычитающее устройство, выход которого соединен с первым входом компаратора, второй вход которого соединен с общей шиной, два элемента запоминания, разделительный ключ, ключи управления, входной ключ, ключ обратной связи, масштабирующий усилитель, блок управления, о т л и ч аю шийся тем, что, с целью повышения быстродействия и точности, в него введены разрядные ключи, блок выделения старшей единицы, шифратор, делитель эталонного напряжения, дополнительные компараторы и дополнительные вычитающие устройства, причем первые входы дополнительных вычитающих устройств и вычитающего устройства соединены с выходами делителя эталонного напряжения, вторые входы соединены с выходом ключа обратной связи и выходом входного ключа, выходЫ дополнительных вычитающих устройств соединены с первыми входами дополнительных компараторов, вторые входы которых соединены с общей шиной, выходы компаратора и дополнительных компараторов соединены со входом блока выделения старшей единицы, выходы которого соединены со входами шифратора и соответствующими первыми входами разрядных ключей, вторые входы которых соединены с выходами вычитающего устройтсва и дополнительных вычитающих устройств, выходы разделительных ключеи соединены с входом первого элемента запоминания и первым входом разделительного ключа, второй вход которого соединен с первым выходом блока управления, выход разделительного ключа соединен со входом второго элемента запоминания и входом масштабирующего усилителя

790291 иг выход которого соединен с первым входом ключа обратной связи, второй вход которого соединен со вторым выходом блока управления, третий вы;ход которого соединен с входом входного ключа.

Источники информации, принятые во внимание при экспертизе

1. Преобразование информации в аналого-цифровых вычислительных устройствах и системах.Под ред.Г.М.Петрова, И., машиностроение, 1973, с. 100.

2. Цифровые электроиэмерительные приборы. Под ред. В.М.Шляндина, И., Энергия, 1972, с. 274-275, рис. ис. 6-21 (прототип) .

ВНИИПИ Заказ 9073/65

Тираж 995 Подписное.

Филиал ППП Патент, г.ужгород, ул, Проектная, 4