Логарифмический аналого-цифровой преобразователь

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советсиик

Социалистических

Республик (н1790294 (61) Дополнительное к авт. саид-ву (22) Заявлено 220279 (21) 2728556/18-21 с присоединением заявки ¹ (23) Приоритет

Опубликовано 2 31 28 0. Бюллетень ¹ 4 7

Дата опубликования описания 231280 (51)М. Кл.

Н 03 К 13/20

Государственный комитет

СССР по делам изобретений и открытий (53) УДК 681 ° 325 (088.8) (72) Авторы изобретения

В.Е.Ямный, Ю.И.Белоносов и В.Н,Чуясов

Ц, i

Белорусский ордена Трудового Красного Знамейи государственный университет им. В..И.Ленина (71) Заявитель (54) ЛОГАРИФМИЧЕСКИЙ АНАЛОГΠ— ЦИФРОВОИ

ПРЕОБРАЗОВАТЕЛЬ

Изобретение относится к информационно-измерительной технике и может быть использовано в преобразователях напряжения в код.с логарифмической функцией преобразования. 5

Известен преобразователь, содержащий блок управления два канала последовательно соединенных усилителей входы которых соединены с источником преобразуемых напряжений, и аналого- 1О вых запоминающих устройств, выходы последних через компараторы подключены к триггерам памяти разрядов., выходы которых подключены к сдвиговым регистрам, объем которых уменьшается 15 на единицу с уменьшением веса разря,да, выходы последних разрядов сдвиговых регистров подсоединены к буферно-му регистру 13.

Недостатком данного устройства яв- 20 ляется малый динамический диапазон и невозможность получения логарифмического преобразования.

Цель изобретения — расширение функциональных воэможностей, а также по- 25 вышение надежности устройства.

Поставленная цель достигается тем, Что в логарифмический аналого-цифровой преобразователь, содержащий блок управления два канала из П последова- jp тельно соединенных усилителей и и аналоговых запоминающих устройств, входы первых усилителей объединены и соединены с выходом источника преобразуемого напряжения, выходы каждого иэ и аналоговых запоминающих блоков подключены через компаратор ко входам триггеров памяти разрядов, соединенных с соответствующими входами и сдвиговых регистров каждого канала, введены дополнительный компаратор, триггер, сдвиговый регистр, 2 (и -1) элементов И, (и -1) элементов ИЛИ, причем выходы триггеров памяти разрядов подключены к управляющему входу соответствующих усилителей, выход первого аналогового запоминающего блока второго канала подключен к дополнительному компаратору, выход которого через триггер памяти подключен к разрядному дополнительному сдвиговому регистру, выход которого соединен с выходной клеммой старшего разряда н с первым входом (h -11 элементов И первой группы, а через инвертор с первым входом (tl -1) элементов И второй группы, вторые входы (П -1) элементов И первой группы подключены к соответствующим выходам (и -1) сдвиговых регистров первого канала, вто790294 рые входы (П -1) элементов И второй группы подключены к соответствующим выходам 11 сдвигоных регистров второго канала, выходы элементов И одного разряда подключены ко входам (и-1) элементов ИЛИ, выходы которых соединены с выходными клеммами преобразователя.

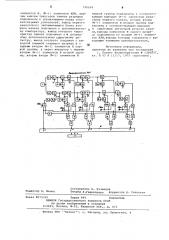

На чертеже схематически изображено предлагаемое ус тройство.

Преобра зова тель содержит источник

1 преобра зуемого напряжения, буферный усилитель 2 с коз ффициен том передачи "1", усилители 2 -2 с переключаемыми коэффициентами передачи первого канала, аналоговые 15 запоминающие устройства (АЗУ) 3 — 3 .h первого канала, компараторы 4 — 4 м первого канала, триггеры 5 — 5п разрядов первого канала, буферный усилитель б„с коэффициентом передачи }0 усилители бо — б„ с переключаемыми коэффициентами передачи второго канала, АЗУ 7 — 7n второго канала, компараторы 8 — 8п второго; канала, триггеры 9„ — 9> разрядов вто- р5 рого канала, дополнительный компаратор 8п и триггер 9о второго канала, сдвиговые регистры 10 — 10п первого канала, сдниговые регистры 11 . — 11 второго канала, разрядные дополнитель-, ные сдвигоные регистры 11д — 11„,,ин.вертор 12,элемент И 13 первого канала/ элементы И 14 второго канала, элемент ИЛИ 15, выходные клеммы 16 преобразователя, блок 17 управления.

Коэффициенты передачи .усилителей

2 и бп равны О«2, 2 и б — Р"/

2 и 6 — О1/2 3

Опорные напряжения компараторов

4 и 8 уанны U z< /D"« 2, 4 и 8

u»/r«2,4 и 8 — u „/Z«, 40

8 — Urnoly /

Логарифмический АЦП работает сле,дующим образом.

В исходном состоянии все усилители, кроме б,имеют коэффициент передачи, равный 1 °

При наличии сигнала 0 ) по команде от блока 17(а) управления в аналоговые запоминающие устройства 3 . и

7 записывается сигнал, равный 50

Uex (Co) и 1(ex (t } D соответственно, . Если U (t )@ превышает порог компаратора 8о, то в триггер 9о по команде от блока 17 управления (с/ записывается 1 . Если Ugy (to) превышает порог компаратора 8«то в триггер 9 по команде от блока 17 управления записывается 1 . Таким образом, на первом такте с помощью трех компараторов весь диапазон преобразуемых напряжений разбивается на ф)

4 участка, динамический диапазон я 2 которых ранен D 2 . Запись в триггерах 5, 9 о, 9 осуществляется в момент времени t+ht, где 6t - время переходного процесса в компараторе ° И

Если в триггерах 5» или 9 записывается "1", то коэффициент передачи усилителей 21 и 62 устанавливается равным О1/Я

Следующим импульсом от блока управления (В) в АЗУ 3 и 7п записывается напряжение преобразуемого сигнала, которое располагается н диапазоне от U „ o U » Р« . Одновременно с этим в сдвиговые регистры 10, ) 1

11,, записывается информация с триггеров 5, 9О, 9

Следующим импульсом от блока уйравления 17 (aj записывается новая выборка н АЗУ 3 и 7 и компараторы 5,,8,,8о квантуют новую выборку описанным способом.Одновременно с этим компараторы

5< и 9 кнантуют предыдущую выборку более точно. Далее процесс повторяется. Таким образом, на каждом этапе измеряется один разряд двоичного числа эквивалентного аналоговой выборке.„

Время преобразования равно

=С +С <Ъ +С пр Аъ комп. тр, цщ, Так как пороги компараторов установлены в соответствии с логарифмической шкалой, то код на разрядных триггерах соответствует логарифмической шкале.

Так как объем сдвиговых регистров уменьшается на 1 в сторону младших разрядов, то на схеме И 13 — 14 информация о коде одной выборки поступает одновременно. Код с выхода регистра 11 управляет с помощью схем

И 13 — 14 и схемы ИЛИ 15 передачу кода или с канала 1 или с канала 2 в зависимости от 0 ) 0пщДЪ или

}З у < }щр /4Ъ, т. е. выход 11 находится в 1 или 0 .

Такое построение АЦП позволяет получить высокое быстродействие, широкий динамический диапазон, логарифмический закон преобразования.

Формула изобретения логарифмический аналого-цифровой преобразователь, содержащий блок управления, два канала из г .последовательно соединенных усилителей и аналоговых запоминающих блоков, входы первых усилителей объединены и соединены с выходом источника преобразуемого напряжения, выходы каждого из П аналоговых запоминающих блоков подключены через компаратор ко входам триггеров памяти разрядов, выходы которых соединены с соответствующими входами и сдвиговых регистров каждого канала, отличающийс я тем, что, с целью расширения функциональных возможностей, повышения быстродействия и надежности, в него введены дополнительный компаратор, триггер, сдвиговый регистр, 2(-1) 790294

Ямафифиичианий Юд

Составитель A Кузнецов

Техред,Е.Гаврилешко Корректор В ° Синицкая

Редактор О. Малец

Заказ 9073/65 Тираж 995 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4 элементов И, (П -1) элементов ИЛИ, причем выходы триггеров памяти разрядов подключены к управляющему входу соответствующих,усилителей, выход первого аналогового запоминающего блока второго канала подключен к дополнительному компаратору, выход которого через

5 триггер памяти подключен к Ю разрядному дополнительному сдвиговому регистру, выход которого соединен с выходной клеммой старшего разряда и с первым входом (И-1) элементов И пер10 вой группы, а через инвертор с первым входом (5-1) элементов И второй группы, вторые входы (h-1) элементов И первой группы подключены к соответствующим выходам (и-1) сдвиговых регистров первого канала, вторые входы (П вЂ” 1) элементов И второй группы подключены к соответств ующим выходам сдвиговых регистров второго канала, выходы элементов И одного разряда подключены ко входам (П вЂ” 1) элементов ИЛИ, выходы которых соединены с выходными клеммами преобра зователя, Источники инФормации, принятые во внимание при экспертиэе

1. Патент Великобритании У 1290057, кл. Н 03 К 13/17, 1975 (прототип).