Логический вентиль на мдп-транзисторах с динамической нагрузкой

Иллюстрации

Показать всеРеферат

ОП ИСАЙИ Е

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистических

Республик п1179О334

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (Ü1) Дополнительное к авт. сеид-ву (22) Заявлено 10 ° 07 ° 78 (21) 2657195/18-21 с присоединением заявки ¹ (23) Приоритет.

Опубликовано 23,1280, Бюллетень ¹ 47

Дата опубликования описания 23. 12. 80

Н 03 К 19/08

Государственный комитет

СССР по делам изобретений и открытий (53) V+K 621.374

1088. 8) (72) Авторы изобретения

E. И. Андреев и Г. Н. Жукова Государственное союзное конструкторско-технологическое бюро по проектированию счетных машин и Опытный завод (71) Заявители (541 ЛОГИЧЕСКИЙ ВЕНТИЛЬ НА МДП ТРАНЗИСТОРАХ с динАмическОЙ нАГРузкОЙ

Изобретение относится к вычислительной технике и может быть использовано в МДП БИС для микропроцессоров.

Известен логический вентиль с динамической иагрузкой, в котором между затвором и истоком нагрузочного транэистора включается предварительно заряженный конденсатор положительной обратной связи (1j.

Недостатком известного устройства является уменьшение выходного напряжения, обусловленное разрядом

Конденсатора обратной связи, и большая потребляемая мощность, обусловленная протеканием тока через нагруэочный транзистор при отпирании управляющих транзисторов вентиля.

Известен логический вентиль на МДП транзисторах с динамической нагрузкой, содержащий тактируемый нагрузочный транзистор, включенный между шиной питания и выходной шиной, и управляющую часть, включенную ме:хду выходной шиной и общей шиной (2J .

Недостатком известного вентиля является низкая помехоустойчивость.

Он характефизуетсй низкой устойчивостью к емкостным помехам .и критичностью к токам утечек легированных полупроводниковых областей выходного узла.

5 Цель изобретения — повышение помехоустойчивости.

Для достижения укаэанной цели в логический вентиль на МДП транзисторах с динамической нагрузкой, 1О содержащей тактируемый нагрузочный транзистор, включенный между шиной питания и выходной шиной„ затвор которого подключен к шине тактового сигнала,и управляющую часть, 1 .включенную между выходной шиной и общей шиной, введен динамический элемент, состоящий из дополнительного нагрузочного транзистора, включенного параллельно тактируемому

2О нагруэочному транзистору, управляющего транзистора, включенного между затвором дополнительного нагрузочного транзистора и выходной шиной, затвор которого подключен

25 к шине питания, и конденсатора смещения уровня тактового сигнала, включенного между затвором дополнчтельного нагрузочного транзистора и шиной инверсного тактового

>Q си гнала.

790334

20

40 б5

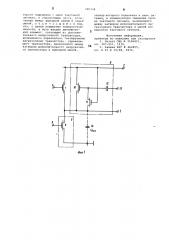

На Фиг. 1 представлена электрическая принципиальная схема устройства; на фиг. 2 — временные диаграммы напряжения входных и выходных сигналов; на фиг. 3 — вольтамперная характеристика Предлагаемого устройства.

На схеме устройства тактируемый нагрузочный транзистор 1 включен между шиной питания 2 и выходной шиной 3, его затвор подключен к шине тактового сигнала 4.управляющая часть 5, которая может состоять иэ группы транзисторов, выполняющих определенную логическую функцию, представлена в частном случае одним транзистором б, включенным между выходной шиной 3 и общей шиной 7, затвор транзистора б подключен ко входной шине 8. Динамический элемент

9 состоит иэ дополнительного нагрузочного транзистора 10, включенного параллельно транзистору 1, управляющего транзистора 11, включенного между затвором транзистора 10 и выходной шиной 3, затвор которого подключен к шине 2, и конденсатора смещения уровня тактового сигнала 12 включенного между затвором транзистора 10 и шиной инверсного тактового сигнала 13. Значение емкости конденсатора 14, включенного между выходной шиной 3 и общей шиной 7, соответствует значению емкости выходного узла.

Логический вентиль на МДП транзисторах с динамической нагрузкой работает следующим образом.

Тактовый сигнал на шине 4 с амплитудой U большей, чем постоянное напряжение Е на шине питания 2 по крайней мере на величину U (напряженче отпирания транзисторов), периодически поступает на затвор тактируемого нагрузочного транЗистора

1„ обеспечивая безусловный заряд конденсатора 14 до напряжения равного Е. В этот момент временной интервал (1„на фиг. 2) напряжение инверсного тактового сигнала на шине 13 равно нулю. Одновременно с предзарядом конденсатора 14 происходит заряд конденсатора 12 дс> напряжения E- L! через открытый транзистор 11, управляющий проводимос.тью дополнительного нагрузочного транзистора 10. Как и во всех ус ройствах "без отношения", во вразумя такта предварительного заряда („) транзисторы управляющей части

5 закрыты. Таким образом, транзистор б заперт и выходная шина 3 не имеет гальванической связи с общей шиной

7.

В конце такта предварительного заряда 1,, после того. как конденсатор 12 эарядится, транзистор 11 запирается напряжением по истоку.

Во время такта считывания (kz) на фиг

2 > тактовые сигналы на шинах 4 и 13 соответственно, становятся равными нулю и U, на затворе дополнительного нагруэочного транзистора 10 устанавливается напряжение Е-U + U т

Тактируемый нагрузочный транизсто

1 в этот временной интервал всегда заперт по затвору, а проводимость дополнительного нагрузочного тран"зистора 10 зависит от комбинации входных логических сигналов управляющей части вентиля 5. Если во время интервала 1 транзистор б заперт, на выходной шине 3 сохраняется высокий потенциал (по абсолютной величине ), при этом допол- . нительный нагруэочный транзистор

10 открыт и гальваническая связь выходной шины 3 с шиной питания 2 нейтрализует влияние емкостных помех и токов утечки.

В следующий такт предзаряда напряжение на выходной шине 3 не изменится, а напряжение на затворе транзистора 10 меняется скачком от

Е 1/т +U до Š— UT.

Если в следующий временной интервал 1 напряжение на шине 8 и, следовательно, на затворе транзистора б становится равным U4,, в первый момент времени дополнительный нагрузочный транзистор 10 открыт и имеет место протекание тока от шины 2 через транзистор 3, при этом напряжение на выходной шине

3 уменьшается. Как только разность напряжений Š— UI>,< > становится равной напряжению отйирания От управляющего транзистора 11, происходит разряд конденсатора 12 через этот транзистор и транзистор б. Дополнительный нагрузочный транзистор 10 запирается, а напряжение на выходной шине 3 устанавливается равным нулю.

Процессы, протекающие в устройстве в тактовые временные интервалы и ", идентичны описанным выше процессам в интервалы .(и ь .

Таким образом, предлагаемый логический вентиль обладает преимуществом потенциальных схем (высокой помехоустойчивостью, малой критичностью к токам утечек ) и в то же время сохраняет все положительные свойства динамических схем "беэ отношения", возможность последовательного включения относительно большого количества управляющих транзисторов и малую потребляемую мощность.

Формула изобретения

Логический вентиль на МДП транзисторах с динамической нагрузкой, содержащий тактируемый нагрузочный транзистор, включенный между шиной питания и выходной шиной, затвор ко790334

10 торого подключен " шине тактового

"и гнала, и управляющую ч =ть,. вклю- енную между выходной шиной и оо,ей шиной, о т л и т а ю шийся тем, что,. с целью повышения помехоустойчивости, в него введен динамический элемент, состоящий и= .дополнительного нагрузочного транзистора, включенного параллельно тактируемому нагрузочному транзистору, управляющегс транзистора, включенного между затвором дополнительного нагрузочного транзистора и выходной шиной, затвор которого подключен к шине питания, и конденсатора смещения уровня тактового сигнала, включенного между затвором дополнительного нагрузочного транзистора H шиной инверсного тактового сигнала.

Источники информации,. принятые во внимание пои экспертизе

1. Патент CBIA 9 3506851, кл. 307-251, 1970.

2. Заявка ФРГ У 462855, кл. Н 03 К 19/08, 1974.

79О334

Составитель Л. Петрова

Техред Т.Маточка

КорректорО. Ковинская

Редактор A. Маковская

Заказ 9075/б7 Тираж 995

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Подписное

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4