Синхронный счетчик

Иллюстрации

Показать всеРеферат

Союз 4:оветскик

Социалистическими

Республик

ОП ИКАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву— (22) Заявлено 02.11. 78 (21) 2681019/18-21 (51)М с присоединением заявки №(23) ПриоритетН 03 К 23/02

Государственный комитет

СССР по делам изобретений и открытий

Опубликовано 231280 Бюллетень ¹47

Дата опубликования описания 23.1280

<5З) УДК 821 374..32(088.8) (72) Автор изобретения

В. И, Горячев (71) Заявитель (54 ) СИНХРОННЫЙ СЧЕТЧИК

Изобретение относится к вычислительной технике, в частности к проектированию синхронных счетчиков.

Известен синхронный счетчик, содержащий и разрядов, каждый из которых состоит из асинхронного счетного триггера, выполненного на логических элементах, и вентиля (1).

Недостатком такого счетчика является сравнительно большое число вентилей, необходимых для организации межразрядных связей и невысокая степень синхронности (одновременности) срабатывания разрядов счетчика, каждый из которых является асинхронным счетным триггером (триггер с одним информационным входом) .

Целью изобретения является повышение степени синхронности работы

"четчика.

Поставленная цель достигается тем, что в синхронный счетчик, содержащий и разрядов, каждый из которых состоит из асинхронного счетного триггера, выполненного на логических элементах, и вентиля, введен элемент ИЛИ-НЕ, первый вход которого соединен с входной шиной, а вы- ход с тактовым входом асинхронного счетного триггера каждого разряда, единичный выход которого подключен к первому входу вентиля последующего разряда, второй вход которого соединен с выходом вентиля предыдущего разряда и со входом асинхронного счетного триггера предыдущего разряда, а выход — c другим входом элемента ИЛИ-HE.

Выход единичного плеча i-го счетного триггера счетчика подключен к первому входу, вентиля 2И (i+1) -го счетного триггера, второй вход которого подключен к входу i-го счетного триггера и к выходу его венти15 яя 2И, при этом выход каждого венгиля 2И подключен к входу элемента

ИЛИ-НЕ, выход которого подключен к тактовым входам всех вспомогательных триггеров.

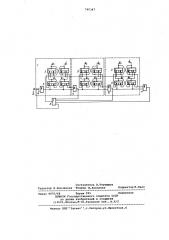

20 Схема предлагаемого синхронного счетчика приведена на чертеже. Синхронный счетчик содержит асинхронный счетный триггер 1, выполненный на двух тактируемых триггерах — основном 2 и вспомогательном 3, вентили (элемент 2И) 4 и элемент ИЛИ-НЕ 5.

Вход синхронного счетчика через элемент 2И 4 подключен к входу первого асйнхронного счетного триггера

30 1 и к входу элемента ИЛИ-НЕ 5, а

790347

4.э

H выход единичного плеча счетного триггера каждого разряда подключен к первому входу элемента 2И 4, последующего разряда второй вход которого подключен к входу асинхронного счетного триггера 1 предыдущего разряда, а выход элемента 2И 4 каждого разряда подключен к входу элемент ИЛИ-НЕ 5, выход которого подключен к тактовым входам всех вспомогательных триггеров 3 синхронного счетчика.

Устройство работает по следующей технологической схеме.

В исходном состоянии на входе синхронного счетчика сигнал отсутствует (С O) . В этом случае на выходе элемента ИЛИ-НЕ 5 действует уровень логической 1 и тем самым разрешается передача кода из всех основных триггеров 2 но вспомогательные триггеры 3. При поступлении сигнала на вход синхронного счетчика (С=1) на выходе элемента ИЛИ-НЕ 5 сформируется уровень логической 1, блокирующий прием информации во вспомогательные триггеры 3 всех разрядон счетчика.

Если до прихода первого сигнала все разряды счетчика находятся в нулевом состоянии (Q =() =Q =o) то на выходах всех элементов 2И-4 действует уровень логического 0, и, н результате с поступлением первого импульса только триггер 2 первого разряда счетчика установится в

C единичное состояние (Q =1) . По окончании первого импульса (C=O) на выходе элемента ИЛИ-НЕ 5 сформируется уровень логический 1 и вспомогательный триггер 3 первого разряда, примет состояние основного т.е. íà его выходе тоже сформируется уровень логической 1 (QÄ =1) . При поступлении второго импульса сформируется сигнал переноса на выходе элемента 2И 4 второго разряда и его основной триггер 2 установится в единичное состояние Я =1),а основной триггер первого разряда -сбросится в нулевое состояние (Q =1) .

Теперь на выходе элемента ИЛИ-НЕ

5 уровень логического О формируется под действием входного сигнаЛа и сигнала c,âûõoäà элемента 2И 4 второго разряда. По окончании входного сигнала на выходе элемента

ИЛИ-НЕ 5 сформируется уровень логической "1" и в счетчике зафиксируется код 01 (Qq 0, Qg=l) .Когда в, ( счетчике устанавливается код 111 (Q=

=Q<=Q =l),то во время действий входО. ного сигнала по мере его прохождения через цепочку из элементов 2И4, на входах элемента ИЛИ-HE 5 всегда присутствует уровень логической 1, и следовательно, на выходе элемента ИЛИ-НЕ 5 действует уровень логического "О . По окончании входного сигнала на всех элементах 2И 4 устанавливаются уровни логическо-! !

ro О, а на его выходе уровень логической И, и, следовательно, в счетчике устанавливается код 000 (Q Q =Q =О),. Таким образом, схема предложенного счетчика выполнена с одним двухвходоным элементом 2И на разряд, против двух вентилей 2И в известной схеме.Следовательно, схема реализуется с меньшими затратами в числе вентилей,т.е. она является более простой по схемотехнической реализации. Меньшее число вентилей является причиной и меньщей мощности потребляемой счетчиком как в статике, так и в динамике.

Наличие дополнительного элемента

ИЛИ-НЕ практически не приводит к заметному увеличению мощностных, затрат, но способствует более высокой степени синхронности (одновременности) срабатывания всех разрядов счетчика. Последнее объясняется тем, что в известной схеме на одновременность срабатывания всех разрядов счетчика влияют как разброс в задержках элементов, образующих нспомогательные триггеры всех разрядов, так и разброс в задержках элементов 2И, включенных на входах триггеров счетчика.

В предложенной схеме степень одновременности срабатынания всех разрядов определяется только лишь разбросы н задержках элементов, образующих вспомогательные триггеры.

Формула изобретения

Синхронный счетчик, содержащий и разрядов, каждый из которых состоит из асинхронного счетного триггера, выполненного на логических элементах, и вентиля, отличающийся тем, что, с целью повышения степени синхронности его работы, в него введен элемент ИЛИ-НЕ, первый вход которого соединен с входной шиной, а выход — с тактовым входбм асинхронного счетного триггера каждого разряда, единичный выход которого подключен к первому входу вентиля последующего разряда, второй нход которого соединен с выходом вентиля предыдущего разряда и со входом асинхронного четного триггера предыдущего разряда, а выход — с другим выходом элемента ИЛИ-HE.

Источники информации принятые во внимание при экспертизе

1. Букреев И.Н. и др. Микроэлектронные схемы цифровых устройств,И.! Советское! радио,1975, с. 256, рис.5.80(в) °

790347 г

Составитель В.Чернышов

Редактор Н.Кончицкая Техред Н,Ковалева Корректор Е.Папп

Заказ 9076/68 Тираж 995 Подписное

ВНИИПИ ГосударствЕнного комитета СССР по делам изобретений и открытий

113035,Москва,Ж-35,Раушская наб.,д.4/5

Филиал ППП Патент,,r.Óærîðîä,óë.Ïðîåêòíàÿ,4