Контролируемое арифметическое устройство

Иллюстрации

Показать всеРеферат

О П И С А В.-М Е»

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистических

Республик

<11792250 с

К АВТОРСКОМУ СВИ ИТЮЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 2Ы278 (23) 2700956/18-24 с присоединением заявки Мо (23) Приоритет

Опубликовано 301280. Бюллетень ЙЯ 48

Дата опубликования описания 301280 (51) М. Кл.з

G F 11/00

Государственный комитет

СССР по делам изобретениЯ и открытий (53) УДК 681 3 (088.8) (72) Авторы изобретения

В. В. Гроль, A. N. Романкевич и О. Д. Руккас (71) Заявитель

Киевский научно-исследовательский и конструкторский институт периферийного оборудования (54) КОНТРОЛИРУЕМОЕ АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО

Изобретение относится к области вычислительной техники и может быть использовано при контроле арифметических устройств.

Известны устройства (1),(2), осуществляющие контроль арифметических устройств., основанные на принципах контроля четности и контроля остатков.

Недостаток таких устройств состоит в ограниченной полноте контроля.

Наиболее.близким по технической сущности к предлагаемому является контролируемое арифметическое устройство f3) принятое за прототип, 15 содержащее первый и второй регистры операндов, входы которых подключены к соответствующим информационным входам устройства, а выходы — к соответствующим входам сумматора, выхо-20 дом соединенного с регистром результата и первым информационным входом блока сравнения кодов. .Недостаток этого устройства заключается в малой достоверности контро- 25 ля.

Цель изобретения — повышение достоверности контроля устройства.

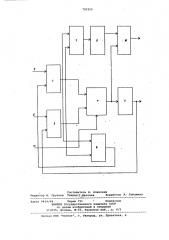

Указанная цель достигается тем, что устройство содержит блок показ- 3Q рядного логического сложения операндов, блок элементов ИЛИ и блок элементов И-НЕ, входы которого соединены с соответствующими входами блока элементов ИЛИ и, с соответствукщими входами сумматора, а выход — со вторым информационным входом первого регистра операндов, выход регистра результата подключен ко второму информационному входу второго регистра операндов, выход блока элементов ИЛИ через блок поразрядного логического сложения операндов — ко второму информационйому входу блока сравнения кодов., Структурная схема арифметического устройства с контролем приведена на чертеже.

Она содержит первый 1 и второй 2 регистры операндов, регистр 3 результата, сумматор 4, шины 5 и б операндов, блок 7 элементов ИЛИ, блок 8 элементов И-НЕ, блок 9 поразрядного логического сложения операндов, блок

10 сравнения кодов, шину 11 управле- ния. Цепи синхронизации и тактировки на схеме усЛовно не показаны.

Принцип работы устройства заключается в том, что при правильном функционировании сумматора пораэряд792250 ная логическая сумма входных операндов должна быть равна разности их арифметической суммы и кода поразрядного логического произведения этих же операндов. Отсюда следует, что каждый рабочий цикл пограммирования двух операндов происходит за два такта.

С л о ж е н и е. Операнды по шинам 5 и 6 записываются в регистры

1 и 2. На выходе блока 7 формируется поразрядная логическая сумма входных кодов, которая записывается в блок 9. На выходе блока 8 формируется инверсия поразрядного логического произведения операндов, но в регистр 1 она не записывается. С выхода сумматора 4 сумма операндов заносится в регистр 3. После занесения информации в регистр 3 и блок

9 осуществляется второй такт рабо.чего цикла.

В ы ч и т а н и е. В -этом такте в регистр 1 заносится инверсия поразрядного логического произведения операндов. Для этого данный регистр может быть выполнен на триггерах с внутренней задержкой. В этом же такте происходит перепись информации из регистра 3 в регистр 2, а по шине 11 в младший разряд сумматора 4 подается инверсное значение состояния, в котором находилась шина 11 на такте

"Сложение". Иными словами, на такте

"Вычитание" происходит сложение прямого кода суммы двух операндов с дополнительным кодом поразрядного логического произведения этих же операндов, а после установления на выходе сумматора 4 нового значения — сравнение на схеме 10 этого кода с кодом поразрядной логической суммы, запи(санньа4 ранее в блоке 9. Равенство этих двух кодов свидетельствует о правильности выполнения такта "Сложение".

Цель изобретения — повышение достоверности контроЛя — достигается

Ъ за счет обнаружения сбоев произвольной кратности в выходном коде сумматора и любых константных неисправностей элементов устройства благодаря его существенным отличительным признакам.

Формула изобретения

Контролируемое арифметическое !

О устройство, содержащее первый и второй регистры операндов, входы которых подключены к соответствующим информационным входам устройства, а выходы — к соответствующим входам

15 сумматора, выходом соединенного с регистром результата и первым информационным входом блока сравнения кодов, о т л и ч .а ю щ е е с ятем, что, с целью повышения достоверности контроля, оно содержит блок поразрядного логического сложения операндов, блок элементов ИЛИ и блок элементов И-НЕ, входы которого соединены с соответствующими входами блока

1элементов ИЛИ и.соответствующими о входами сумматора, а выход — со вторым информационным входом первого регистра операндов, выход регистра результата подключен ко второму информационному входу второго регистра операндов, выход блока элементов ИЛИ подключен через блок поразрядного логического сложения операндов ко второму информационному входу блока сравнения кодов.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

М 551646, кл. G 06 F 11/04, 1977.

2. Авторское свидетельство СССР

9 297041, . G 06 F 11/00, 1968.

3. Авторское свидетельство СССР

Р 404084, кл. G 06 F 11/00, 1975 (прототип).

Составитель И. АлекСеев

Редактор И. Грузова Техред,Т,Маточка Корректор;A..Гриценко

Заказ 9434/48 Тираж 751 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул., Проектная, 4