Устройство для параллельного сдвига двоичных чисел

Иллюстрации

Показать всеРеферат

г

ly t

Союз Соавтсннх

Соцналнстнческнк

Республнк

ОП И И

ИЗОБРЕТЕНЙЯ

<»>792251

* .л

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

{61) Дс>полнительное к авт, свид-ву— (22) Заявлено 271278 (21) 2702956/18-24 (51)М Кл 3

G F 7/00 с присоединением заявки Йо (23) Приоритет

Государственный комитет

СССР но делам изобретениЯ и открыти Я

Опубликовано 30.1?80. Бюллетень HP 48

Дата опубликования описания 3 01280 (53) УДК 681. 3 (088.8) (72) Авторы изобретения

Ю. А. Кипецкий, Б. И.Смертыга, В. М. Тафель и А. Ф. Теслюк (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ПАРАЛЛЕЛЬНОГО СДВИГА

ДВОИЧНЫХ ЧИСЕЛ

Изобретение относится к вычислительной технике и может быть исполь зовано в ЦВМ для ускоренного выполнения арифметических и логических операций.

Известны схемы реверсивных сдвигающих регистров (1) .

Недостатком таких регистров сдвига является низкое быстродействие при организации сдвига информации на несколько разрядов, который осуществляется как последовательность сдвигов на один разряд.

Известна также схема ускоренного сдвига информации на заданное число 15 разрядов (2). В этой схеме имеются самостоятельные цепи сдвига на 2 разрядов, где n = 1, 2, ...,о . Сдвиг на любое число разрядов комбинируется из указанных элементарных сдвигов. 20

Недостатком такой схемы является недостаточно высокое быстродействие, так как количество тактов равно числу разрядов в двоичном коде задан° ного количества сдвигов. 25

Наиболее близким к изобретению является расширяемое устройство для параллельного сдвига двоичных чисел (3), содержащее m-разрядный регистр выходы которого соединены с первыми $P входами элементов И, расположенных в узлах кососимметричной матрицы умножения, вторые входы элементов

И подключены к выходам дешифратора кода сдвига, третьи входы элементов

И подключены к шинам сигналов левого сдвига или правого сдвига, а выходы элементов И поразрядно подключены к соответствующим входам группы элементов ИЛИ, выходы которой соответствуют разрядам двоичного числа и являются выходными шинами устройства.

С выхода дешифратора кода сдвига унитарный код сдвига построчно поступает на входы элементов И кососимметричной матрицы умножения. На другие входы элементов И поступают код mразрядного двоичного числа и сигналы левого сдвига или правого сдвига.

На выходе элементов И формируется результат умножения m-разрядного двоичного числа на 2, где n — укап затель числа сдвигов. Выходные шины дешифратора кода сдвига, соответствующие сдвигу на и разрядов вправо, также соответствуют сдвигу на m-n-1 разрядов влево, кроме случая сдвига на 0 разрядов.

Недостатком устройства-прототипа . является его сложность, связанная с

792251 необходимостью прошивки элементов кососимметричной матрицы по четырем координатам.

Целью изобретения является упрощение устройства.

Поставленная цель достигается тем, что устройство для параллельного сдвига двоичных чисел, содержащее

m-разрядный регистр, дешифратор кода сдвига, матрицу элементов И, группу элементов ИЛИ, причем входы m-разрядного регистра соединены с входными шинами устройства, а выходы — с первыми входами соответствующих элементов И каждой строки матрицы, вторые входы элементов И каждой строки матрицы подключены к соответствующим выходам дешифратора кода сдвига, первая группа входов дешифратора кода сдвига подключена ко входным шинам кода сдвига устройотва, а вторая группа входов — к управляющим шинам сигналов правого сдвига и левого сдвига, дополнительно содержит m элементов 2 И-ИЛИ, первые и вторые управляющие входы которых соединены соответственно с управляющими шинами сигналов левого сдвига и правого сдвига, а выходы — с выходными шинами устройства, выход каждого

j-го элемента и 1-ой строки матрицы (i = 1,..., m; j = 1, ., m), кроме первого элемента И первой строки и

m-ro элемента И m-ой строки, соединен,со входом (i + j — 2)-го элемента ИЛИ группы, первый информационный вход первого элемента 2 И-ИЛИ с выходом первого элемента И первой строки матрицы, первые информационные входы каждого k-ro элемента

2 И-ИЛИ (k 2, ..., m) соединены с выходом (k - 1)-го элемента ИЛИ группы, второй информационный вход каждого 1-ro элемента 2 И-ИЛИ (1

1, ..., m - 1) соединен с выходом (m + 1 - 2)-ro элемента ИЛИ группы, второй информационный вход m-ro элемента 2 И-ИЛИ соединен с Выходом

m-го элеМента И в-ой строки матрици.

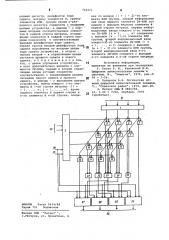

Схема устройства приведена на чертеже.

Устройство для параллельного сдвига двоичных чисел содержит

m-разрядный регистр 1, дешифратор кода сдвига 2, элементы И 3-18 косо симметричной матрицы, группу элементов ИЛИ 19-23, элементы 2 К-ИЛИ 2427,, управляющие шины сигналов правого сдвига 28 и левого сдвига 29, шины 30 кода сдвига, входные 31 и выходные 32 шины устройства.

Схема устройства изображена для случая m = 4.

Входы регистра 1 подключены ко входным шинам 31 устройства, входы дешифратора кода сдвига 2 подключены к шинам 30 кода сдвига и к управляющим шинам сигналов правого сдвига 28 и левого сдвига 29. Выходы регистра 1 соединены с первыми входами элементов И 3-18 кососимметричной матрицы по соответствующим косым столбцам. Вторые входы элементов И

i3-18 кососимметричной матрицы подключены по строкам к соответствующим выходам дешифратора кода сдвига. Выходы элементов И 4-17 по вертикальным столбцам соединены со входами (2m-3) элементов ИЛИ 19-23. Выход элемента

И 18 кососимметричной матрицы и выходы (m - 1) элементов ИЛИ 21-23 подключены к информационным входам элементов 2 И-ИЛИ 24-27. Выходы (m — 1) элементов ИЛИ 19-21 и выход элемен15 та И 3 кососимметричной матрицы подключены к другим информационным входам элементов 2 И-ИЛИ 24-27. Первый и второй управляющие входы элементов

2 И-ИЛИ 24-27 подключены к управляющим шинам сигналов соответственно леваго сдвига 29 и правого сдвига 28.

Выходы элементов 2 И-ИЛИ 24-27 соединены с выходными шинами 32 устройства.

Устройство работает следующим образом.

Информация, подлежащая сдвигу, заносится в регистр 1, с выходов которого число поступает на первые входы элементов И 3-18. На одном из выходов дешифратора кода сдвига 2 присутствует сигнал разрешения, поступающий на выбранную строку матрицы и соответствующий коду и направлению сдвига. С выходов элементов И

3-18 выбранной строки матрицы результат сдвига исходного числа через элементы ИЛИ 19-23 и элементы 2 И-ИЛИ

24-27 поступает на выходные шины

32 устройства. При сдвиге влево на щ выходах дешифратора кода сдвига 2 сигналы разрешения,:соответствующие возрастающему коду сдвига и (от 0 до m — 1) размещены в порядке возрастания (сверху вниз); При сдвиге вправо на выходах дешифратора кода сдвига 2 сигналы разрешения, соответствующие возрастающему коду сдвига и размещены в порядке убывания (снизу вверх). Окончательная выборка результата сдвига в зависимости от направления сдвига произво-! дится элементом 2 И-ИЛИ 24-27.

Технико-экономический эффект достигается за счет повышения техно логичности устройства путем уменьше55 ния количества координат прошивки кососимметричной матрицы до трех и уменьшения аппаратурных затрат (по критерию количества эквивалентных входов). Уменьшение аппаратурных затрат при щ .= 8 составляет 10% и с ростом m асимптотически стремится к 25%.

ФоРмУла изобретения

Устройство для паралпельного сдви- га двоичных чисел, содержаще m-раз792251

ВНИИПИ Эакаэ 943

Тираж 751 Подпис рядный регистр, дешифратор кода сдвига, матрицу элементов И, группу элементов ИЛИ, причем входы m-раэрядного регистра соединены с входными шинами устройства, а выходы — с пер- выми входами соответствующих элементов И каждой строки матрицы, вторые входы элементов И каждой строки матрицы подключены к соответствующим выходам дешифратора кода сдвига, первая группа входов дешифратора кода сдвига подключена ко входным шинам кода сдвига устройства, а вторая г .„ группа входов — к управляющим шинам сигналов правого сдвига и левого сдвига, о т л и ч а ю щ е е с я тем, что, с целью упрощения устройства, t5 н него дополнительно введены m элементов 2И-ИЛИ, первые и вторые управляющие входы которых соединены соответственно с управляющими шинами сигналов левого сдвига и правого 20 сдвига, а выходы — с выходными шинами . устройства, выход каждого )-го элемента И i-ой строки матрицы ()

1, ..., m; j = I, ..., m), кроме первого элемента И первой строки и

m-го элемента И m-ой строки, соедиФилиал ППП Патент, r Ужгород, ул, Проектная, 4 нен со входом (i + ) — 2)-го элемента ИЛИ группы, первый информацион ный вход первого элемента 2И-HJIH соединен с выходом. первого элемента И первой строки матрицы, первые инфор" мационные входы каждого k-го элемента 2И-ИЛИ )k 2, ..., m) соединены с выходом (k - !)-го элемента ИЛИ группы, второй информационный вход каждого 5-ro элемента 2И-HJIH (1

1, ..., m-1) соединен с выходом (m + 1 — 2)-ro элемента ИЛИ группы., второй информационный вход m-го элемента 2И-ИЛИ соединен с выходом .

m-го элемента и m-ой строки матрицы.

Источники.информации, принятые во внимание при экспертиэе

1. Каган Б. N., Каневский М.И.

Цифровые вычислительные машинЫ и системы. М., "Энергия", 1974, рис,354 — 3-56.

2. Папернов A.A. Логические основы цифровой вычислительной техники, "Советское радио", 1972, рис.26.

3, Патент США В 3961750, кл. G 06 F 7/00, опублик. 1976 (прототип).