Система микропрограммного управления

Иллюстрации

Показать всеРеферат

Ceos Советских

Сецнаинстнческих

Республик

О П И Н-ЖИ

ИЗОБРЕТЕНИЯ

«»792252

К АВТОРСКОМУ СВИ ЕПЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 04.0179 (21) 2706488/18-24 с присоединением заявки No (23) Приоритет

Опубликовано 30.1230. Бюллетень ЙЯ 48

Р1 1М. Кл.

G F 9/22

Госуяарстаенный коинтет

СССР

Ilo дмаи нзобретеннй н открытнй (5З) ÀÊ 681.325 (088.8) Дата опубликования описания 3Q1280

С. И. Емец, П. П. Куликов, И. Д. Петренко, В. A. Резвицкий и И. Г. Ханин (72) Авторы изобретения (71) Заявитель (54) СИСтемА МИКРОПРОГРАММНОГО УпРАВЛЕНия

Изобретение относится к вычислительной технике, в частности к устройствам микропрограммного управления, и может быть использовано при построении цифровых вычислительных машин и контроллеров с микропрограммным управлением.

Известно микропрограммное устройство управления (1),содержащее блок памяти, регистры, схемы приема 10 информации, генератор импульсов, счетчик тактов, элементы И, НЕ, дешифраторы, формирователь адресов микропрограммных слов.

Сложность такого устройства обус- 15 ловлена большим количеством разнотипного оборудования.

Наиболее близким к изобретению . по технической сущности и достигаемому результату является система 20 микропрограммного управления f2), содержащая адресную и управляющую

Памяти микрокоманд, память команд, арифметико-логическое устройство, интерфейс ввода-вывода, генератор им- 25 пульсов, регистр адреса памяти микрокоманд, регистр условий, узел выделения логических условий.

Однако такое устройство требует большого количества оборудования и Зр значительного увеличения объема адресной памяти микрокоманд в случае увеличения числа ветвлений микропрограмм.

Цель изобретения — сокращение обОрудования.

Эта цель достигается тем, что система микропрограммного управления, содержащая генератор импульсов, первый выход которого соединен с управляющими входами памяти команд, адресной и управляющеЯ памятями микрокоманд, первый выход адресной памяти микрокоманд связан с адресным входом регистра адреса памяти микрокоманд, выход памяти команд соединен с информационным входом регистра адреса памяти микрокоманд, разрядный выход которого подключен к адресному входу управляющей памяти микрокоманд, выход которой соединен с входом памяти команд и входом арифметикологического блока, а вход генератора импульсов является входом устрой" ства, содержит комбинационный сумматор и память констант переходов.

При этом выход логических условиЯ арифметико-логического блока соединен с входом логических условий памяти констант переходов, управляю,792252 щий вход которой соединен с вторым выходом генератора импульсов, а выход памяти констант переходов — с входом констант перехода комбинационного сумматора, адресный вход которого связан с разрядным выходом регистра адреса памяти микрокоманд. Выход комбинациониого Сумматора подключен к входу адресной памяти микрокоманд, второй выход которой связан с адресным входом памяти констант перехо- © дов.

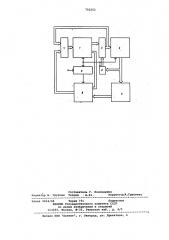

Блок схема микропрограммного устройства управления приведена на чертеже.

Система микропрограммного управлейия содержит адресную память 1 микрокоманд, регистр 2 адреса памяти микрокоманд, управляющую память 3 микрокоманд, арифметико-логическое устройство 4, генератор 5 импульсов, память 6 команд, комбинационный сум- 3) матор 7, память 8 констант переходов.

Адресная память 1 микрокоманд содержит адресные микрокоманды, формат которых включает адрес микрокоманды управляющей памяти 3 микрокоманд и вторую группу адресов памяти 8 констант переходов. Регистр 2 адреса памяти микрокоманд выдает адрес микрокоманды управляющей памяти 3 микрокоманд, который используется также в комбинационном сумматоре 7 для выработки следующего адреса адресной памяти 1 микрокоманд. Управляющая память 3 микрокоманд содер жит набор различных управляющих микрокоманд для задания режимов работы памяти 6 команд и арифметико-логического устройства 4.

Логические условия, вырабатываемые арифметико-логическим устройством, используются в качестве первой 4О группы адресов памяти 8 констант переходов.

Устройство работает следующим образом.

В каждом цикле, задаваемом гене- 4 ратором 5 импульсов, из адресной памяти 1 микрокоманд считывается текущая адресная.микрокоманда. Часть адресной микрокоманды используется, для адресации памяти 8 констант у переходов. Другая часть заносится в регистр 2 адреса памяти микроквманд, который определяет адрес управляющей памяти 3 микрокоманд.

Этот же адрес подается на первый . вход комбинационного сумматора 7 для определения следующего адреса .адресной памяти 1 микрокоманд. Микрокоманда, считанная .из управляющей памяти 3 микрокоманд, подается на вход арифметико-логического устройст- go ва 4, которое по выполнению операций формирует логические условия, являющиеся первой группой адресов памяти 8 констант переходов. При отсутствии ветвления в микропрограмме адрес следующей микрокоманды адресной памяти микрокоманд определяется содержимым регистра адреса памяти микрокоманд, поскольку константа перехода в этом случае равна О. Определение адреса следующей микрокоман,ды в случае ветвления микропрограммы осуществляется путем суммирования содержимого регистра адреса памяти микрокоманд и константы перехода, считанной из памяти констант переходов.

Наличие в составе данного устройства комбинационного сумматора и памяти констант переходов позволяет исключить дополнительные схемы управления адресной памяти микрокоманд, что обеспечивает сокращение количества оборудования, а.исключение повторяющихся микрокоманд ведет к уменьшению объема памяти микрокоманд.

Формула изобретения

Система микропрограммного управления, содержащая генератор импульсов, первый выход которого соединен с управляющими входами памяти команд, адресной и управляющей памятями микрокоманд, первый выход адресной памяти микрокоманд соединен с адресным входом регистра адреса памяти микрокоманд, выход памяти команд соединен с информационным входом регистра ад-. реса памяти микрокоманд, разрядный выход которого подключен к адресному входу управляющей памяти микрокоманд, выход которой соединен с входом памяти команд и входом арифметико-логического блока, а вход генератора импульсов является входом устройства, отличающаяся тем, что, с целью сокращения оборудования, оно содержит комбинационный сумматор и память констант переходов, причем выход логических условий арифметикологического блока соединен с логическим входом условий памяти констант переходов, управляющий вход которой соединен с вторым выходом генератора импульсов, а выход памяти констант соединен с входом констант перехода комбинационного сумматора, адресный вход которого соединен с разрядным выходом регистра адреса памяти микрокоманд, а выход комбинационного сум матора подключен к входу адреСной памяти микрокоманд, второй выход которой связан с адресным входом памяти констант переходов.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

М 416696, кл. G 06 F 9/16, 1974.

2. Патент США Р 4.038.643, кл. G 06 F 9/16, 1977 прототип), 792252

Составитель Г. Пономарева

Техред, A,Ач Корректор!А.Гриценко

Редактор И. Грузова

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4

Заказ 9434/48 Тираж 751 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5