Устройство для контроля дискретной аппаратуры

Иллюстрации

Показать всеРеферат

О П И С А Н И Е < 792259

ИЗОБРЕТЕН Ия

Союз Советски и

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свкд-ву(22) Зая влено 18 12 78 (21) 2700128/18 -24 с присоединением заявки Ж— (23) fl рноритет (51)М. Кл.

G 06 F 11/30

Веударстееииый камитет

СССР по деяам изобретеиий и открытий

Опубликовано 30.12 80 Бюллетень,% 48 (53) УДК 681.325.

65:621.382 (088.8)

Дата опубликования описания 30.12,80

,(72) Автор| . изобретения

Н. И. Лукинов (71) Заявитель (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ДИСКРЕТНОЙ АППАРАТУРЫ

Изобретение относится к области вычисли. тельной техники и может быть использовано для контроля и испытания дискретной аппаратуры, требующей для своего функционирования управляющих воздействий, подаваемых в реальном масштабе времени, например, работающей в составе автоматизированной системы управления быстропротекающими технологическими процессами.

Известно устройство для контроля дискретной аппаратуры, содержащее блок вэанмодей!

О ствия с оператором, блок отображения и регистрашш, блок управления, солрягаемый с цифровой вычислительной машиной, и блок подключения к объекту контроля (1}.

Это устройство осуществляет контроль дискретной аппаратуры путем программирования цифровой вычислительной машины (ЦВМ) и выдачи управляющих и тестовых воздейст- д вий на объект контроля через ее каналы ввода-вывода, а также получением от контролируемой аппаратуры результатов контроля и сравнением нх с эталонными значениями.

Недостатком устройства является низкое быстродействие при выдаче управляющих и тестовых воздействий, обусловленное необходимостью обращеш я программ контроля к таймерам и средствам прерываний программ

ЦВМ для подачи асинхронных тестовых воздействий.

Наиболее близким техническим решением к изобретению является устройство для контроля дискретной аппаратуры, . содержащее блок обмена, блок управления, блок отображения и блок регистрации, причем первый, второй н третий выходы блока управления подключены к первому входу контролируемой аппаратуры, входу блока регистрации и входу блока отображения соответственно; первый вход — к выходу вычислителя через блок обмена, а второй -- к выходу контролируемой аппаратуры (2).

Недостатком известного устройства является использование режима разделения времени с обращением к аппарату прерываний и таймерам ЦВМ для организации асинхронной подачи тестовых воздействий через произвольно

792259

10 ний оператору. заданные интервалы времени, что существенно

/снижает быстродействие устройства.

Целью изобретения является повышение быстродействия устройства.

Поставленная цель достигается тем, что в устройство, содержащее блок обмена, блок управления, первый, второй и третий выходы которого подключены к первому входу контролируемой дискретной аппаратуры, входу блока регистрации и входу блока отображения соответственно, первый вход через блок обмена к выходу вычислителя, а второй вход — к выходу контролируемой дискретной аппаратуры, введены коммутатор, генератор импульсов, первый и второй элементы И, первый и второй счетчики, первый и второй блоки сравнения, первая и вторая вентильные группы, первый, второй,, третий и четвертый блоки памяти, причем первые входы первого и второго блоков

I памяти подключены через блок обмена к выходу вычислителя, первый блок памяти первым выходом подключен через первую вентильную группу к первым входам соответственно третьего блока памяти и коммутатора, соединенного выходом со вторым входом контролируемой дискретной аппаратуры; первый и третий блоки памяти вторыми выходами подключены ко входам первого и второго элементов И соответственно, а третьими выходами — к первым входам соответственно первого и второго блоков сравнения, выходы которых подключены ко входам первой, второй вентильных групп и вторым входам первого и третьего блоков памяти соответственно, вторые входы — к выходам соответственно первого и второго счетчиков, входы которых соединены через первый и второй элементы И соответственно с выходом генератора импульсов, а третий блок памяти первым выходом подключен через вторую вентильную группу к первому входу четвертого и к второму входу второго блоков памяти, выходы которых соединены со вторым и третьим входами коммутатора соответственно.

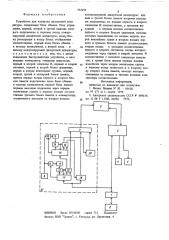

Блок-схема устройства представлена на чертеже, Устройство содержит блок 1 обмена, блок 2 управления, соединенный входом и выходом с объектом контроля 3, блок 4 регистрации, блок 5 отображения, причем вход блока 1

1 обмена соединен с выходом вычислителя 6, коммутатор 7, генератор 8 импульсов, первый

9 и второй 10 элементы И, первый 11 и второй 12 счетчики, первый 13 и второй 14 блоки сравнения, первая 15 и вторая 16 вентильные группы, первый 17, второй 18, третий 19 и четвертый 20 блоки памяти, причем блоки

7 -20 образуют программируемый синхронизатор 21.!

Блок 1 обмена предназначен для ввода из вычислителя 6 управляющей, адресной и тестовой информации, а также ввода в вычислитель

6 результатов контроля.

Блок 2 управления предназначен для управления обменом тестовой и управляющей информацией, а также информацией о результатах контроля в процессе взаимодействия с контролируемой дискретной аппаратурой 3.

Блок 4 регистрации предназначен для документирования результатов контроля и сообщеБлок 5 отображения предназначен для индикации результатов контроля и сигналов, соответствующих отклонениям измеряемых параметров.

Вычислитель 6 предназначен для автоматизированного управления контрольными операциями и для обработки результатов контроля при большом объеме измерений.

Коммутатор 7 предназначен для объединения и перераспределения кодовой информации, поступающей от первого 17 и второго 18 блоков оперативной памяти, и выдачи ее на вход контролируемой аппаратуры 3.

Генератор 8 импульсов предназначен для управления работой счетчиков 11, 12, поступление сигналов на которые обеспечивают элементы И 9, 10.

Блоки 13, 14 сравнения предназначены для сравнения кодов времени с выходов счетчиков 11, 12 и с третьих выходов блоков 17, 19 соответственно.

Вентильные группы 15, 16 предназначены для выдачи кодов с первых выходов блоков

17, 19 в моменты совпадения кодов в блоках 13, 14 соответственно, Первый блок 17 оперативной памяти предназначен для хранения и выдачи изменяемой от вычислителя 6 управляющей информации, осуществляющей включение в работу блока

19 и передачу на контролируемую дискретную аппаратуру 3 через коммутатор 7 кодов адреса, команд и контрольных тестов.

Второй блок 18 оперативной памяти предназначен для хранения изменяемых от цикла к циклу контрольных тестов или команд управления и выдачи их под управлением от блока 19.

Третий блок 19 полупостоянной намял предназначен для долговременного хранения и выдачи управляющей информации, осуществляющей считывание двоичных кодов из ячеек полупостоянной памяти четвертого блока

20 и ячеек оперативной памяти блока 18 в заранее запрограммированные моменты времени относительно появления команды на первом входе блока 18.

Программируемый синхронизатор 21 в целом предназначен для предварительного запоминания

5 792259 изменяемой от цикла к циклу контроль-информации и команд управления, постоянного хранения неизменной от шлкла к циклу контрольной информации и команд управления, а также для выдачи тестов контроля и управляющей информации с высокой скоростью в заранее запрограммированные моменты времени на вход контролируемой дискретной аппаратуры 3.

Устройство работает следующим образом.

Вычислитель 6 подает в течение всего процесса контроля через блок 1 обмена и блок

2 управления контрольную программу, включающую синхронные тестовые наборы, поступающие через равные интервалы времени на контролируемую дискретную аппаратуру 3.

Перед началом работы вычислитель 6 вводит через блок 1 в блоки 17, 18 контрольную программу, включающую асинхронные тестовые наборы, подача которых должна производиться через неравные моменты времени.

Двоиный код момента времени выдачи данного тестового набора записан в его разрядной сетке. Аналогичная контрольная программа, включающая необходимые при контроле константы и коды времени, вводится в блоки 19, 20.

С приходом команды управления от вычислителя 6 через блок 1 обмена блок 17 вырабатывает импульс, по которому открывается первый элемент И 9 и синхроимпульсы от генератора 8 поступают на вход счетчика 11.

В момент совпадения кодов времени, поступающих из блока 17 и от счетчика Il, первый, блок 13 сравнения кодов выдает на первую группу венп лей 15 и на второй вход блока

17 импульсы, по которым блок 17 выдает содержимое ячейки оперативной памяти. В результате этого на вход блока 19 и на первый вход коммутатора 7 с выходов первой группы вентилей 15 поступают коды команд и тестов соответственно.

При поступлении кода команды на блок 18 последний вырабатывает импульс, по которому открывается второй элемент И 10 и синхроимпульсы от генератора 8 поступают на вход второго счетчика 12. В моменты совпадения кодов времени, поступающих пз блока 19 и от счетчика 12, второй блок 14 сравнения кодой выдает на вторую группу вентилей 16 и на вход блока 19 импульсы, по которым блок 19 выдает содержимое ячейки полупостоянной памяти. В результате с выходов группы вентилей 16 поступают коды адресов ячеек на вход блока 20 и второй вход блока 21, соответствую цих данной микрокоманде. С приходом кодов адресов осуществляется считывание содержимого соответствующих ячеек блоков 18, 20. в результате

5 о

Скорость выдачи команд управления и контрольных тестов с выхода программируемого синхронизатора 21 зависит от быстродействия счетчика 12, блока сравнения 14, а также от времени считывания кодов из блоков оперативной 18 и полупостоянной 19, 20 памяти и может быть получена сколь угодно большой в зависимости от характеристик применяемых элементов. При этом затраты времени на организацию н обработку прерываний от таймеров ЦВМ существенно снижаются, так как программы контроля вводят в блоки 17, 18 операплвной памяти предлагаемого устройства в виде больших массивов кодовых слов однократно в процессе контроля.

Таким образом, применение третьего и четвертого блоков полупостоянной памяти 19, 20 для хранеш я микрокоманд, первого и второго счетчиков 11, 12 и блоков 13, 14 сравнения кодов позволяет повысить быстродействие устройства контроля дискретной аппаратуры. Кроме того, применение третьего 19> четвертого 20 блоков полупостоянной памяти для хранения неизметюй от цикла к циклу контрольной и управляющей информацти позволяет вести обмен с вычислителем только оперативно изменяющейся в процессе контроля информации, что сокращает объем и время обмена.

55 чего коды команд или тестов, неизменных BO времени контроля (от блока 20) или изменяемых во времени (от блока 18), поступают на второй и третий входы коммутатора 7 и далее с его выхода на второй вход контролируемой дискретной аппаратуры 3.

Окончание работы блока 19 производит команда, поступающая от блока 17 или формируемая самим блоком 19 в соответствии с реализованной микропрограммой. При этом блок 19 закрывает элемент И 10, в результате чего счетчик 12 переводится в нулевое состояние. После этого от блока 17 может, быть подана следующая команда по включению блока 19 в работу для выдачи следующей разновидности команд (кодов команд и тестов контроля) .

Окончание работы программируемого синхронизатора 21 вызывает команда, поступающая от вычислителя 6 через блок обмена 1 на вход блока 17 или формируется в блоке

17 в соответствии с окончанием программы контроля. При этом блок 17 закрывает элемент И 9, в результате чего счетчик 11 переводится в нулевое состояние. После этого в оперативную память блоков 17, 18 от вычислителя 6 может быть записана новая программа контроля, использующая другие разновидности микропрограмм блока 19.

792259

Формула изобретения

Устройство для контроля дискретной аппаратуры, содержащее блок обмена, блок управления, первый, второй и третий вььходы которого подключены к первому входу контролируемой дискретной аппаратуры, входубло-. ка регистрации и входу блока отображения соответственно, первый вход блока обмена— к выходу вычислителя, а второй вход — к выходу контролируемой дискретной аппаратуры, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия устройства, в него введены коммутатор, генератор импульсов, первый и второй элементы И, первый и второй счетчики, первый и второй блоки сравнения, первая и вторая вентильные группы, первый, второй, третий и четвертый блоки памяти, причем первые входы первого и второго блоков памяти подключены через блок обмена к выходу вычислителя, первый блок памяти первым выходом подключен через первую вентильную группу к первым входам соответ. ственно третьего блока памяти и коммутатора, соединенного выходом со вторым входом

8 контролируемой дискретной аппаратуры; первый и третий блоки памяти вторыми выходами подключены ко входам первого и второго элементов И соответственно, а третьими выходами — к первым входам соответственно первого и второго блоков сравнения, выходы которых подключены ко входам первой, второй вентильных групп и вторым входам первого и третьего блоков памяти соответственно, вторые входы — к выходам соответственно первого и второго счетчиков, входы которых соединены через первый и второй элементы И соответственно с выходом генератора импульсов, а третий блок памяти первым входом подключен через вторую вентильную группу к первому входу четвертого и к второму входу второго блока памяти, выходы которых соединены со вторым и третьим входами коммутатора соответственно.

Источники информации, принятые во внимание при экспертизе

1. Патент Японии N 50 — 16618, кл 97 (7) G 1, опубл. 1975.

2. Авторское свидетельство СССР У 498619, кл, G 06 F 11/00, опубл, 1976.

ВНИИ11И Заказ 10136/49 r ираж 751 Подписное

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4