Устройство для решения уравнений вида

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик

< >792262

Ф

1 (6t) Дополнительное к авт. саид-ву (22) Заявлено 04,12.78 (21) 2691513/18-24 с присоединением заявки,% (23) Приоритет (5 l ) M. Кл.

G 06 F 15/32

Гасударственный комитет СССР по данаи изобретений и открытий

Опубликовано 30.12.80. Бюллетень р6 48 (53) УДК 681.14 (088.8) Дата опубликования описания 30.12.80 (72) Авторы изобретения

В. Б, Дудыкевич и В. Н. Максимович (7I) Заявитель (54) УСТРОЙСТВО ДЛЯ РЕШЕНИЯ УРАВНЕНИЙ ВИДА

«2 У2 +У2

Устройство относится к области вычислительной техники и может быть использовано в специализированных вычислительных системах и измерительных преобразователях.

Известно устройство, содержащее регистр, группу элементов И, сумматор, элемент И, 5 элемент задержки и квадратор.

Недостаток этого устройства заключается в его черезмерной сложности, обусловленной наличием в его составе квадратора (1). l0

Наиболее близкое по своей сущности к предлагаемому устройству-устройство, содержащее две схемы сравнения, дешифратор, две группы элементов И, группу элементов ИЛИ, реверсивный счетчик, сумматор, два элемента И и два триггера (21. !

Недостатком такого устройства является его сложность.

Другой недостаток устройства — низкое

20 быстродействие, обусловленное тем, что процесс решения уравнений в известном устройстве происходит в два этапа: на первом этапе формируется квадрат одного из аргументов, а на втором — результирующее выражение.

Цель изобретения — повышение быстродействия устройства.

Поставленная цель достигается тем, что в устройство, содержащее первую и вторую группы элементов И, первый элемент ИЛИ, дешифратор, введены блок суммирования, блок вычитания, суммирующий счетчик, вычитающий счетшк, второй элемент ИЛИ. При этом выходы блока суммирования и блока вычитания соединены соответственно со входами суммирующего и вычитающего счетчиков, группа выходов суммирующего счетчика через соответствующие элементы И первой группы — с группой входов первого элемента

ИЛИ, вход которого подключен к выходу суммирующего счетчика. Группа выходов вычитающего счетчика соединена с группой входов дешифратора непосредственно и через вторую группу элементов И с группой входов второго элемента ИЛИ. Вход дешифратора подключен к выходу вычитающего счетчика и ка входу второго элемента ИЛИ, 7922б2 выходы первого н второго элементов ИЛИ

|соединены соответственно с первыми входами блока суммирования и блока вычитания, вторые входы которых подключены ко входу тактовых импульсов устройства, а их третьи входы — к выходу дешифратора.

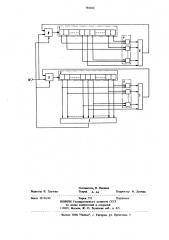

На чертеже представлена схема устройства.

Оно содержит суммирующий счетчик 1, вычитающий счетчик 2, дешифратор 3, две группы элементов И 4 и 5, элементы ИЛИ 6 и 7, блок 8 суммирования и блок 9 вычитания, вход 10 устройства, Счетчики 1 и 2 являются п-разрядными.

Процесс вычисления в устройстве начинается в момент записи числа х в счетчик 2 и числа у в счетчик 1. При этом дешифратор 3 открывает ключевые элементы, расположенные в блоках 8, 9, и тактовые импульсы с входа 10 устройства поступают на входы счетчиков 1 и 2. В момент перехода счетчика 2

s нулевое состояние дешифратор 3 закрывает ключевые элементы, расположенные в блоках

8, 9, и процесс вычисления в устройстве заканчивается.

Таким образом, в процессе вычисления происходит изменение числа в счетчике 1 от у до 7., а в счетчике 2 - от х до О, где .г. — решенйе уравнения.

Повышение быстродействия достигается бла годаря тому, по результат решения уравнения формируется в устройстве в один этап, а в прототипе — в два этапа, причем время одного этапа вычисления в данном устройстве не больше времени вычисления первого этапа в прототипе.

Формула изобретения устроиство для решения уравнении вида

2 =x2+ у, содержащее первую и вторую

2 2 группы элементов И, первый элемент ИЛИ, дешифратор, отлич ающе еся тем, что, с целью повышения быстродействия, в него введены блок суммирования, блок вычитания, суммирующий счетчик, вычитающий О счетчик, второй элемент ИЛИ, причем выходы блока суммирования и блока вычитания соединены соответственно со входами суммирующего и вычитающего счетчиков, группа выходов суммирующего счетчика соединена через

1s соответствующие элементы И первой группы с группой входов первого элемента ИЛИ, вход которого подключен к выходу суммирующего счетчика, группа выходов вычитающего счетчика соединена с группой входов деэп шифратора непосредственно и через вторую группу элементов И с группой входов второго элемента ИЛИ, вход дешифратора подключен к выходу вычитающего счетчика и ко входу второго элемента ИЛИ, выходы первого и второго элементов ИЛИ соединены соответственно с первыми входами блока суммирования и блока вычитания, вторые входы которых подключены ко входу тактовых импульсов устройства, а их третьи входы

30 к выходу дешнфратора

f Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР И 392494, кл. G 06 F 7/38, 1971.

2. Авторское свидетельство СССР Н 453б97, кл. G 06 F 15/32, 1973.

792262

Составитель Н. Палеева

Техред А, дл Корректор М. Демчик

Редактор И. Груэова

Заказ 10136/49

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4

Тираж 751 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Рауиюкая наб., д. 4/5