Аналого-цифровой преобразователь

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Соввтских

Социвлистичвск их

Республик ()792581 (61) Дополнительное к авт. свид-ву Э. (51)М. Кл.

Н 03 К l3/17 (22) Заявлено 30.05.75(21) 2l38245/l8-2l с присоединением заявки М (23) Приоритет

Опубликовано 30.l2.80. Бюллетень .% 48

Пвударотвеиимй комитет

СССР ао лвваи изобретений и OtlfphlTN11 (53) УДК 88l.

325(088 8) Дата опубликования описания 03.0l 81. (72) Авторы изобретения

Л. А. Брякни, Н. П. Вашкевич и В. Ф. Говоров

Пензенский политехнический институт (7I ) Заявитель (54) АНАЛОГО-БИФРОВОЙ

ПРЕОБРАЗОВАТЕЛЬ

Изобретение относится к вьгчислительной технике.

Известен аналого-цифровой преобразователь, содержащий реверсивный счетчик, выходы которого через элементы

ИЛИ соединены с входом элемента И, выход которого через аналоговое интегрирующее устройство и нуль-opraH генераторного типа подключен к управляющим входам вентелей сложения и "вычитания реверсивного счетчика P) .

Недостатком устройства является низкое быстродействие, Известен также аналого-цифровой преобразователь, содержазцнй! сравнивающее устройство, выходы которого через дифференцирующие блоки и элемент ИЛИ соединены со входом триггерного счетчика; первый выход которого подключен к входу основного реверсивного счетчика а второй выход — к входу дополнительзаого реверсивного счетчика, основные входы которого соединены со входами основного реверсивного счетчика(2).

Недостатком аналого-цифрового преобразователя является низкое быстродействие иэ-аа большого времени установ. ления переходных пропессов при включении и вьпипочении старших разрядов

5 цифроаналогового преобразователя, включенного в обратную цепь.

Белью изобретения является повышение быстродействия аналого-цифрового преобразователя.

1О

Это достигается тем, что в аналогопифровом преобразователе, содержащим козапаратор, цифроаналоговый преобразователь, два реверсивных счетчика, ге15 нератор импульсов, введены дополнительные компаратор и шерроаналоговый преобразователь, источник тока, два элемента И, элемент ИЛИ и инвертор, причем первый вход дополнительного компаратора соединен со вторым входом компаратора„второй вход — с выходом дополнительного цифроаналогового преобразователя, цифровые входы которого соединены с выходом второго реверсивного счетчике, а вход соединен с выходом генератора тока, выходы компаратора дополнительного компаратора соединены с первыми входами элементов И, вторые входы которых соединены с прямым и инверсным выходами первого реверсивного счетчика, а выходы через элемент ИЛИ соединены с входом инвертора и входами "вычитание пер — вого и второго реверсивных счетчиков, входы сложение" которых соединены с выходами инвертора.

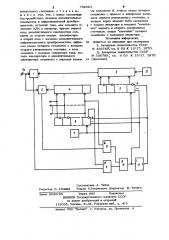

На чертеже приведена структурная электрическая схема предлагаемого уст) ройства, Устройство содержит компараторы 1 и 2, цифроаналоговые преобразователи 3 и 4, реверсивные счетчики 5 и 6, генератор 7 импульсов, элементы И 8 и 9, элемент ИЛИ 10, инвертор 1l, источ° ник 12 тока..

Принцип работы устройства заключает- ся в следующем.

В любой такт преобразования содержимое реверсивных счетчиков 5 и 6 отличается на единицу младшего разряда.

При этом время установления выходного напряжения цифроаналогового преобразователя И длительно, так как коммутируются токи всех разрядов. Время установления выходного напряжения дополнительного цифроаналогового преобразователя определяется лишь временем пе:.реходных процессов при коммутации тока в младшем разряде. Благодаря питанию источника 3.2 выходные уровни, к которым устанавливаются напряжения на выходах цифроаналоговых преобразователей

4 и 3, одинаковы. Это позволяет при коммутации токов в старших . разрядах цифроаналогового преобразователя 4, не дожидаясь окончания переходных процессов на его выходе, осуществить очередной такт преобразования, используя компаратор 1. и цифроаналоговый преобразователь 3, время установления переходнего прсцесса в котором гораздо меньше

Предположим,что после очередного такта уравновешивания реверсивный счет чик 6 содержит код Ol...ll, а реверсивный счетчик 5 содержит код 01...10.

В этом случае с прямого выхода младшего разряда реверсивного счетчика 6 поступает логическая единица на вход элемента И 8. Это позволяет информации с выхода компаратора 2 через элемент ИЛИ 10 поступить на управляющие входы реверсивных счетчиков 5,6.

258 l 4

Элемент И 9 закрыт сигналом инверсного выхода триггера младшего разряда реверсивного счетчика 6.

Предположим, что в момент прихода очередного тактового импульса с генераторе 7 сигнал с выхода компаратора 2 разрешает режим сложения счетчиков. В этом случае новое состояние реверсивных счетчиков 5,6 соответствует кодам

10 10...00 и 03...1l. В этом случае раз(решается прохождение информации через элемент И 9 и запрещается прохождение

Г информации через элемент И 8 и режим работы реверснвных счечиков 5, 6 к приходу следующего тактового импульса с генератора

7 определится сигналом на выходе компаратора 1»

Всякий раз, когда состояние младшего разряда реверсивного счетчика 6 соответствует логической единице, в такте преобразования участвуют компаратор 2, реверсивный счетчик 6 и цифроаналоговый преобразователь 4. При логическом "нуле в младшем разряде реверсивного счетчика 6 в такте преобразования участвуют компаратор 1, реверсивный счетчик 5 и цифроаналоговый преобразователь 3.

В следующем преобразователе длитель ность такта преобразования определится соотношением

Тт = Туст + Т + Тцс где Т вЂ” длительность такта преобраТ зов ания;

Т С вЂ” время установления переходных процессов в цифроаналоговом преобразователе; .—

Тк, Т - время задержки информации в компараторе и цифровой схеме соответственно.

Время установления цифроаналогового преобразователя определяется установлением с заданной точностью старшего разряда. В зависимости от числа разрядов это время колеблется в пределах (6-4.0), где p — постоянная времени переходных процессов цифроаналогового преобразователя.

Устройство йозволяет сократить такт преобразования в 2-3 раза.

Формула изобретения

Аналого-цифровой преобразователь соУ держащий компаратор, первый вход которого соединен с выходом цифроаналогового преобразователя, входы которого соедине- ны с выходами первого реверсивного счет. чика, выход генератора импульса соединен с первыми входами первого и второго

79258 реверсивных счетчиков, о т л и ч а юшийся тем р что с пелью повьпп(жщР быстродействия, введены дополнительные компаратор и цифроаналоговый преобразователь, источник тока, два элемента И, элемент ИЛИ и инвертор, причем первый вход дополнительного компаратора соединен со вторым входом компаратора, а второй вход с выходом дополнительного пнфроаналогового преобразователя, цифро- 16 вые входы которого соединены с выходом второго реверсивного счетчика, а вход соединен с выходом генератора тока, выходы компаратора и дополнительного коМпаратора соединены с первыми входа, 15

l 4 ми элементов И, вторые входы которых соединены с прямым и инверсным выходами первого реверсивного. счетчика, а выходы через элемент ИЛИ соединены с входом инвертора и.входами "вычитание" первого и второго реверсивных счетчиков, входы сложение которых соединены с выходами инвертора.

Источники информапии, принятые во внимание при экспертизе.

1. Авторское свидетельство СССР ,% 335786, кл. ff 03 К 3.3/17, 1970, 2. Авторское свидетельство СССР

N 336798. кл. Н 03 К 13/l7. 1970 (прототип) .. Составитель А. Taros

Редактор .О. Степина Техред Е.Гаврилешко Корректор iB. Бутага1

Заказ 9620/65 Тарахс 995 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

ll303S, Москва, Ж»35, Раушская наб., д. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4