Устройство для защиты от импульсных помех

Иллюстрации

Показать всеРеферат

(< i>792599

Союз Советских

Социалистических

Республик

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (6! ) Дополнительное к авт. свид-ву (22)Заявлено08.01.79 (21) 2709420/18 21 с присоединением заявки РЙ (23) П риоритет

Опубликовано 30.12.80. Бюллетень ),ь. 48

Дата опубликования описания Q6 01.81 (5l ) M. Кл.

Н 04 B 15/QQ

ФЬоудоротвенный комитет

СССР йв аелем изобретений и открытий (53) УДК 621.374.. 3(088.8) (72) Авторы изобретения

В. А. Артеменко и E. Г. Белый -Ткач (71) Заявитель (54) УСТРОЙСТВО ЗАЩИТЫ ОТ ИМПУЛЬСНЫХ ) 0МЕХ- — -- — --.

f <,r

Ф . а ° . .., Изобретение относится к импульсной технике и может быть использовано в цепях защиты радиозлектронной аппаратуры от импульсных помех, в частности от помех, возникающих в результате дребезга механических контактов.

Известно устройство защиты от импульсных помех, содержащее времязадающую цепь, выполненную в вйде сдвигового регистра, выходы последовательных

1О каскадов которого подключены к элементу совпадения, датчик тактовых импульсов, управляющий сдвиговым регистром и подключенный к одному иа входов элемента совпадения1 1).

Недостаток устройства ааключается в том, что оно исключает вози;ожность аащиты от помех импульсов, длительность которых превышает длительность полезных сигналов.

Наиболее блиаким к изобретению является устройство защиты от импульсных помех, содержащее логический элемент

И-Н Е, инвертор, времяаадающую цепь,соо2 стоящую иа последовательно соединенных конденсатора и двух реаисторов, последний из которых подключен к. общей шине Р23.

Недостатком этого устройства также является низкая эффективность нашиты иа-эа невоаможности устранения помех от импульсов, длительность которых превышает длительность ттолеаного сигнала.

Бель иэобретения ааключается в повышении эффективности защиты путем уст ранения помех от импульсов, превышающих длительность полезного сигнала.

Поставленная цель достигается тем, что в устройство аащиты от импульсных помех, содержащее логический элемент

И-НЕ, инвертор, времяаадающую цепь,состоящую иэ последовательно соединенных конденсатора и двух резисторов, последний иэ которых соединен с общей шиной, введены цепь аашиты верхнего предельного значения логической единицы, цепь зашиты нижнего предельного аначения логической единицы и дополнительный рези7935

3 ,стор, причем цепь защиты нижнего предельного значения логической единицы состоит из последовательно соединенных (входного резистора, первого стабилитрона и резистора нагрузки, причем анод стаб билитрона соединен с первым входом логического элемента И-НЕ и через допол нительный резистор — с выходом инвертора, вход которого подключен .к выходу логического элемента И-НЕ, цепь защиты верхнего предельного значения логической единицы содержит второй стабилитрон и . транзистор, коллектор которого подключен к второму входу логического.элемента И-НЕ, эмиттер - к общей шине, а база - к общему выводу резисторов времязадающей цепи и аноду второго стабилитрона, катод которого соединен с катодом первого стабилитрона.

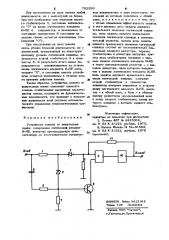

На чертеже представлена функциональ- ная схема устройства защиты от импульсных помех, Устройство защиты от импульсных помех содержит цепь защиты нижнего предельного значения логической единицы, состоящей из последовательно соеди-.. ненных входного резистора 1, первого стабилитрона 2 и резистора 3 нагрузки; включенного между первым входом логического элемента И-НЕ 4 и общей ши ной, времяэадающую цепь, состоящую из последовательно соединенных конденсатора 5 и резистивного делителя, выполненного на резисторах 6 и 7, цель защиты: верхнего предельного значения логической единицы, состоящую иэ транзистора 8, . резистора 7, стабилитрона 9 и входного резистора 1, причем анод первого стабилитрона подключен к первому входу логического элемента И-НЕ и к выходу инвертора 10 через резист ор . 1 1. К вто49 . рому входу логического элемента И-НЕ . подключен коллектор транзистора, его

Ф эмиттер соединен с общей шиной, а база - с выходом резистивного делителя и анодом второго стабилитрона, катод ко45 торого соединен с катодом первого стабилитрона. Выход логического элемента

И-НЕ соединен с входом инвертора.

Устройство защиты от импульсных помех работает следующим образом.

В исходном состоянии, когда на входе устройства сигнал отсутствует, на первом входе, логического элемента И-HE 4, соединенным с общей шиной через резистор

3 нагрузки с достаточно малым сопротивлением, имеет место логический "0", на втором входе, связанном с общим прово-

99 4 дом через закрытый транзистор 8, — логическая l"„на выходе логического элемента И-НЕ 4 и входе инвертора 10 îгическая "1», на выходе инвертора 10 и выходе устройства - логический 0 .

С момента подачи на вход устройства сигнала с логической "1 верхнего уровня до момента окончания заряда конденсатора 5 (через цепь: вход устройства - конденсатор 5 - резистор 6 -не-! реход база-эмиттер транзистора 8 и резистор 7) транзистор 8 открыт, и второй вход логического элемента И-НЕ 4 соединен с общей шиной через сопротив« ление открытого транзистора 8.

Одновременно при открытии первого стабилитрона 2 происходит деление напряжения сигнала между элементами цепи входного резистора 1, первого стабилитрона 3 и резистора 3 нагрузки, в резуль тате чего на первом входе логического элемента И-НЕ 4 образуется сигнал логической "1" - второго уровня.

При сохранении в течение указанного интервала времени (aapR@a конденсатора

5) на втором входе логического эйемента И-НЕ 4 логического - О" состояние ее выхода не изменяется, и сигнааы на выход схемы не проходит.

После окончания процесса вара@а конденсатора 5 транзистор . 8 защмивавтоа4 и на втором входе логического элемента

И-НЕ 4 восстанавливается логическая

"1". Состояние выхода логического элемента И-НЕ 4 и входа инвертора ХО «еменяется на логический О», а выхода инвертора и выходе логического элемента

И-НЕ - на логическую 3., При передаче логического уровни (сигнала сколь угодно большой дли-, тельности) схема РаботаеР аналогично, С появлением на входе схемы сигнала .помехи длительностью меньше заданной процесс заряда конденсатора за время его действия, не успевает завершиться., B результате этого в течение всего времени его действия транзистор 8 остается открытым, на входе логического элемента И-НЕ 4 сохраняется состояние логического О, а на его выходе - логи ческой «1 .

Аналогично устройство работает от воздействия каждого из серии импульсов, обусловленных дребезгом коммутирующего контакта, установленного, например, между некоторым источником напряжения ,и входом устройства защиты.

2599

5 79

При поступлении на вход помехи любой длительности, но с амплитудой не более, чем это необходимо для открытия первого стабилитрона 2, состояние логического 0" на входе логического элемента

И-HE 4 сохраняется, и независимо от состояния транзистора 8 состояние на

: выходе схемы остается неизменным (логический 0 ) ..

При поступлении на вход помехи сколь угодно большой длительности, но с амплитудой, превышающей на некоторую величину уровень логической единицы, от.крываются второй стабилитрон 9 и транзистор 8. В результате этого канал перекрывается - возникновением на втором входе логического элемента И-НЕ логического 0", и состояние выхода устройсгаа остается неизменным в течение всего времени действия помехи.

Таким образом, устройство защиты от импульсных помех позволяет повысить степень стабилизации временных характе- ристик схемы, расширить ее функциональ» .ные воэможности, что приводит к повышению надежности всей системы автоматического управления технологическими процессами.

Формула изобретения

Устройство защиты от импульсных ноях, содержащее логический элемент

-HE, инвертор, времязадающую цепь, состоящую иэ последовательно соединенных конденсатора и двух резисторов, последний из которых подключен к общей шине, о т л и ч а ю щ е е с я тем, что, с целью повышения эффективности защиты, в него введены цепь защиты верхнего предельного значения логической единицы, цепь защиты нижнего предельного значения логической единицы и дополнительный резистор, причем цепь защиты р нижнего предельного значения логической единицы состоит из последовательно соединенных входного резистора, первого стабилитрона и резистора нагрузки, причем анод стабилитрона соединен с первым входом логического элемента И-НЕ и через дополнительный резистор - с вы» ходом инвертора, вход которого подклкь-; чен к выходу логического элемента И-НЕ, цепь защиты верхнего предельного.зна.® чения логической .единицы содержит второй стабилитрон и транзистор, коллектор которого подключен к второму ,входу логического элемента И-НЕ, вмиттер .- к общей шине, а бава - к общему выводу резисторов времязадающей цепи и аноду второго стабилитроиа, катод которогс соединен с катодом первого стабмлитроиа.

Источники информ &цин1 цринятыв во внимание при экспертизе

1. Патент ФРГ Ж 2415564, кл, Н 03 К 5/153, опублик. 1975.

2.,Патент Японии Ъ 51-36583, кл. Н 03 К S/153, опублик. 1976 (прототип). г.Ужгород, ул. Проектная,4