Устройство декодирования скоррекцией ошибок

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ ())) 794728

Союз Советских

Социалистических

Республик

K АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 23.10.78 (21) 2678541/18-09 с присоединением заявки № (23) Приоритет (43) Опубликовано 07.01.81. Бюллетень № 1 (45) Дата опубликования описания 07.01.81 (51) М Кл з

Н ОЗК 13/34//

//Н 04L 1/10

Государственный комитет

СССР (53) УДК 621.394.14 (088.8) по делам изобретений и открытий (72) Авторы изобретения В. М. Амербаев, P. Г. Бияшев, А. И. Карпухин и P. Н. Нугманов (71) Заявитель (54) УСТРОЙСТВО ДЕКОДИРОВАНИЯ С КОРРЕКЦИЕЙ

ОШИБОК

Изобретение относится к вычислительной технике, может быть использовано в устройствах обнаружения и исправления одиночных и групповых ошибок при контроле хранения и передачи дискретной информации.

Известно устройство декодирования с коррекцией ошибок, содержащее регистр данных, выход которого подключен к входу формирователя контрольных разрядов и 10 первому входу блока сумматоров коррекции, при этом выходы формирователя контрольных разрядов подключены к первым входам сумматоров первой и второй групп контрольных разрядов, ко вторым входам 15 которых подключены соответственно выходы регистров первой и второй групп контрольных разрядов (1).

Однако известное устройство сложно и имеет невысокую точность декодирования. 20

Цель изобретения — повышение точности декодирования и упрощение устройства.

Для этого в устройство декодирования с коррекцией ошибок, содержащее регистр данных, выход которого подключен к входу формирователя контрольных разрядов и первому входу блока сумматоров коррекции, при этом выходы формирователя контрольных разрядов подключены к первым входам сумматоров первой и второй групп 3р контрольных разрядов, ко вторым входам которых подключены соответственно выходы регистров первой и второй групп контрольных разрядов, введены последовательно соединенные дешифратор обратной величины, блок умножения двух величин, дешифратор номера ошибочной позиции и блок вентилей, выход которого подключен ко второму входу блока сумматоров коррекции, при этом ко второму входу блока вентилей подключен выход сумматора первой группы контрольных разрядов, а выход сумматора второй группы контрольных разрядов подключен ко второму входу дешифратора номера ошибочной позиции.

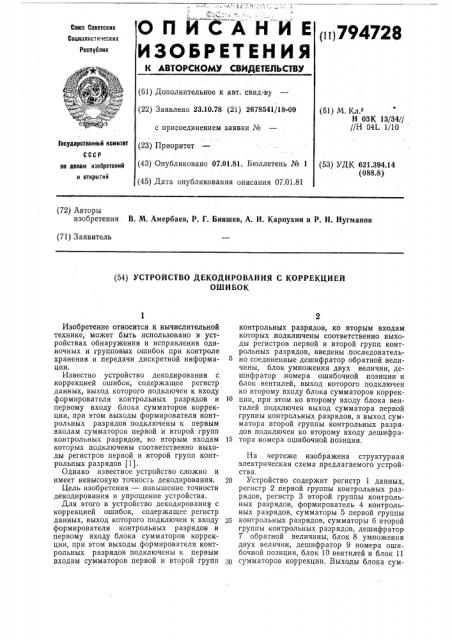

На чертеже изображена структурная электрическая схема предлагаемого устройства.

Устройство содержит регистр 1 данных, регистр 2 первой группы контрольных разрядов, регистр 3 второй группы контрольных разрядов, формирователь 4 контрольных разрядов, сумматоры 5 первой группы контрольных разрядов, сумматоры 6 второй группы контрольных разрядов, дешифратор

7 обратной величины, блок 8 умножения двух величин, дешифратор 9 номера ошибочной позиции, блок 10 вентилей и блок 11 сумматоров коррекции. Выходы блока сум794728

Составитель Н. Пантелеева

Редактор Г. Петрова Техред А. Камышникова

Корректоры: О, Тюрина и 3. Тарасова

Заказ 524/16 Изд. Ме 163 Тираж 1007 Подписное

НПО «Поиск» Государственного комитета СССР по делам изобретений и открытий

113035, Москва, 3(-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2 маторов коррекции являются выходами устройства.

Устройство работает следующим образом.

На входы формирователя 4 поступает и знаков (групп) по m разрядов в каждом с выходов регистра 1, где производится формирование контрольных разрядов, которые затем на сумматорах 5 и 6 суммируются с содержимым регистров 2 и 3. Если в одной из групп регистра 1 произошла любая ошибка, то выходы сумматоров 5 и 6 будут отличны от нуля, причем выходы сумматора 5 будут показывать величину ошибки 6;, а выходы сумматора 6 — произведение ошибки на номер позиции, в которой она произошла, т. е. i б;. На дешифраторе 7 формируется обратная величина ошибки

6;, а на блоке 8 — номер позиции, на которой произошла ошибка. Номер позиции дешифрируется на дешифраторе 9. Сигналы с дешифратор а 9 разрешают величине ошибки с выходов сумматоров 5 посредстВоМ блока 10 суммироваться на блоке 11 с неисправной группой разрядов регистра 1.

Остальные группы разрядов регистра 1 суммируются с нулем на блоке 11.

Введение в устройство дешифратора 7, блока 8, дешифратора 9 и блока 10 позволяет существенно повысить надежность и уменьшить оборудование устройства.

Формула изобретения

Устройство декодирования с коррекцией ошибок, содержащее регистр данных, выход которого подключен к входу формирователя контрольных разрядов и первому входу блока сумматоров коррекции, при этом выходы формирователя контрольных разрядов подключены к первым входам сумматоров

10 первой и второй групп контрольных разрядов, ко вторым входам которых подключены соответственно выходы регистров первой и второй групп контрольных разрядов, о тличающееся тем, что, с целью повыше15 ния точности декодирования и упрощения устройства, введены последовательно соединенные дешифратор обратной величины, блок умножения двух величин, дешифратор номера ошибочной позиции и блок вен20 тилей, выход которого подключен ко второму входу блока сумматоров коррекции, при этом ко второму входу блока вентилей подключен выход сумматора первой группы контрольных разрядов, а выход сумматора

25 второй группы контрольных разрядов подключен ко второму входу дешифратора номера ошибочной позиции.

Источники информации, принятые во внимание при экспертизе

30 1, Францис Т. А., Янбых Г, Ф. Избыточность в электронных устройствах, Л., «Энергия», 1969, с. 227 — 235.