Устройство для временнойкоммутации каналов

Иллюстрации

Показать всеРеферат

<» 794750

СПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (61) Дополнительное к авт. свнд-ву— (22) Заявлено 05.01.79 (21) 2710889/18-09 с присоединением заявки ¹â€” (23) Приоритет— (51) М Кл з

Н 04 1 3/00

Н 04 Я 3/52

Государственный комитет (43) Опубликовано 07.01.81. Бюллетень № 1 (53) УДК 621.395.345 (088.8) и открытий (45) Дата опубликования 07.01.81 (72) Автор изобретения

В. А. Авдеев

Таганрогский радиотехнический институт им. В. Д. Калмыкова (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ВРЕМЕННОЙ

КОММУТАЦИИ КАНАЛОВ

Изобретение относится к технике связи, может использоваться в вычислительных системах с перестраиваемой структурой, а также в электронных автоматизированных телефонных станциях.

1 1звестно устройство для временной коммутации каналов, содержащее блок сопряжения, первый выход которого подключен к первому входу блока управления, второй выход блока сопряжения подключен к информационным входам блоков памяти, информационные выходы которых подключены к первому входу блока сопряжения, первый выход блока управления подключен к второму входу блока сопряжения, второй выход блока управления подключен к управляющим входам блоков памяти, адресные входы которых соединены с выходами соответствующих счетчиков адреса, другие выходы одного блока памяти подключены к первым входам блока элементов И, а также блок стробирования, выход которого подключен к второму входу блока элементов И (1).

Недостатком известного устройства является низкое быстродействие.

Шаг обмена информацией (время цик. ла установления полного числа соединеи ний) известного устройства Т=- ();r) ат, r=l (где т — время выполнения одного такта, п — число входов илн выходов устройства) н число блоков памяти v=11 .

Цель изобретения — повышение быст5 родействня.

Для этого в устройство, содержащее блок сопряжения, первый выход которого подключен к первому входу блока управления, второй выход блока сопряжения

10 подключен к информационным входам блоков памяти, информационные выходы которых подключены к первому входу блока сопряжения, первый выход блока управления подключен к второму входу блока

15 сопряжения, второй выход блока управления подключен и управляющим входам блоков памяти, адресные входы которых соединены с выходамн соответствующих счетчиков адреса, другие выходы одного

20 блока памяти подключены и первым входам блока элементов 1Л, а также блок стробнрования, выход которого подключен к второму входу блока элементов. И, введены регистры адреса, регистры конечного

25 адреса, блок сравнения, дешнфраторы и дополнительные блоки элементов И, при этом третий выход блока сопря>кения подключен к входам рагистров адреса, выходы которых подключены к первым входам со30 ответствующих счетчиков адреса, вторые

794750 входы счетчиков адреса соединены с третьими выходами блока управления, чстверTbIH BbIxogl блока сопряжения подK:»o oH K входам регистров конечного адреса, выходы которых через блок сравнения подключены к второму входу блока управления, выходы счетчиков адреса подключены к другим входам блока сравнения и и входам соответствующих дешифраторов, выходы которых подключены к входам блока стробирования, выходы блока элементов 11 подключены к последовательно соединенным дополнительным блокам элементов И, при этом другие выходbI остальных блоков памяти подключены к вторым входам соответствующих дополнительных блоков элементов И, третьи входы которых соединены с. выходом блока стробирования.

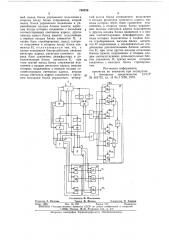

На чертеже представлена структурная электрическая схема устройства для временной коммутации каналов для случая р-2.

Устройство содержит блок 1 сопряжения с интерфейсными шинами 2, регистры 3 и 4 конечного адреса, регистры 5 и 6 адреса, блоки 7 и 8 памяти, счетчики 9 и 10 адреса, дешифраторы 11 и 12, блок 13 сравнения, блок 14 управления, блок И 15 элементов, дополнительный блок И 16 элементов, выходы 17i — 17 „ которого являются информационными выходами устройства, блок 18 стробирования, входы 19» — 19,, которого являются информационными входами устройства. В состав блока 18 входят элементы

И 20ii — 20„, и элементы ИЛИ 21. Ьлоки И 15 и И 16 содержат элементы

И 22i — 22„.

Устройство работает следующим образом.

По шинам 2 через блок 1 осуществляется ввод программы коммутации в блоки

7 и 8. При построении двухадресного (р-2) устройства временной коммутации все множество входов блока 18, число

ll которых равно и, разбивается íà n> — — — „ подмножеств. Внутри каждого подмножества мощности п, каждый вход с помощью элемента И стробируется сигналом с выхода дешифратора 11, т. е. разрешается одновременная передача данных сначала входов 19», 19иь...191п,(19ii — 191, ), затем передача данных входов 19„.„19 2, ...

192„(19 1 — 192„, ) и т. д. Кроме того, входы каждого подмножества моц;ности п1 стробируются с помощью элементов И сигналами с выходов дешифратора 12 так, что разрешается одновременная передача информации входов 19» — 19„1, затем входов 1912 — 19,р и т. д. Прйчем длитель. ность каждого распределенного во времени и в пространстве сигнала с выхода дешифратора 12 включает в себя длительности п1 сигналов дешифратора 11. Та4 кнм образом, момент времени появления информации на входе устройства определяется импульсом с выхода дешнфратора 11 II потенциалом с выхода дешифратора 12. Формирование соответствующих сигналов дешифраторов 11 и 12 выполняется с помощью счетчиков 9 и 10. На суммирующий вход счетчика 9 из блока 14 поступает тактовая серия импульсов с часI10 тотой f i — — —, а на сумм ируюгцпй вход

Й счетчика 10 с частотой / = — . В соответП1

И ствии с этими частотами формируется и частота обращения к блокам " и 8. Таким образом, частота появления информации на входах 19» — 19„,, (выходах элементов

И 201 — 20,„,) устройства синхронизирована с частотой считывания информации

II3 блоков 7 и 8. Каждая L-я ni-разрядная и и>-разрядная ячейки памяти блоков 7и

8 соответствуют выходу 171устройства. Так как момент времени появления информации

25 на каком-либо входе устройства известен (он определяется сигналами дешнфраторов

II и 12), то, записывая логическую единицу в соответствующие позиции п1-разрядной и п2-разрядной 1-ых ячеек памяти, задаем

30 программу соединения i-ro выхода с требуемым входом, т. е. в момент времени появления информации на входе будут открыты элементы И 22; блоков И 15 и

И 16, и информация через элементы

35 ИЛИ 21 поступит íà i-й выход устройства.

Таким образом, повышение быстродействия данного устройства осуществляется за счет непосредственного управления сое динением его входов и выходов через бло40 ки логических элементов информацией, хранящейся в блоках памяти, и организации соединения только тех входов с выходами устройства, которые участьуют в передаче информации.

Так как число адресов находится в пределах 1 5 р (pff = I „n (рр — оптимальное число адресов), то и число элементов памяти р-адресного устройства временной коммутации изменяется в соответствующих

50 1+—

1 пределах Vi=n ) )Vn — — рп ") Vn. — 1„(„п.

При р-Г число элементов памяти р-адресного устройства временной коммутации равно числу элементов известного одноадресного коммутационного устройства.

Формула изобретения

Устройство для временной коммутации каналов, содержащее блок сопряжения, 60 первый выход которого подключен к первому входу блока управления, второй выход блока сопряжения подключен к информационным входам блоков памяти, информационные выходы которых подключе65 ны к первому входу блока сопряжения пер794750

Составитель Н. Пантелеева

Техред И. Пенчко

Редактор Г. Петрова корректор О. Тюрина

Заказ 1066 Изд. № 100 Тираж 712 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

I !3035, Москва, Ж-35, Раушская наб., д. 4/5

Загорская типография Упрполиграфнздата Мособлпсполкома

5 вый выход блока управления подключен к второму входу блока сопряжения, второй выход блока управления подключен к управляющим входам блоков памяти, адресные входы которых соединены с выходами соответствующих счетчиков адреса, другие выходы одного блока памяти подключены к первым входам блока элементов И, а также блок стробирования, выход которого подключен к второму входу блока элементов И, отличающееся тем, что, с целью повышения быстродействия, введены регистры адреса, регистры конечного адреса, блок сравнения, дешифраторы и дополнительные блоки элементов И, при этом третий выход блока сопряжения подключен к входам регистров адреса, выходы которых подключены к первым входам соответствующих счетчиков адреса, вторые входы счетчиков адреса соединены с третьими выходами блока управления, четвер6 тый выход блока сопряжения подключен к входам регистров конечного адреса, выходы которых через блок сравнения подключены к второму входу блока управления, выходы счетчиков адреса подключены к другим входам блока сравнения и к входам соответствующих дешифраторов, выходы которых подключены к входам блока стробирования, выходы блока элемен1р тов И подключены к последовательно соединенным дополнительным блокам элементов И, при этом другие выходы остальных блоков памяти подключены к вторым входам соответствующих дополнительных бло15 ков элементов И, третьи входы которых соединены с выходом блока стробирован ия.

Источники информации, принятые во внимание при эксперТпзе

1. Авторское свидетельство СССР

Мв 563732, кл. Н 04 J 3/00, 1975.