Устройство цикловой синхронизации

Иллюстрации

Показать всеРеферат

"зев ею

1ФЛ jfgqgg, теор; у

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свнд-ву 566379 (22), аявлено 08.08.77 (21) 2515635/!8-09 с присоединением заявки Ме— (23) Приоритет— (43) Опубликовано 07,01.81. Бюллетень М 1 (45) Дата опубликования описания 07.01.81 (51) Ч К з

Н 04 L 7/04

Гасударственный комитет (53) УДЫ 621.394.662 (088.8) па делам изобретений н открытий

А. В. Беланович, А. А. Пыжов, В. С. Пуденков и

К. И. Василевский (72) Авторы изобретения (7l ) Заявитель (54) УСТРОЙСТВО ЦИКЛОВОЙ

СИНХРОНИЗАЦИИ

Изобретенис относится к технике связи, может использоваться в системах передачи данных.

По основному авт. св. М 566379 известно устройство цикловой синхронизации, содержащее последовательно соединенные ключ, к первому входу которого подключен первый вход блока сравнения, ко второму входу ключа — первый выход регистра сдвига и третьему входу ключа — выход счетчика числа совпадений, к четвертому входу ключа — выход псрвого элемента И, регистр сдвига, дешифратор и первый элемент И, ко второму входу которого подключсн выход триггера, к первому входу которого подключен выход первого элемента И, а ко второму входу триггера через счетчик числа совпадений выход блока сравнения, ко второму входу которого подключен первый выход регистра сдвига, а также второй элемент И, декодср и блок памяти состояния декодера, при этом выход декодера подключен через блок памяти состояния декодера к первому входу второго элемента И, ко второму входу которого подключен выход первого элемента И, а вход декодера подключен к первому входу блока сравнения fl).

Однако данное устройство имеет невысокую точность цикловой синхронизации.

Цель изобретения — повышение точности цикловой синхронизации.

Для этого в устройство цикловой синхронизации, содержащее последовательно соединенные ключ, к первому входу которого подключен первьш вход блока сравнения. ко второму входу ключа — первый выход регистра сдвига, к третьему входу ключа — выход счетчика числа совпадений, к четвертому входу ключа — выход первого элемента И, регистр сдвига, дешифратор и первый элемент И, ко второму входу которого подключен выход триггера, к первому входу которого подключен выход первого элемента И, а ко второму входу триггера подключен через счетчик числа совпадений выход блока сравнения, ко второму входу которого подключен первый выход регистра сдвига, а так2п же второй элемент И, декодер и блок памяти состояния декодера, при этом выход декодера подключен через блок памяти состояния декодера к первому входу второ о элемента И, ко второму входу которого подключен выход первого элемента 11, а вход декодсра подключен к первому входу блока сравнения, введены последователь. но соединенные элемент задержки, элемент ИЛИ, дополнительный триггер и дояп полннтсльный элемент И, при этом к дру794757

60 гому входу трппсра подключен гы.,од декодера, а к другим входам элемента задержки и дополнительного элемента И подкгпочсн выход второго элемента И, причем на другой вход элемента ИЛИ подан сигнал «начальная установка> .

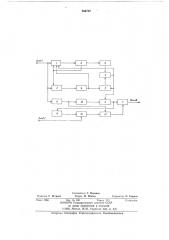

На чертеже изображена структурная электрическая схема предложенного усгройства.

Устройство цикловой синхронизации содержит ключ 1, блок 2 сравнения, рсгистр 3 сдвига, счетчик 4 числа совпадений, элементы И 5 — 7, дешифратор 8, триггеры 9 и 10, декодер 11, блок 12 памяти, элемент 13 задержки и элемент ИЛИ 14.

Предложенное устройство работаст следующим образом.

Информация, принимаемая из канала связи, поступает на блок 2 и через ключ 1 на регистр 3. Количество поразрядных совпадений эталонной и принимаемой комбинации подсчитывается счетчиком 4.

В случае неудовлетворения хотя бы одной проверки счетчик 4 автоматически сбрасывается до нуля, и анализ начинается сначала. При наличии подряд K-кратного совпадения счетчик 4 переводиг регистр 3 через ключ 1 на автономную работу замыкания обратную связь регистра 3 и одновременно отключается поступление входной информационной последователь. ности на регистр 3.

Выдсленис фазирующего сигнала дсшифратором 8 происходит при формировании па регистре 3 комбинации оконча ния фазового пуска, Фазирующий сигнал с дешифратора 8 через элемент И 5 при наличии сигнала с триггера 9, который взводится счетчиком 4, поступаст на ключ 1, размыкая обратную связь регистра 3 и подключая на вход регистра 3 входную информацию, а также сбрасывает триггер 9 в исходное состояние. Фазнрующий сигнал с выхода элемента И 5 поступает на вход элемента И 6.

Информация с входа устройства поступает также на декодер 11. Так как при передаче информ а ции синхронизирующа я последовательность не кодируется, то па приеме декодер 11 при выделении истинной синхронизирующей последовательностити всегда выдает сигнал с неправильно принятой кодовой комбинации, который через блок 12 выдаст разрешение элементу И 6 на прохождение фазирующего сигнала на вход элемента И 7. Если фазирующая последовательность была выделена из информационной, то на выходе декодера 11 выделится сигнал правильно принятой кодовой комбинации (прохождение по коду, так как на передаче кодовые комбинации кодируются), который через

>0

4 блок 12 запрсщаст элементу И 6 npo>;oжденис выделенного фазирующсго сигнала, чем исключает сс выделение из передаваемой информации.

При наличии высокого уровня помех в канале связи значительное количество информационных кодовых комбинаций будет иска>кено и воспримется декодером 11 как неправильно принятые кодовые комбинации, вследствие чего блок 12 будет выдавать сигнал разрешения элементу И 6 с каждой искаженно принятой кодовой комбинацией для прохождения ложного фазирующего сигнала на вход элемента И 7.

Триггер 10 запрещает прохождение ложного фазирующего сигнала через элемент И 7 при наличии хотя бы одной правильно принятой кодовой комбинации (что свидетельствует о наличии синхронизации по циклам между приемным и передающим устройствами) .

Начальная установка триггера 10 осу. ществляется через элемент ИЛИ 14, фазирующий сигнал проходит через элемент

И 7 на выход устройства, так кaê с триггера 10 поступает сигнал разрешения. После вхождения в синхронизм триггер 10 следит за состоянием декодера 11, сели принимается неискаженная информационная кодовая комбинация, то сигнал с декодера 11 устанавливает триггер 10 в такое состояние, при котором запрещается прохождение фазирующего сигнала через элемент И 7, При использовании предложенного устройства значительно уменьшается вероятность ложного фазирования. В результате повышается точность цикловой синхронизации за счет устрансния сбоев от случайного выделения синхронизирующей последовательности из информационной.

Формула изобретения

Устройство цикловой синхронизации по а вт. св. ¹ 566379, о т л и ч а ю щ е е с я тем, что, с целью повышения точности цикловой синхронизации, введены последовательно соединенные элемент задержки, элемент

ИЛИ, дополнительный триггер и дополнительный элеме IT И, при этом к другому входу триггера подключен выход декодера, а к другим входам элемента задержки и дополнительного элемента И подключен выход второго элемента И, причем на дру гой вход элемента ИЛИ подан сигнал «начальная установка».

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 566379, кл, Н 041 7/04, 1975.

794757

Составитель Т. Маркина

Техред И. Пенчко

Корректор О. Т>орина

Рсдактор Г. Петрова

Заказ 1066

Изд. ¹ 100 Тираж 712

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Подписное

Загорская типография Упрполиграфиздата Мособлисполкома