Устройство для записи и контроляпрограммируемых блоковпостоянной памяти

Иллюстрации

Показать всеРеферат

®й вттю 4Ок и >тФв>е>еепеев

Фп4(еттат М

Союз Советснмк

Социвлнстнческнк

Республик

О П И С А Н И Е 796909

ИЗОБРЕТ ЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (6I ) Дополнительное к авт. свил-ву (22) Заявлено 20.01.78 (21) 2572327/18-24 (51 ) М. Кл.

6-11 С 7/ОО

6 11 С 29/ОО с присоединение>и заявки ¹

Гвсударстеанный ко>кнтет (23) Приоритет по дела>к изобретений н открытий

Опубликовано 15.01.81. Бюллетень ¹ 2

Дата опубликования описания 18. 01.81 (53 ) УД К 681. 327 (OBB.B) Н, Н. Данилин, Ю. H. Дьяков, Л. М. Попель, В. g. Пашкова, Л. Н. Скворцова и О. Н. Шаромет (72) Авторы изобретения (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ЗАПИСИ И КОНТРОЛЯ

ПРОГРАММИРУЕМЫХ БЛОКОВ ПОСТОЯННОЙ

ПАМЯТИ

Изобретение относится к запоминающим устройствам.

Известно устройство для записи и контроля программируемых блоков постоянной памяти, содержащее регистры, за5 дающий генератор, формирователи сигналов и схему сравнения $1)

Недостатком этого устройства является невысокое быстродействие.

Наиболее близким к изобретению по своему решению является устройство для записи и контроля программируемых блоков постоянной памяти, содержащее регистр текущего адреса и регистр данных, одни из входов которых подключены к вы->5 ходам задающего генератора и блока оперативной памяти, а выходы — соответст венно к первым вход»л> Формирователя адресных сигналов н форл>ирователя сигналов ланных, компаратор конечного алреса, вхо- 2О лы которого соединены с выходами регистра конечного а»реса и регистра текущего аЛреса, компаратор ныхолных данных, один из входов кот<>рого подключен ко входу устройства, а другие входы соедине»нь> с выходами регистра данных и блока оперативной памяти, один из входов ко>орого подключен к выходу счетчика, и блок управления 2

Недос1атком этого устройства является отсутствие универсальности при работе с разнотипными программными блоками памяти, что сужает область применения устройства.

Бель изобретения — расширение области применения устройства за счет обеспечения возможности записи и конт» роля равнотипных блоков памяти.

Поставленная пель достигается тем, что устройство содержит блок аналоговой памяти, ключи, цифроаналоговый преобразователь, дешифратор, дополнительные блок оперативной памяти и счетчик, формирователь синхросигналов и блок программируемых синхросигналов, причем входы блока аналоговой памяти соелин< ны с выходами ключей, выходы — oo»т< рыми входами формирователя алрт <:ных

3 79 сигналов и формирователя сигналов данных и первым входом формирователя синхросигналов, второй вход которого подключен к выходу блока программируемых синхроимпульсов и другим входам регистра текущего адреса и регистра данных, а выход — к одному иа выходов устройства, выходы дешифратора и цифроаналогового преобрааователя соединены со входами ключей, а входы — соответственно с выходами дополнительного счетчика и дополнительного блока оперативной памяти, первый вход которого подключен к выходу дополнительного счетчика, выход блока управления соединен со входом дополнительного счетчика, вторым входом дополнительного блока оперативной памяти и одним из входов блока программируемых синхроимпульсов, другой вход которого подключен к выходу аадающего генератора..

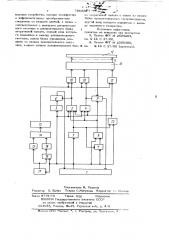

На чертеже изображена блок-схема предложенного устройства.

Устройство содержит блок 1 управления, регистр 2 текущего адреса, регистр

3 конечного адреса, регистр 4 данных, задающий генератор 5, блок 6 оператив- ной памяти, счетчик 7, компаратор 8 конечного адреса, компаратор 9 данных, Входы и выходы устройства подключают ся к выходам и входам индивидуального модуля 10, который через контакты 11 соединяется с программируемым блоком

12 постоянной памяти.

Устройство также содержит блок 13 аналоговой памяти, ключи 14, дешифратор 15, дополнительные блок 16 оперативной памяти и счетчик 17, цифроаналоговый преобразователь 18, формирователь 19 адресных сигналов, формирователь 20 сигналов данных, формирователь

21 синхросигналов, блок 22 программируемых синхросигналов, Выходы регистров 2 и 4 подключены к первым входам формирователей 19 и

20 соответственно. Сдин из входов блока 6 соединен с выходом счетчика

7, Входы блока 13 соединены с выхода.ми ключей 14, а выходы - со вторыми входами формирователей 19 и 20 и первым входом формирователя 21, второй вход которого подключен к выходу блока

22 и другим входам регистров 2 и 4, а выход — к одному из выходов устройства.

Выходы дешифратора 15 и преобразователя 18 соединены со входами ключей 14, а входы - соответственно с выходами счетчика 17. Выход блока 1 соединен со вх щом счетчика 17, вторым входом бло ка 16 и одним иа входов блока 22, другой вход которого подключен к выходу аадающего генератора 5.

Устройство работает следующим обрааом.

K модулю 10 через контакты 11 подключается программируемый блок 12 пос-тоянной памяти.

Иа блока 2 в соответствии с програм1в мой входного контроля необходимая информация заносится в блок 16 дпя аадания величины верхних и нижних границ импульсов формирователей 19, регистров

3 и 4 с целью определения начала и. конца контроля, в блок 22 для выбора номера канала, задержки и длительности импульсов синхронизации, в задающий генератор 5.

По команде иа блока 1 в соответстро вии с .временной диаграммой работы блока 12-блок 22 программируемых синхроимпупьсов вьщает сигналы на индивидуальный модуль 10, на регистры 2 и 4. По первоначальному адресу, запи2з санному в регистре 2, информация считывается из блока 12 на компаратор 9, где идет сравнение с содержимым регистра

4. Положительный результат сравнения позволяет добавить единицу в регистр

Зп 2 с периодом, определяемым задающим генератором 5. Отрицательный результат сравнения поступает в блок 1 и запрещает добавление единицы в регистр 2. При сравнении содержимого регистра 2 с содержимым регистра 3 в блок 1 проходит команда "Годен", Формирование величин верхних и ниж них границ импульсов формирователей 1921 происходит автономно после ааписи в блок 16 последнего слова, Счетчик 17 тактируется собственным внутренним генератором. Каждое состояние счетчика 17 расшифровывается дешифратором 15 в поаиционный код и вызывает считывание соответствующего слова в виде двоичного кода из блока 16.

Йвоичный код каждого слова из блока

16 преобразуется цифроаналоговым пре-. обрааователем 18 в аналоговый сигнал.

Этот сигнал через открытый соответст вующим позиционным кодом дешифратора

15 ключ 14 поступает и запоминается в блоке 13. С выходов блока 13 соо1 ветствующие сигналы напряжения постуМ пают на формирователи 19-21. Эгими напряжениями подготавливаются к работе формирователи 10-21.

После подготовки формирователей 1921 с регистра 2 на формирователь 19

Д 7969 последовательно поступают коды адресов ячеек программируемого блока 12. Они, нреобразовываясь формирователем 19 адреса в необходимую форму, поступают на адресные входы блока 12. С кодом каждого адреса блока 12 выдается управляющий сигнал блоком 22. Этот сигнал чераз формирователь 21 также поступает на соответствующие входы блока 12.

По каждому адресу происходит считыва- N ние информации выбранной ячейки блока 12 и сравнение этой информации с первоначально записанной в регистре 4 компаратором 9. Так продолжается д тех пор, пока код регистра 2 не сравнится с кодом регистра 3 компаратором 8.

Компаратор 8 выдает в блок 1 соответст вующий сигнал. Иикп входного контроля работоспособности блока 12 заканчивает.ся. После проведения входного функцио 2о нального контроля выполняется программирование в соответствии с таблицей истинности, занесенной в блок 1. С этой целью после занесения требуемой информации и подготовки к работе формирова - М телей 19=-21 аналогично описанному выше с регистра 4 на формирователь 20 синхронно с каждым адресом поступает информация, в соответствии с которой происхсдит электрическое программирование ЗО блока 12.

Отличия режима программирования от режима входного контроля следующие.

Добавление единицы в регистр 2 проводится по команде из блока 1, а не из задающего генератора 5.

Один из каналов синхронизации выбирается дпя организации паузы после прог раммирования, в режиме, программирования в течение паузы проводится контроль М правильности программирования в зависи- мости от типа блока 12 после каждого бита или всего слова.

Задающий генератор 3 необходим только для организации синхроимпупьсов и паузы в блоке 22.

Устройство для записи и контроля программируемых блоков постоянной памяти, содержащее регистр текущего ад-. реса и регистр данных, одни из входов которых подключены к выходам задающего генератора и блока оперативной памяти, а выходы — соответственно к первым выходам формирователя адресных сигналов и формирователя сигнаповданны:,-, компаратор конечного. адреса, входы ко арог о соединены с выходами регистра конечного адреса и регистра текущего адреса, комнаратор данных, один из вхс=дов которого подключен ко входу устройства, а другие входы соединены с выходами регистра данных и блока оперативной памяти, один из входов которого подключен к выходу счетчика, и блок управления, о т л и ч а ю щ е е с я тем, что, с целью расширения области применения устройства за счет обеспечения возможности записи и контроля разнотипных блоков памяти, оно содержит блок анайоговой памяти, ключи, цифроаналоговый преобразователь, дешифратор, дополнительные блок оператйвной памяти и счетчик, формирователь синхросигналов и блок программируемых синхросигналов, причем входы блока аналоговой памяти соединены с выходами ключей, а выходы со вторыми входами формирователя адресных сигналов и формирователя сигналов данных и первым входом формирователя синхросигналов, второй вход которого подключен к выходу блока програм-= мируемых синхроимпульсов и другим входам регистра текущего адреса и регистуа данных, а выход — к одному из

Режим программирования выполняется как и в нервом случае до тех пор, пока код регистра 2 не станет равным коду регистра 3.

После окончания режима программирования проводится режим выходного функционального контроля. Отличие режима выходного контроля от входного состоит

55 в том, что ожидаемая информация для сравнения нри считывании из блока 12 на комнаратор 9 поступает из блока 6, в который предварительно была занесена

09 6 из блока 1, добавление единицы" в счет чик 7 и регистр 2 идет синхронно по сигналу из генератора 5 с частотой предельной для конкретного типа блока 12, если объем памяти блока 6 меньше объе, ма памяти блока 12, то режим выходного функционального контроля повторяется несколько раз, при этом последовательно увеличивается содержимое регистра 2.

Окончание выходного функционального контроля проводится так же по содержимому регистра 3.

Описанное устройство является более универсальным по сравнению с известнь -» ми, а также отличается повышенной надежностью и точностью работы.

Ф ормула и зобретения

В»» с„>

7969бУ . " .,» ». ...,, 8 .Ф. выходов устройства, выходы иешифратора ка оперативной»1аМяти и одним и;» входов и цифроаналог ового преобразователя блока программ ируемы х сии хроичпульсов, соединены со входами ключей, а входы — другой вход которого подключен к выхосоответственно с выходами дополнител»» ду задающего генератора. ного счетчика и дополнительного блока Источники информации, оперативной памяти, первый вход которо- принятые во внимание при экспертизе го подключен к выходу дополнительного 1, Патент ФРГ hb 2505285, счетчика, выход блока управления сое- кл. Я 11 С 17/00. динен со входом дополнительного счет- 2. Патент ФРГ М; 2505300, чика, вторым входом дополнительного бло-10 кл. 6- 11 С 17/00 (прототип).

Составитель B. Рудаков

Редактор П. Бабич Texpeg С.Мигунова Корректор (:. П!ек»»ар

Заказ 9779/70 Тираж 656 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д, 4/5

Филиал ППП "Патент, г. Ужгород, ул, Про кт»»»s», 4