Устройство для контроля блокапамяти

Иллюстрации

Показать всеРеферат

сф с о-; к я " y о и .м-":е А н к е

Союз Советских

Социалистических

Республик

< 796916

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. саид-ву (22) Заявлено. 15.02.7g (21) 2726641/18-2 (51)М. Кл.

Q 11 С 29/00 с присоединением заявки М (23)Приоритет

Гооударстееннмй комитет

СССР (53 ) УД К 68 1. 327 (088;8) ио делам изобретений и открытий

Опубликовано 15.01.81 .Бюллетень Ж 2

Дата опубликования описания 18. 01.81

Л. В. Дербунович, Г. И. Белов, А. И. Кордюмов, И. Е. Фролова и A. И. Овчаренко (72) Авторы изобретения

Харьковский ордена Ленина политехнический институт им. В. И, Ленина (7! ) Заявитель (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ БЛОКА ПАМЯТИ

Изобретение относится к запоминающим устройствам.

Известно устройство для контроля блока памяти, которое содержит счетчик, схему индикации, схемы связи по количеству адресных формирователей запомина» ющего блока, регистр сдвига Pl).

Указанное устройство не формирует сигнал неисправности в случаях, если возбуждается один, но не выбранный адресный формирователь, или возбуждаются пять, девять и т.д. адресных формирователей.

Наиболее близким к предлагаемому является устройство, содержащее два счетчика, триггер, коммутатор, регистр сдвига и схему сравнения, подключенные к блоку управления P2).

Недостаток етого устройства - низкая достоверность контроля вследствие того, что не формируется сигнал неисправности в случаях, если возбуждается один, Но не выбранный адресный формирователь, или возбуждается пять, девять и т.д. ад2 ресных формирователей. Кроме того, уст ройство не позволяет провести локализацию неисправностей.

Бель изобретения — повышение достоверности контроля и быстродействия устройства и обеспечение диагностики неисправностей.

Поставленная цель достигается тем, что в устройство для контроля бпока памяти, содержащее блок управления, счел

10 чик, триггер, регистр сдвига и схему сравнения, причем одни иэ входов регистра сдвига являются информационными входами устройства, другие входы подключены соответственно к первому и вторсииу выходам блока управления, выход регистра сдвига соединен с одним из входов схемы сравнения, один из выходов и первый вход счетчика подключены соответст

1 венно к первому входу и второму выходу блока управления, введены регистр, элемент И, блок индикации, элемент задержки и две группы элементов И, причем другие входы схемы сравнения подключены

796916

И 14. Вход элемента 11 задержки подключен к первому выходу блока 12, а выход — ко второму входу счетчика 5.

Выходы элементов И 8, 10 н 14 соединены со входами блока 4 индикации, а входы регистра 7 — с шинами 6.

Устройство работает следующим образом.

В момент обращения к блоку памяти (на чертеже не приведен) по некоторому адресу с каждого адресного формирователя 2 через элемент 1 связи сннмает ся сигнал, указывающий состояние формирователя — включен он нлн .выключен.

Эти сигналы одновременно подаются на входы регистра 3 сдвига. Прн этом прн2 ннмается, что включенный формирователь

2 записывает 1 в регистр 3 сдвига, а невключенный — 0". В зависимости от технического состояния блока памяти (исправен он нлн ненсправен) в регистре

Зц 3 сдвига могут быть записаны одна единица, положение которой определяется двоичным адресом регистра 7, одна единица, положение которой не соответствует двоичному адресу регистра 7, божее одной еднннпы нли все нуля.

Первое состояние соответствует нсправной работе блока. памяти, остальные состояния - неисправной работе. Йля определения действительного состояния блока памяти в регистр 7 по шинам 6 записывается ...двоичный код адреса н на шину 15 сннхроннзапин блока 12 управ= лення поступает сигнал разрешении проверки. Блок 12 управления устанавлнвает в начальное состояние триггер 13, счетчик 5, регистр 3 сдвига. Затем с блока 12 управления поступает тактовая частота на регистр 3 сдвига н через элемент 11 задержкн на счетчик 5. Информация нз регистра 3 с тактовой частотоя поступает на вход схемы 9 сравнения. Прн поступлении елнннчного снс нала нз регнстра 3 сдвига на тактовый вход-схемы 9 сравнения происходит сравнение двоичного кода адреса, подаваемого из регистра 7, и двоичного кода включенного адресного формирователя 2 нз счетчнка 5. Прн несовпаленнн колов схема 9 сравнения вырабатывает единичный соответственно к выходам регистра, другнм выходам счетчика и первым входам элементов И групп, выходы элемента И н схемы сравнения соединены соответственно со вторыми входами элементов И первой н второй групп, входы триггера подключены соответственно к выходу регистра сдвига и второму выходу блока управления, входы элемента И соединены с од. ннм нз выходов счетчика н выходом триггера, выход схемы сравнения подключен ко второму входу блока. управления, третий вход которого соединен с выходом элемента И, вход элемента задержки подключен к первому выходу блока управления, а выход - ко второму входу счетчика, выходы элементов И соединены со входами блока индикации, а входы регистра являются адресными входами устройства.

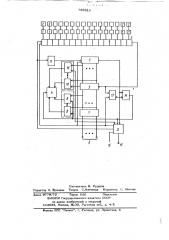

На чертеже представлена структурная схема устройства для контроля блока памяти.

Устройство через элементы 1 связн подключается к соответствующим адресным формирователям 2 контролируемого блока памяти. Устройство содержит регистр 3 сдвига, блок 4 индикации, счетчик 5, предназначенный для определения двоичного адреса включенного адресного формирователя 2 и формирования сигнала окончания цикла проверки, адресные шины 6, являющиеся адреснымн входами устройства, регистр 7, первую группу элементов И 8, схему.9 сравнения, вт рую группу элементов И 10, элемент 11 задержки,блок 12 управлення, триггер

13, который предназначен для образования сигнала невключения адресных формирователей 2, элемент И 14, шину 15 сннхроннзапин, шину 16 результата проверки. Счетчик 5 должен иметь К разрядов, где v — число ячеек контролируемой памятн.

Одни пз входов регнстра 3 являются информационными входами устройства, другие входы подключены соответственно к первому н второму выходам блока 12.

Выход:регнстра 3 соединен с одним нз входов схемы 9 сравнения. Chas нз выходов н первый вход счетчика 5 подключены соответственно к первому входу к второму выходу блока 12. другие входы схемы 9 сравнении подключены соответ ственно к выходам регистра 7, другим выходам счетчика 5, первым входам элементов И 8 н 10. Выходы элемента И 14 и схемы 9 сравнения соединены соответственно со вторымн входами элемен4 тов И 8 и 10. Входы триггера 13 подключены соответственно к выходу регистра

3 и второму выходу блока 12. Входы элемента И 14 соединены с одним нз выходов счетчика 5 н выходом триггера 13.

Выход схемы 9 сравнения подключен ко второму выходу блока 12, третий вход которого соединен с выходом элемента

Таким образом, описанное устройство для контроля блока памяти обнаруживает и локализует одиночные и кратные неисп равности схем управления блока памяти, 4 что позволяет повысить достоверность контроля и сократить время поиска неисправного элемента.

5 7969 сигнал неисправности, который поступает на блок 12 управления и элементы И 10.

Двоичный адрес включенного адресного формирователя 2 поступает череа элементы И 10 на блок 4 индикации и тем самым осуществляется локализация неправильно включенных адресных формиро вателей 2.

Если и регистре 3 сдвига записаны только нули, то триггер 13 останется в tO нулевом состоянии, и после окончания цикла проверки счетчик 5 вырабатывает импульс переполнения, который поступает на блок 12 управления и элемент

И 14. Сигнал отсутствия включенного 1д адресного формирователя 2 поступает череа элемент И 14 на элементы И 8 и на блок 4 индикации. Двоичный код иа регистра 7 череа элементы И 8 поступает на блок 4 индикации и тем самым проводится локализация невключенного адресного формирователя 2.

Наличие блока 12 управления позво- ляет вести проверку с тактовой частотой, определяемой лишь элементной баной 2S устройства контроля, и тем самым позволяет сократить время цикла проверки.

Кроме того, блок 12 управления при наличии сигнала неисправности вырабатывает сигнал повторения цикла проверки, чп тем самым исключая сигнал неисправности, обусловленный сбоем устройства контроля или блока памяти. После окончания второго цикла проверки блок 12 управления вырабатывает на шине 16 сигнал «разрешения записи следующего адреса в регистр 7 (при исправной работе) или вырабатывает сигнал прерывания проверки (при повторном обнаружении неисправности) . 40

16 6

Формула и зобрете ни я

Устройство для контроля блока памяти, содержащее блок управления, счетчик, триггер, регистр сдвига и схему сравнения, причем одни из входов регистра сдвига являются информационными входами устройства, другие входы подключе« ны соответственно к первому и второму выходам блока управления, выход регис« ра сдвига соединен с одним из входов схемы сравнения, один из выходов и первый вход счетчика подключены соответственно к первому входу и второму выходу блока управления, о т л и ч а.— ю щ е е с я тем, что, с целью повышения достоверности контроля и быстродействия устройства оно содержит регистр, элемент И, блок индикации, элемент аадержки и две группы элементов И, причем другие входы схемы сравнения подключены соответственно к выходам регистра, другим выходам счетчика и первым входам элементов И групп . вы/. ходы элемента И и схемы сравнения соединены соответственно со вторыми входами элементов И первой и второй. групп, входы триггера подключены соответственно к выходу регистра сдвига и второму выходу блока управления, входы элемента И соединены с одним иа выходов счетчика и выходом триггера, выход схемы сравнения подключен ко второму входу блока управления, третий вход которого соединен с выходом элемента И, вход элемента аадержки подключен к первому выходу блока управления, а выходко второму входу счетчика, выходы элементов И соединены со входами блока индикации, входы регистра являются адресными входами устройства.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 419984, кл, Cj 11 С 29/00, 1972.

2. Авторское .свидетельство СССР по заявке № 2722147/18-24, кл. Я 11 С 29/00, 26.01.79 (прототип).

° °

Составитель B. Рудаков

Редактор Н. Вушаева Техред С.Мигунова Корректор С. Шекмар

Закав 9779/70 Тираж 656 Подписное

ВНИИПИ Государственного комитета СССР по делам ивобретений и открытий

113035, Москва, Ж-35, Раушская наб., a. 4/5

Филиал ППП "Патент, г. Ужгород, ул, Проектная, 4