Устройство формирования импульсов

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОИЗ©МУ С ИЛЬСТВУ

Союз Советски

Социалистических

Республик (61) Дополнительное к авт. сеид-ву— (22) Заявлено 03.01.79 (21) 270б903/18-21 (1)М с присоединением заявки И9 .—

Н 03 К 5/01

Гвсударетаеякыв квмятет

СССР

IIo делам язебретекнй я открытма (23) ПриоритетОпубликовано 15.01.81. Ьюллетень N9 2

Дата опубликования описания 17. 01. 81 (53) УДК 821. 374. .5(088.8) (72) Авторы изобретения

A.Í. Дорофеев и Ю.Н. Мохов (71) Заявитель (54) УСТРОЙСТВО ФОРМИРОВАНИЯ ИМПУЛЬСОВ

Изобретение относится к промиаленности средств связи и может быть использовано в схемах управления приборами с зарядовой связью (ПЭС ), например в телевизионных камерах с применением ПЗС. Оно предназначено для преобразования уровня импульсно го напряжения прямоугольной формы малой величины до большой величины (15 и более вольт) для управления ®

ПЗС.

Известно устоойство преобразования уровня "1" импульсного напряжения от 3 В на выходе циФровых микросхем до 15-25 В на затворах ПЗС, 15 содержащее два транзистора разных типов проводимости п-р-и и р-п-р> змиттеры которых присоединены соответственно к отрицательной и положительной шинам, коллекторы соеди- 20 нены и являются выходом устройства, управляющее импульсное напряжение со входа устройства поступает на базы транзисторов через два токоограннчивающих звена, состоящие каждое 25 из соединенных параллельно резистора и конденсатора, причем между базой и эмиттером одного из транзисторов вкл очается дополнительный резистор f1).

Недостатком этого устройства является невысокая частота импульсного напряжения на выходе.

Известно также устройство, содержащее входной транзистор, база которого соединена с шиной входных сигналов через токоограничивающее звено, состоящее из соединенных параллельно резистора и конденсатора, два переключающих транзистора разных типов проводимости, ьмиттеры которых соединены с положительной и отрицательной шинами источника питания, коллекторы соединены с одним выводом резистора обратной связи, а базы соединены через аналогичные токоограничивающие звенья с коллектором входного транзисто-. ра (2).

Недостаток этого устройства— повышенное потребление энергии от источника питания.

Цель изобретения — уменьшение потре иения энергии и увеличение частоты следования формируемых импульсов.

Указанная цель достигается тем, что в известное устройство, ссдер" жащее входной транзистор, база которого соединена с шиной входных

797058 сигналов через токоограничивающее звено, состоящее из соединенных параллельно резистора и -конденсатора, два переключающих транзистора разных типов проводимости, эмиттеры которых соединены с положительной и отрицательной шинами первого источника питания, коллекторы — с одним выводом резистора обратной связи, а базы соединены через аналогич-. ные токоограничивающие звенья с кол" лектором входного транзистора, вве» ден дополнительный транзистор обратного по отношению к входному транзистору типа проводимости, дополнительный конденсатор и выходной каскад, причем коллектор дополнительного транзистора соединен с коллектором входного транзистора,эмиттером соединенного с шиной второго источника питания, эмиттер дополнительного транзистора подключен к шине третьего источника питания, а база соединена непосредственно с другим выводом резистора обратной связи и подключена через дополнительный конденсатор к шине входных сигналов, при этом коллекторы переключающихся транзисторов подсоедииены к шине выходных сигналов через выходной каскад, который ссдержит два.транзистора разйого типа проводимости, эмиттеры которых соединены с шинами источника питания, базы через токоограничивающие звенья подключены к входной, а коллекторы к выходной шине каскада.

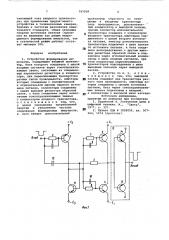

На фиг. 1 представлена принципиальная схема устройства формирования импульсов; на фиг. 2 — схема выходного каскада устройства, вариант; на фиг. 3 — схема выходного каскада устройства, вариант; на фиг. 4диаграмма импульсных напряжений устройства.

Устройство (фиг. 1) содержит входной р-и-р транзистор 1, база которого соединена со входом устройства через токоограничивающее звено, состоящее из соединенных параллельно резистора 2 и конденсатора

3, два переключающих транзистора

4 и 5 разных типов проводимости, эми тер транзистора 4 соединен с отрицательной шиной первого источника питания, а транзистора 5 — с положительной шиной этого источника питания Е(, коллекторы соединены с одним выводом резистора 6 обратной связи, а базы соединены через аналогичные токоограничивающие звенья, состоящие из резисторов 7 и 8, и конденсаторов 9 и 10, с коллектором входного транзистора 1. Коллектор дополнительного транзистора 11 соединен с коллектором входного транзистора 1, эмиттер которого соединен с положительной шиной ис точника питания Е, база допол5 t0

SS

d0

65 нительного транзистора соединена с другим выводом резистора 6 обратной связи, эмиттер соединен с отрицательной шиной источника пита ния Е, конденсатор 12 включен между базой дополнительного транзисто- . ра 11 и входом устройства. Выходной каскад 13 соединен с коллекторами переключающих транзисторов 4 и 5, а его выход является выходом устройства. Отрицательная шина источника питания Е соединяется с положительными шинами источников питания Е и Е > и с корпусом. Практически величина напряжения источника питания E составляет от +1,5 до +2В.

Если в качестве источника Е использовать источник питания +5B цифровых микросхем, то между базой и эмиттером входного транзистора необходимо включить дополнительный резистор. Если для управления устройством используются цифровые элементы "отрицательной логики", то источник питания Л не нужен. В этом слу.чае эмиттер входного транзистора сое— диняется с положительной шиной источника питания Е3.

С целью сокращения числа источников питания, вместо источников питания Е и Е> а также вместо источни-. ка питания выходного каскада можно применить один общий источник.

Выходной каскад может быть построен, например, по схеме симметричного эмиттерного повторителя на транзисторах 14 и 15 разных типов проводимости (фиг. 1), коллекторы ко— торых присоединены к соответствующим шинам источника питания, а эмиттеры соединены и являются выходом устройства. Базы транзисторов 14 и

15 соединены между собой и соединены с коллекторами переключающих транзисторов 4 и 5. Такой выходной кас- . кад не инвертирует входной сигнал.

Выходной каскад может выполнять инверсию входного сигнала (фиг.2)..

Схема этого выходного каскада полностью аналогична каскаду переключающих транзисторов 4 и 5 (фиг. 1).

Выходной каскад может быть построен по более сложной схеме при помощи транзисторов 18-21 (фиг. 3).

На соединенных вместе коллекторах транзисторов 18 и 19 образуется выходное импульсное напряжение прямоугольной формы, инвертированное по отношению ко входному напряжению. На коллекторах транзисторов

20 и 21 образуется неинвертированное выходное импульсное напряжение.

Существование на выходах одного устройства как инвертированного, так и неинвертированного выходных импульсных напряжений позволяет сократить число устройств почти в два раза при управлении однострочным

ПЗС датчиком иэображения.

797058

Устройство можно без каких-либо изменений использовать совместно с ПЗС, выполненными как на основе полупроводника и-типа проводимости, так и полупроводника р-типа. Но. в устройстве, предназначенном преимущественно для работы ПЗС на полупроводнике р-типа, целесообразно изменить по сравнению с фиг. 1 проводимости транзисторов и шины источников питания на обратные.

Любой транзистор может быть выполнен по схеме составного транзистора (схема Дарлингтона). Это обеспечивает более высокую энергоэкономичность устройства, в особенности в преимущественно статическом режиме его работы.

При массовом производстве устройства целесообразно изготовление элементов его схемы на одном общем кристалле или на небольшом числе кристаллов полупроводника. В этом случае в устройстве вместо резисторов можно применить полевые транзисторы с изолированным затвором. В качестве конденсаторов могут быть использованы МДП-конденсаторы или емкости закрытых р-и переходов.

Устройство работае следующим образом. импульсное напряжение прямоугольной формы (фиг. 4, ocb A) подается с выхода цифровой микросхемы на вход устройства и, воздействуя через токоограничивающее звено (резистор

2 и конденсатор 3), в момент времени t, включает транзистор 1. Скачок напряжения от переднего фронта этого импульсного напряжения также ггоступает через конденсатор 12 на базу транзистора 11 и дифференцируется.

Поэтому на базе п-р-и транзистора

11 образуется отрицательный экспоненциально-спадающий импульс (фиг.4, ось Б, кривая а), который в момент времени t закрывает этот транзистор на время своей длительности 7:1 .

Промежуток времени С, oïðåäåëÿåòñÿ временем превышения по абсолютной величине этим импульсом порогового напряжения тока базы Uä транзистора -11. При одновременном включении транзистора 1 .и выключении тран» зистора 11 их коллекторы в момент времени с4 приниМают потенциал, близкий потенциалу положительной шины источника питания Е (фиг. 4, ось В). Возникающий на коллекторах этих транзисторов положительный перепад напряжения по своей величине близок к напряжению второго и третьего источников питания (E> F Eg).

Этот скачок напряжения поступает через два токоограничивающих звена (резисторы 7 и 8 и коьденсаторы

9 и 10) на базы п-р-п транзистора

4 и р-п-р транзистора 5, причем транзистор 4 включается, а транзистор 5 выключается. Благодаря высокочастотности транзисторов устройства, а также благодаря существованию в токоограничивающих звецьях ускоряющих конденсаторов 9 и 10 переклю чение транзисторов 4 и 5 происходит почти непосредственно в момент времени t<, Таким образом, в этот момент времени коллекторы транзисторов 4 и 5 скачком гриобретают потен1,, циал, близкий потенциалу отрицательной шины источника питания E (ôèã.4, ось r), который воспроизводится при, помощи выходного каскада на выходе устройства (фиг. 4, ось Д). Отрицательный перепад напряжения, образовавшийся в момент времени t на кол4 лекторах транзисторов 4 и 5, через резистор 6 обратной связи воздействует на базу транзистора 11 (фиг.4

-ось Б, кривая б)и, спадая экспоненЩ циально; подтверждает с некоторой задержкой Т по времени выключенное состояние этого транзистора. Промежуток времени определяется относительно порогового напряже2 ния Urr на базе транзистора 11. Величина резистора 6 и конденсатора

12 выбирается таким образом, чтобы величина Cg была меньше t,1 . В момент времени t потенциал входа скачком принимает уровень "1" и закрывает транзистор 1. На базе транзистора 11 этому положительному скачку напряжения соответствует экспоненциальноспадающий импульс (фиг.4, ось Б, кривая в), который открывает транзистор 11 в момент времени

В этот момент времени на коллекторах транзисторов 1 и 11 образуется отрицательный перепад напряжения (фиг.4i ось B), который через токоограничи40 вающие звенья воздействует на базы транзисторов 4 и 5. Поэтому транзистор 4 закрывается, а транзистор 5 открывается, т.е. потенциал коллекторов этих транзисторов в момент вре4 мени tn скачком приобретает потенциал, блйзкий потенциалу положительной шины питания источниi i E (фиг. 4, ось Г). Этот уровень воспроизводится на выходе устройства (фиг. 5, ось Д) при помощи выходного каскада. Положительный скачок напряжения посредством резистора 6 обратной связи подтверждает включенное состояние транзистора 11 с некоторым запозданием Т (фиг. 4, ось

Б, кривая г), но до прекращения действия продифференцированного.перепада входного напряжения (фиг. 4, ось Б, кривая в). Уровень на выходе подде"живается до момента времени ф() t>, когда начинается следующий период функционирования устройства.

В предлагаемом устройстве уменьшение потребляемой энергии достигается главным образом за счет почти полного исключения статической сос797058

8ход иод фиг.1 тавляющей тока входного транзистора; при применении предла аемого устройства в телевизионных камерах, близких к частотам разложения. вещательного стандарта, общая экономия энергии источника питания (принимая во внимание как режим непрерывного формирования импульсов, так и статический режйм работы} составит минимум 30%.

Формула изобретения

1. Устройство формирования импульсов, содержащее входной транзистор, база которого соединена с шиной входных сигналов через токоограничивающее звено, состоящее из соединенных параллельно резистора и конденсатора, два переключающих транзистора разных типов проводимости, эмиттеры которых соединены с положительной и отрицательной шинами первого источника питания, коллекторы соединены с одним выводом резистора обратной связи, а базы соединены через аналогичные токоограничивающие звенья с коллектором входного транзистора, о т л и ч а ю щ е е с я тем, что, с целью уменьшения потребляемой энергии и увеличения частоты следования формируемых импульсов, в него введен дополнительный транзистор обратного по отношению к входному транзистору типа проводимости, дополнительный конденсатор и выходной каскад, причем коллектор дополнительного транзистора соединен с коллектором входного транзистора,эмиттером соединенного с шиной второго источника питания, эмиттер дополнительного транзистора подключен к шине третьего источника питания, а база соединена непосредственно с другим выводом резистора обратной связи и подключена через дополнительный конденсатор к шине входных сигналов, при этом коллекторы переключающихся !

3 транзисторов подсоединены к шине выходных сигналов через выходной каскад.

2. Устройство по п. 1, о т л ич а ю щ е е с я тем, что, выходной

2О каскад содержит два транзистора разного типа проводимости, эмиттеры которых соединены с шинами источника питания, базы через токоограничивающие звенья подключены к входной, а коллекторы к выходной шине каскада.

Источники информации, принятые во внимание при экспертизе

1. Будинский Я. Логические цепи в цифровой технике. N., "Связь", 1977, с. 337.

® 2. Патент CIIIA 9 3858059, кл. 307264, 1974 (прототип).