Управляемый делитель частоты сле-дования импульсов

Иллюстрации

Показать всеРеферат

1 лФт зн р j . Р бн(>ли о т t к в h1 Ь,"

О Й

Союз Советскик

Социалистических

Республик

ИСАНИЕ

ИЗОБРЕТЕНИЯ

<>797076

Н АВТОРСКОМУ СВИ ЕТЕЛЬСТВУ (61.) Дополнительное к авт. саид-ву(53)М. Кл.

Н 03 К 23/ООУ

6 06 Г 7/39 (Щ3аявлвио 17.10.,77 (21) 2537890/18-21 с крисюедииеииеав заявки N9—

Государственный комитет

СССР по делам изобретений и открытий (23) Г1риаритет—

Опубликовано: 15.0181. Бк ллетеиь М (53) УДК 621.374 (088.8) Дата опубликования описания 180181

1 (72) Авторы изобретения

Т.Г.Галамай, В.Б.Дудыкевич и И.И.Уланова (7t) Заявитель, (54) УПРАВЛЯЕМЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ СЛЕДОВАНИЯ

ИМПУЛЬСОВ

Изобретение относится к вычислительной. технике и может быть использовано в устройствах автоматики и вычислительной техники.

Известен. управляемый делитель частоты, содержащий счетчик импульсов, элементы ИЛИ, линию задержки, коммутатор и сумматор (1).

Недостатком этого устройства является неравномерность следования выходных импульсов, что ограничивает точность работы устройства.

Наиболее близким к предлагаемому является управляемый делитель частоты импульсов, содержащий входной преобразователь импульсов, выход которого подключен ко входу первого счетчика, импульсов, блок элементов совПадения со сборкой на выходЕ, первая и вторая группа входов которого подключены соответственно к выходам первого и второго счетчиков импульсов (2).

Недостатком этого устройства также является неравномерность следования импульсов выходного напряжения, что ограничивает точность работы устройства.

Цель изобретения — повышение точ-. ности работы устройства.

Поставленная цель достигается тем,что в управляемый делитель частоты следования импульсов, содержащий первый и второй счетчики импульсов, выходы которых подключены соответственно к первой и второй группам входов блока элементов совпадения со сборкой на выходе, и входной формирователь импульсов, первый вход кото10 рого соединен со входом устройства., а выход подключен ко входу первого счетчика импульсов, введены соединеннае последовательно регулируемая ли,ния задержки, входы;которой; подклю15 чены к выходам второго счетчика импульсов, н дешифратор, утравляющий вход которого соединен с выходом блока элементов совпадения со сборкой на выходе, а выход — со вторым

20 входом входного формирователя импульсов.

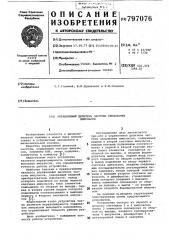

На чертеже пр иведена структурная электрическая схема предлагаемого устройства.

25 Устройство состоит из первого и второго счетчиков 1 и 2 импульсов, блока 3 элементов совпадения со сборкой на выходе, входного преобразователя 4 импульсов, дешифратора 5 и регулируемой линии 6 задержки.

797076

При.этом информационные входы счетчика 1 соединены с информационными входами устройства., а выходы— соответственно с управляющими входами блока З,.сигнальные входы которого подключены соответственно к выходам второго счетчика 2, один вход которого соединен с выходом устройства и выходом входного преобразователя

4, первый вход которого подключен ко входу устройства, входы дешифратора 5 соединены с выходами счетчика

1, выходы дешифратора 5 — co входами управления регулируемой линии б задержки входы которой подключены к выходу блока 3, а выход линии задержки соединен со вторым входом входного преобразователя импульсов.

На вход устройства подается сигнал с частотой F>„ . На информационные входы счетчика 1 поступает код

N> . Входной преобразователь 4 может быть выполнен как схема сложения, схема вычитания или комбинированная схема (схема сложения-вычитания).

Рассмотрим материал выполнения преобразователя 4 как схемы сложения.

Устройство работает следующим образом.

В счетчике 1 формируется дополнительный код и =й „-МЧ, который управляет элементамй совпадения блока 3. Дополнительный код у получается на обратных выходах разрядов счетчика, если из кода, N>, занесенного в счетчике 1, вычесть единицу. В случаях выполнения преобразователя

4 как схемы вычитания или комбинированной схемы, управление элементами совпадения блока 3 осуществляется прямым кодом N

Импульсы входной частоты F>< поступают на вход преобразователя 4 и далее с era выхода на вход счетчика 2. На выходе блока 3 при поступлении импульсов на вхед счетчика

2 формируется последовательность импульсов с частотой F, равной

Fsbw "ч вых(w ч (1) где ГВь,Х вЂ” частота импульсов, поступающих с выхода преобразователя 4. на вход счетчика 2.

Импульсы частоты Fg. через линию б задержки поступают на второй вход преобразователя 4, частота F>b< на выходе которого равна сумме Рвх и

F> поступающих на его входы

Ъ 1

BblX ВХ (2) Из выражений (1) и (2) г

SbIX Вх q вх (K„; (3) где Nyy .А Йщ

Задаваясь определенными значениями йч, т.е. К „, можно получить необходимое деление число-импульсного сигнала на постоянный коэффициент согласно выражению (3) . Счетчик 2 может одновременно использоваться и для подсчета количества импульсов выходной поделенной частоты F,„ .

При использовании выходов разрядов счетчика 2 в качестве выходов устройства значения частоты F вью

f5 может изменяться в пределах от ("вх м) /Ng < "вх! ч

В зависимости от значения управляющего кода в счетчике 1 через дешифратор 5 регулируется время за20 держки линии 6.,,что позволяет регулировать расстановку импульсов выходной частоты, т.е. уменьшить неравномерность следования импульсов выходной частоты. Это приводит к

25 повышению точности предлагаемого устройства по сравнению с известными.

При динамическом диапазоне изменения коэффициента деления, равного

10, и емкости счетчика — 10,погрешность от неравномерности следования импульсов выходной частоты в предлагаемом устройстве не превышает 2 единиц младшего разряда.

Формула изобретения

Управляемый делитель частоты следования импульсов, содержащий первый и второй счетчики импульсов, выходы которых подключены соответст4О венно к первой и второй группам входов бло".а элементов совпадения со сборкой на выходе,и входной формирователь импульсов, первый вход которого соединен со входом уст45 ройства, а выход подключен ко входу первого счетчика импульсов, о т л ич а ю шийся тем, что, с целью повышения точности работы, в него введены соединенные последовательно регулируемая линия задержки, входы

50 которой подключены к выходам второго счетчика импульсов, и дешифратор, управляющий вход которого соединен с выходом блока, элементов совпадения со сборкой на выходе, а выход

55со вторым входом входного формирователя импульсов.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР

d0 9 308523, кл. G 06 F 7/52, 1969 ° .

2.Авторское свидетельство СССР

Ч 418857, кл. G 06 F 7/39, 1972. ч/076

Ъи

Составитель О.Митрофанов

Редактор Ю.Петрушко Техред H.Ковалева корректор M.äåì÷èê

Заказ 9801/78, Тираж 999 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5

Филиал ППП"Патент", r.Óæroðîä,óë.Ïðîåêòíàÿ,4